# A Simplification of a Real-Time Verification Problem

Indranil Saha<sup>1</sup> Janardan Misra<sup>2</sup>

Suman  $Roy^3$

<sup>1</sup> Comp. Sc. Dept., Uni. of California, Los Angeles, CA 90095, USA. Email:indranil@cs.ucla.edu

<sup>2</sup> HTS Research, BG Road, Bangalore 560076, India.

Email: janmishra@gmail.com

<sup>3</sup> SETLABS, Infosys Tech. Ltd., #44 Electronic City, Bangalore 560100, India. Email: suman\_roy@infosys.com

November 5, 2018

#### Abstract

We revisit the problem of real-time verification with dense time dynamics using timeout and calendar based models, originally proposed by Dutertre and Sorea, and simplify this to a finite state verification problem. To overcome the complexity of verification of real-time systems with dense time dynamics, Dutertre and Sorea, proposed timeout and calender based transition systems to model the behavior of real-time systems and verified safety properties using k-induction in association with bounded model checking. In this work, we introduce a specification formalism for these models in terms of Timed Transition Diagrams and capture their behavior in terms of semantics of Timed Transition Systems. Further, we discuss a technique, which reduces the problem of verification of qualitative temporal properties on infinite state space of (a large fragment of) these timeout and calender based transition systems into that on clockless finite state models through a two-step process comprising of digitization and canonical finitary reduction. This technique enables us to verify safety invariants for real-time systems using finite state model-checking avoiding the complexity of infinite state (bounded) model checking and scale up models without applying techniques from induction based proof methodology. Moreover, we can verify liveness properties for real-time systems, which is not possible by using induction with infinite state model checkers. We present examples of Fischer's Protocol, Train-Gate Controller, and TTA start-up algorithm to illustrate how such an approach can be efficiently used for verifying safety, liveness, and timeliness properties specified in LTL using finite state model checkers like SAL-smc and Spin. We also demonstrate how advanced modeling concepts like inter-process scheduling, priorities, interrupts, urgent and committed location can be specified as extensions of the proposed specification formalism, that can be subjected to the proposed two step reduction technique for verification purposes.

Keywords: Real-Time Systems; Timeout and Calendar Model; Clockless Model; Finite State Verification

### Contents

|          |     | roduction                                       |

|----------|-----|-------------------------------------------------|

|          | 1.1 | Related Work                                    |

| <b>2</b> | Tin | neout and Calendar-based Real-Time Models       |

|          | 2.1 | Timed Automata                                  |

|          | 2.2 | Timeout Transition Model                        |

|          | 2.3 | Calendar Transition Model                       |

|          | 2.4 | Limitation of Existing Formalisms               |

| 3        | For | malization of Timeout and Calendar based Models |

|          | 3.1 | Timeout based Timed Transition Model            |

|          |     | 3.1.1 Syntax                                    |

|          |     | 3.1.2 Semantics                                 |

|   | <ul> <li>3.2 Calendar Based Timed Transition Model</li></ul>                                                                                                                                      | 9<br>9<br>9<br>10                                                      |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 4 | Examples<br>4.1 Fisher's Mutual Exclusion Protocol                                                                                                                                                | <b>11</b><br>11<br>11                                                  |

| 5 | Verification Results for Digitization5.1Timed Sequences5.2Digitization5.3Digitization of Timeout and Calendar based Transition Systems5.4Linear Temporal Logic5.5An Integral Verification Problem | <ol> <li>13</li> <li>14</li> <li>14</li> <li>15</li> <li>15</li> </ol> |

| 6 | Clockless Modeling         6.1       Timeout based Models: Clockless Modeling                                                                                                                     | <b>15</b><br>16<br>16<br>17<br>17<br>17<br>18<br>19                    |

| 7 |                                                                                                                                                                                                   | <b>21</b><br>21<br>24<br>24                                            |

| 8 | Extension of Timeout and Calendar based Models8.1Modeling Inter-Process Scheduling8.2Modeling Priorities and Interrupts8.3Modeling Urgent Location and Committed Location                         | 25<br>27<br>28<br>28                                                   |

| 9 | Conclusion and Further Work                                                                                                                                                                       | 29                                                                     |

# 1 Introduction

Real-time systems are an important class of mission critical systems, which have been well studied for their design, implementation, performance and verification. Modeling and verification of real-time systems in dense time domain is an important problem area that evoked lot of research interest in the recent past. Because of the fact that the state space of real-time systems with continuous dynamics is uncountable, modeling and verification of them is rather difficult, in particular using explicit state model checkers. Many formalisms have been used to model and verify real-time systems. Notable among them are different kinds of timed transition models [Alu99, HMP92b], timed process algebras [BeJ91, DaS95, NiS94], and real-time logics [AlH91, BMN00].

In [DuS04a], Dutertre and Sorea, considered verification of a train-gate controller modeled as a timed automata. Though they could specify the timed automata model in terms of state transition system in infinite state model checker SAL [MOR04], it however did not to produce the desired results. In particular, the clock variables occurring in timed automata would be updated in arbitrarily small increments leading to infinite trajectories during which the discrete state remained idle. This made proof of **safety** properties by k-induction quite hard, and sometimes impossible. The fact that the traditional semantics of timed automata allows several time steps to occur in succession is an obstacle in proving properties by k-induction.

To address this problem the same authors proposed timeout and calender based transition models, [DuS04a, DuS04b], originally from discrete event simulation, to represent the behavior of timed triggered systems with dense time dynamics. These models are amenable to general-purpose verification environments, like SAL in which state machines and their compositions can be specified. In this modeling approach, each process in the system has a timeout that holds the time when the next discrete transition of the process would happen, and there is a global data structure, called *calendar*, which stores future events (message delivery) and the time points at which these events are scheduled to occur. During the time progress transition, time is advanced to the minimum of timeouts of processes, or to the least time point at which a message will be delivered in future, whichever is less. Further, Dutertre and Sorea, used this calendar based model along with timeouts for individual processes to model TTA startup protocol in SAL [DuS04b]. Using bounded model checking, they proved a safety property by k induction. However, these proofs using k-induction do not usually scale up well; a safety property often cannot be proved at induction depth 1. Sometimes safety property for the TTA startup algorithm with only 2 nodes has been proved by using 3 additional lemmas. A verification diagram based abstraction method proposed in [Rus00] has been used to prove the same safety (invariant) property for scaled up models (upto 10 nodes). However, liveness properties still remain beyond the scope of this approach.

While only safety properties can be verified on these models with dense time, discrete time modeling of the same can help verify liveness and timeliness properties, and also help scale up proofs for safety properties. It turns out that verification of a real-time system in dense domain is equivalent to verifying the system in discrete domain if both the behavior of the system captured by the model and the properties considered are digitizable [HMP92a]. It can be shown that if the timeout updates are not restricted to (0, 1)-intervals, then similar to the timed transition system of [HMP92a] (refer to theorem 2 therein), transition systems for timeout and calendar based models also give rise to digitizable behaviors (computations). Also verification of qualitative properties like safety and liveness, in discrete time domain is equivalent to verifying these properties in dense time domain (refer to proposition 1 in [HMP92a]).

Techniques like bounded model checking [MRS03, DuS04a] can be useful for detecting bugs during the verification process even in discrete domain, where one systematically searches for counterexamples of length bounded by some integer k. The bound k is increased until a bug is found, or some pre-computed completeness threshold is reached. Unfortunately, it is usually very expensive to compute completeness thresholds. Also these thresholds may be too large to effectively explore the bounded search space. Additionally, such completeness thresholds may be absent for many infinite-state systems. A finite state modeling of the system can help exploring the state space much easily. Examples of finite state model checkers are Spin [Hol93], SAL-smc solvers [DuS04a] etc. Spin has been used to finitely model TTA startup algorithm using a clockless calendar based model [SMR07]. In terms of scalability, finite state verification of TTA in Spin is almost comparable to the verification of TTA based on verification diagram oriented abstraction method [DuS04b]. Moreover, liveness properties can be verified in this framework.

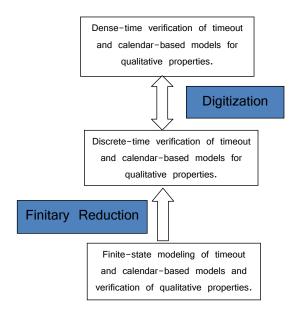

In this work, we aim to carry out a finite state modeling and verification on timeout and calendar models without continuously varying clocks. As there are drawbacks of those models earlier proposed from the point of view of design considerations, like absence of formally defined syntactic models and associated semantics, we slightly deviate from them. We consider the specification framework of timed transition diagrams and extend it to formalize timeout and calendar based models as timeout and calendar based transition diagrams and their behavior in terms of semantics of transition systems. The benefits that we derive from using this formalization are many-fold. Our framework of timeout transition diagrams inherits most of the properties of classical timed transition system introduced in [HMP92b]. Most of the techniques, like digitization that can be applied to these timed transition systems are applicable to our formalization also. This can be also used to model time-triggered systems and reason about them. Finally we use this formal modeling framework to reduce continuous time verification problem to discrete time finite state verification, albeit under some restrictions. Towards that, we use a two step technique comprising of digitization and finitary reduction (a schematic diagram of this technique is shown in Figure 1). We show that the computations of timeout and calendar models are digitizable provided the timeout increments are not restricted to (0, 1)-interval. As LTL properties are qualitative and hence, are digitizable, verification of LTL properties on timeout and calendar models in dense time is equivalent to that in discrete time. The next step is to reduce this problem into an equivalent finite state verification problem. We could not directly proceed to extract finite state models from dense time models, since the latter models are inherently infinite (and dense) and hence it is not possible to render them finite even by bounding the variables. Also note that such a modeling cannot be directly subjected to finite state verification since for timeout and calendar based models, global time and timeouts always increase. Nonetheless, we propose a finitary reduction technique which effectively reduces the infinite state timeout

Figure 1: A two-step verification process

and calendar based transition systems with discrete dynamics into a finite state transition system. We achieve this by using a clockless modeling technique which effectively strips the model of the global clock and keeps track of the relative updation of timeouts, and restricts the values of variables/timeout updates to bounded domains. We demonstrate by examples, how such a modeling approach can be efficiently used for verifying safety, liveness, and timeliness properties using finite state model checkers, SAL-smc and Spin. We also highlight the scalability of such models for verification purposes by comparing the performance of such models under dense time and finite state modeling. A preliminary version of this paper appeared in [SMR07].

The remainder of the paper is organized as follows. In the next section, we briefly discuss the timeout and calendar based modeling as presented in [DuS04a, DuS04b]. In Section 3, we present the formalization of these models in terms of timeout transition diagrams and their behavior in terms of the semantics of transition systems. We discuss the technique of digitization in Section 5 and present our first step of reduction of dense-time verification problem to integral time verification problem. In Section 6, we describe the finitary reduction technique and subsequently, formalize it in terms of clockless modeling. We present experimental results in Section 7. A few extensions of our framework are described in Section 8 followed by concluding remarks in Section 9.

### 1.1 Related Work

There have been earlier attempts to model and verify time-triggered systems using extensions of finite state model checkers, e.g., Spin. Spin [Hol93] is a tool for automatically model checking distributed systems, but it does not allow explicit representation for time. There are mainly two attempts for extending Spin with time. Real-time extension of Spin (RT-Spin [TrC96]) is one such attempt, that makes use of timed Buchi automata [AlD94] with real-valued clocks as a modeling framework. However, this formalism is incompatible with the partial order reduction which is supported by Spin. Another is the work on DT-Spin [BoD98a, BoD98b], which allows one to quantify (discrete) time elapsed between events, by specifying the time slice in which they occur. DT-Spin is compatible with the partial order reduction and has been used to verify industrial protocols, like, AFDX Frame management protocol [SaR06a] and TTCAN [SaR06b]. Nonetheless, systems with asynchronous communication with bounded delays between components cannot be modeled directly by using the kind of asynchronous channels that Spin provides, since there is no explicit provision to capture message transmission delays. A possible way is to model each channel as a separate process with delay as a state variable. In [BoD98a], the channels in the example of PAR protocol have been implemented in the same way. But for systems with relatively large number of components and high degree of connectivity among them, modeling channels in this way is difficult, and hence state space explosion becomes an unavoidable problem.

The concept of clockless modeling has been introduced in [Pik05]. In that Pike builds on the work

of [DuS04a] and proposes a new formalism called Synchronizing Timeout Automata (STA) to reduce the induction depth k required for k-induction. He introduces a clockless semantics for STA so that the resulting transition system does not involve a clock. STA in effect, describes the overall system architecture in terms of timeout transition system introduced in [DuS04a]. A closer analysis of the SAL model for the example of Train-Gate Controller presented in [Pik05], reveals that the considered model is not deadlock free. This is because the model fails to specify the timeout updation rules precisely for the transitions leading to a waiting state. When a process is waiting for an external signal, its timeout should be set to a value greater than the current value of the timeouts of the senders of the expected signal. This kind of modeling errors could possibly be eliminated with a suitable modeling framework such as the one proposed in this paper.

To our knowledge, the first attempt to convert TA to untimed TA is taken up in [AlD94]. Building upon these, in [ChH04] the authors discuss how a special kind of model for specifications written in Duration Calculus (DC) [CHR91] can be generated in which, DC formulas would correspond to regular expressions over a state of special symbols. The models for DC formulas contain discrete states and digitization of continuous states, thereby enabling reasoning in a single framework of both discrete and continuous time. Applying discretization on the continuous component of real-time systems, these models could be further translated into Promela models for verification experiments using SPIN.

# 2 Timeout and Calendar-based Real-Time Models

In this section we briefly discuss the timed automata [AlD94], timeout, and calendar-based models introduced earlier in [DuS04b].

### 2.1 Timed Automata

Timed automata (TA) was introduced by Alur et al. in [AlD94] as a clock based model for specifying real-time system designs. TA is widely used for modeling and verification of real-time systems. Many tools are available for analyzing timed automata e.g., UPPAL [BDL04], Kronos [Bozga], Rabbit [BLN03]. For further details on TA, the reader is referred to [AlD94].

### 2.2 Timeout Transition Model

Dutertre and Sorea [DuS04a, DuS04b] used timeout based modeling to formally verify real-time systems using k-induction in SAL model checker. A Timeout Transition Model (TTM), which is a model of the combined system behavior, contains a finite set of timeouts and a global clock variable t. Timeouts define the time points when discrete transitions will be enabled in the future. The clock variable t keeps track of the current time. In practice a typical real-time system may contain a number of processes. Every process is associated with one timeout which records the future point of time when the next discrete transition for the process is scheduled to occur. Transitions in this model are classified into two types: time progress transitions and discrete transition occurs when t is equal to the minimum valued timeout(s). Discrete transition occurs when t is equal to the minimum value, one of them is randomly chosen and corresponding discrete transition occurs updating the value of the timeout for the selected process. Timeout based modeling approach is suited to model systems where the processes is a rendezvous one.

### 2.3 Calendar Transition Model

Interprocess communication delay during message transfers cannot be modeled using timeout based modeling because delays are beyond the control of individual processes. Addition of an *event calendar*, a globally shared data structure, is proposed as a convenient way to model such delays [DuS04b]. This model is called Calendar Transition Model (CTM). A *calendar* is a set of bounded size of the form  $C = \{\langle e_1, t_1 \rangle, \ldots, \langle e_r, t_r \rangle\}$ , where each event  $e_i$  is associated with the time point  $t_i$  when it is scheduled to occur. There is fundamental difference between a clock and a calendar in the sense that while the former measures the time elapse since its last reset, the latter stores expected delivery delays for all undelivered messages. Asynchronous communication with bounded delay can be easily modeled by using calendar as a global data structure. When a message is transmitted by a process, it is added to the calendar as an event  $e_i$  to occur at time  $t_i$ , where  $t_i$  denotes the expected delivery time for the message. On receiving the message, the event is removed from the calendar. Thus at any state, the calendar C can be seen as a set of messages that have been sent but are yet to be received with corresponding expected delivery delays.

### 2.4 Limitation of Existing Formalisms

Timed automata is one of the most frequently used formalism for specifying real-time system designs. However as it turns out that for systems with asynchronous communication with bounded delays between components TA does not offer any efficient means of specification. Two possible choices have been considered in literature. First choice is to use state variables for encoding the behavior of asynchronous channels however without any explicit provision to capture message transmission delays. Second choice is to model each channel as a separate TA with delay as a state variable. However with relatively large number of components and high degree of connectivity among them, modeling channels in this way is difficult, and state space explosion becomes an unavoidable problem. UPPAAL [BDL04], which can model TA, has the same problem when it is used to model asynchronous communications with bounded delays - every channel has to be modeled as a separate TA capturing the message transmission delays.

On the other hand, although TTM and CTM are expressive enough to capture a range of behaviors associated with time triggered systems including asynchronous communication delays, they however have two specific design limitations:

- These models are not well suited for actual system design purpose since they describe the behavior of the combined system without (explicitly) specifying the design of the modular components.

- Absence of formally defined syntactic design models corresponding to these transitions systems would demand that additional correctness measures are put in place because for verification purposes actual designs models need to be (manually) interpreted and translated into these transition systems as per the underlying system dynamics and on discovering an error during verification, such errors need to comprehended by a designer, and subsequently, translated back into his design for a remedial action.

Keeping in view of such limitations in the existing specification formalisms, we will next define and elaborate using examples a new timeout based formalism, which can effectively overcome these barriers.

# 3 Formalization of Timeout and Calendar based Models

In [HMP92b] an abstract model of timed transition system was proposed which could represent a wide variety of behaviors of the timed execution of concurrent processes. In this section we adapt and extend the Timed Transition System (TTS) described therein to represent timeout and calendar based models. Further we describe their associated semantics in terms of state transition systems.

#### 3.1 Timeout based Timed Transition Model

#### 3.1.1 Syntax

A Timeout based Model (ToM) is represented as

$$P: \{\theta\}[P_1||P_2||\dots||P_n].$$

Each process  $P_i$  is a sequential non-deterministic process having  $\tau_i$  as its local timeout and  $\mathcal{X}_i$  as a set of local timing variables. Local timing variables are used for determining the relative delay between events. A shared variable  $\{t\}$  represents the global clock. The operator "||" denotes parallel composition. The formula  $\theta$ , called the *data pre-condition* of P, restricts the initial values of variables in

$$\mathcal{U} = \{t\} \cup \mathcal{T} \cup \mathcal{X} \cup Var,$$

where the set of all timeouts is  $\mathcal{T} = \{\tau_1, \tau_2, \ldots, \tau_n\}$ , and  $\mathcal{X} = \bigcup_i \mathcal{X}_i$ . The set  $Var = (G \cup L_1 \cup L_2 \cup \ldots \cup L_n)$  is the set of other state variables. The variables in G are globally shared among all the processes while  $L_i$  contains variables local to process  $P_i$ . Let  $f^{Var}$  be the set of computable functions on Var.

Each process  $P_i$  is represented using a *timeout transition diagram* (TTD), which is a finite directed graph with a set of nodes  $Loc_i = \{l_0^i, l_1^i, \ldots, l_{m_i}^i\}$ , called *locations*. The entry location is  $l_0^i$ . There are two

kinds of edges in the graph of a process  $P_i$ : Timeout edges and Synchronous Communication edges. Edge definitions involve an enabling condition or guard  $\rho$ , which is a boolean-valued function or a predicate.

Timeout Edges: A timeout edge  $(l_j^i, \rho \Rightarrow \langle \tau_i := update_i, \gamma, f \rangle, l_k^i)$  in the graph of the process  $P_i$  is represented as

$$l_{i}^{i} \stackrel{\rho \Rightarrow \langle \tau_{i} := update_{i}, \gamma, f \rangle}{\longrightarrow} l_{k}^{i},$$

where  $update_i$  specifies the way timeout  $\tau_i$  is to be updated on taking a transition on the edge when the guard  $\rho$  evaluates to **true**.  $\gamma \subseteq \mathcal{X}_i$  specifies the local timing variables which capture value of the clock t while taking transition on the edge. This value may be used during future transitions while estimating relative delay w.r.t. this transition.  $f \in f^{Var}$  manipulates the state variables in  $G \cup L_i$ .

$update_i$  is defined using the rule:

$$update_i = k_1 \mid k_2 \mid \infty \mid \max(\mathcal{M})$$

where  $l + z \prec k_1 \prec' m + z'$  for  $\prec, \prec' \in \{<, \leq\}$  and  $k_2 \succ l + z$  for  $\succ \in \{>, \geq\}$ ; z, z' := t | w and  $l, m \in \mathbb{N}$  are non negative integer constants specifying the lower and upper limits for a timeout increment interval<sup>1</sup>, and  $w \in \mathcal{X}_i$  is a local timing variable. The variable z makes such an interval relative to the occurrence of specific events.  $\mathcal{M}$  is the set of all the integer constants that are used to define the upper limit of different timeouts for different processes in the system. max( $\mathcal{M}$ ) returns the maximum of all the integers in  $\mathcal{M}$ .

Constraints on  $k_1, k_2$  specify how new value of timeout  $\tau_i$  should be determined based upon the current value of the clock t and/or w, which would have captured the value of t in some earlier transition. Setting a timeout to  $\infty$  tends to capture the requirement of indefinite waiting for an external signal/event. The selection of the timeout value using  $\max(\mathcal{M})$  is used to capture the situation where the next discrete transition of a process may happen at any time in the future, for example, the process may be in a sleeping mode and can wake up at any future point of time.

Synchronous Communication Edges: Rendezvous communication between a pair of processes  $(P_s, P_r)$  is represented by having an edge pair  $(e_s, e_r)$  s.t.  $e_s \in P_s$  and  $e_r \in P_r$  and

$$e_s: l_j^s \xrightarrow{\rho \Rightarrow \langle ch!m, \tau_s:=update_s, \gamma, g \rangle} l_k^s$$

$$e_r: l_j^r \xrightarrow{True \Rightarrow \langle ch?\bar{m}, \tau_i:=update_r, \gamma', h \rangle} l_k^r$$

where ch is the channel name,  $m \in L_i$  is the message sent, and  $\overline{m} \in L_r$  the message received, and  $g, h \in f^{Var}$  are the computable functions.

#### 3.1.2 Semantics

With a given ToM

$$P: \{\theta\}[P_1||P_2||\dots||P_n]$$

we associate the following transition system  $S_P = (\mathcal{V}, \Sigma, \Sigma_0, \Gamma)$ , referred to as *timeout based clocked* transition system (TCTS) where,

- 1.  $\mathcal{V} = \mathcal{U} \cup \{\pi_1, \ldots, \pi_n\}$ . Each control variable  $\pi_i$  ranges over the set  $Loc_i \cup \{\bot\}$ . The value of  $\pi_i$  indicates the location of the control for the process  $P_i$  and it is  $\bot$  (undefined) before the start of the process.

- 2.  $\Sigma$  is the set of states. Every state  $\sigma \in \Sigma$  is an interpretation of  $\mathcal{V}$ , that is, it assigns values to clock variable t, every timeout variable in  $\mathcal{T}$ , timing variables in  $\mathcal{X}$ , state variables in Var, and control variables  $\pi_1, \ldots, \pi_n$ , in their respective domains. For  $x \in \mathcal{V}$ , let  $\sigma(x)$  denote its value in state  $\sigma$ .

- 3.  $\Sigma_0 \subseteq \Sigma$  is the set of initial states such that for every  $\sigma_0 \in \Sigma_0$ ,  $\theta$  is true in  $\sigma_0$  and  $\sigma_0(\pi_i) = \bot$  for each process  $P_i$ .

- 4.  $\Gamma = \Gamma_e \cup \Gamma_+ \cup \Gamma_0 \cup \Gamma_{syn\_comm}$  is the set of transitions. Every transition  $\nu \in \Gamma$  is a binary relation on  $\Sigma$  defined further as follows:

<sup>&</sup>lt;sup>1</sup>This interval mimics the delay interval marking an edge in the original timed transition diagrams

Entry Transitions:  $\Gamma_e$ , the set of entry transitions contains an *entry transition*  $\nu_e^i$  for every process  $P_i$ . In particular,  $\forall \sigma_0 \in \Sigma_0$ ,

$$\nu_e^i \equiv (\sigma_0, \sigma') \in \Gamma_e \Leftrightarrow \begin{cases} 1. & \forall x \in \mathcal{U} : \ \sigma'(x) = \sigma_0(x) \\ 2. & \forall \tau \in \mathcal{T} : \ \sigma'(t) \le \sigma'(\tau) \\ 3. & \sigma_0(\pi_i) = \bot \text{ and } \sigma'(\pi_i) = l_0^i \end{cases}$$

Time Progress Transition: The first kind of edges  $\nu_+ \in \Gamma_+$  are those where the global clock is increased to the minimum of all timeouts. In particular,

$$\nu_{+} \equiv (\sigma, \sigma') \in \Gamma_{+} \Leftrightarrow \begin{cases} 1. & \sigma(t) < \min\{\sigma(\mathcal{T})\} \\ 2. & \forall \tau \in \mathcal{T} : \sigma'(\tau) = \sigma(\tau) \\ 3. & \forall x \in \mathcal{X} : \sigma'(x) = \sigma(x) \\ 4. & \forall i : \sigma'(\pi_{i}) = \sigma(\pi_{i}) \\ 5. & \sigma'(t) = \min\{\sigma(\mathcal{T})\} \end{cases}$$

Timeout Increment Transition: For the second kind of edges  $\nu_0^i \in \Gamma_0$  the global clock equals the minimum of timeouts. Also if an edge in the TTD for process  $P_i$  connects source location  $l_j^i$  to target location  $l_k^i$  and is labeled by the instruction  $\rho \Rightarrow \langle \tau_i := update_i, \gamma, f \rangle$ , then

$$\nu_{0}^{i} \equiv (\sigma, \sigma') \in \Gamma_{0} \Leftrightarrow \begin{cases} 1. \quad \rho \text{ holds in } \sigma \\ 2. \quad \sigma'(t) = \sigma(t) \\ 3. \quad \text{If } \sigma(\tau_{i}) = \sigma(t) \\ \quad \text{then } \sigma'(\tau_{i}) = update_{i} > \sigma(\tau_{i}) \\ else \, \sigma'(\tau_{i}) = \sigma(\tau_{i}) \\ 4. \quad \forall x \in \gamma : \ \sigma'(x) = \sigma(t) \text{ and} \\ \forall x \in \mathcal{X} \setminus \gamma : \ \sigma'(x) = \sigma(x) \\ 5. \quad \forall v \in G \cup L_{i} : \sigma'(v) = f(\sigma(v)) \text{ and} \\ \forall v \in Var \setminus (G \cup L_{i}) : \ \sigma'(v) = \sigma(v) \\ 6. \quad \sigma(\pi_{i}) = l_{j}^{i} \text{ and } \sigma'(\pi_{i}) = l_{k}^{i} \end{cases}$$

If  $update_i = k_1$  s.t.  $l + z \prec k_1 \prec m + z'$ , then  $update_i$  arbitrarily selects a value  $\delta$  such that  $[l + \sigma(z) \prec \delta \prec m + \sigma(z')] \land [\delta > \sigma(\tau_i)]$  and returns  $\delta$ . If  $update_i = k_2$  s.t.  $k_2 \succ l + z$ , then  $update_i$  arbitrarily selects a value  $\delta$  such that  $[\delta \succ l + \sigma(z)] \land [\delta > \sigma(\tau_i)]$  and returns  $\delta$ . If  $update_i = \infty$ ,  $update_i$  returns the largest possible constant defined as per the design of the system. If  $update_i = \max(\mathcal{M})$ ,  $update_i$  nondeterministically selects any integer  $\delta$  in [0, M + 1], where M is the maximum of all the integers in  $\mathcal{M}$  returned by  $\max(\mathcal{M})$ . The local timing variables in  $\gamma \subseteq \mathcal{X}_i$  for process  $P_i$  are assigned the current value of global clock on timeout increment transition, while the other local timing variables in the system retain their old values before this transition. The variables in  $\gamma$  are thus used to capture the delay between two events.

Synchronous Communication: For a pair of processes  $P_s, P_r$  having synchronous communication edges  $(e_s, e_r)$  as defined before,  $\nu_{syn\_comm}^{sr} \in \Gamma_{syn\_comm}$  exists such that:

$$\nu_{syn\_comm}^{sr} \equiv (\sigma, \sigma') \in \Gamma_{syn\_comm} \Leftrightarrow \begin{cases} 1. \quad \rho \text{ holds in } \sigma \\ 2. \quad \sigma'(t) = \sigma(t) \\ 3. \quad \sigma'(\tau_s) = update_s > \sigma(\tau_s) \text{ and} \\ \sigma'(\tau_r) = update_r > \sigma(\tau_r) \\ 4. \quad \forall x \in (\gamma \cup \gamma') : \ \sigma'(x) = \sigma(t) \text{ and} \\ \forall x \in \mathcal{X} \setminus (\gamma \cup \gamma') : \ \sigma'(x) = \sigma(x) \\ 5. \quad \sigma'(\bar{m}) = \sigma(m) \\ 6. \quad \forall v \in G \cup L_s : \sigma'(v) = g(\sigma(v)) \\ \forall v \in G \cup L_r : \sigma'(v) = h(\sigma(v)) \\ \forall v \in Var \setminus (G \cup L_s \cup L_r) : \ \sigma'(v) = \sigma(v) \\ 7. \quad \sigma(\pi_s) = l_s^s, \sigma(\pi_r) = l_r^r \text{ and} \\ \sigma'(\pi_s) = l_s^s, \sigma'(\pi_r) = l_r^r \end{cases}$$

This semantic model defines the set of possible computations of the ToM P as a (possibly infinite) set of state sequences  $\xi : \sigma_0 \to \sigma_1 \to \ldots$ , which starts with some initial state  $\sigma_0$  in  $\Sigma_0$  and follows with consecutive edges in  $\Gamma$ , *i.e.*,  $\forall i.(\sigma_i, \sigma_{i+1}) \in \Gamma$ . Let  $[S_P]$  be the set of all these computations of a ToM Pas defined by its TCTS  $S_P$ .

### 3.2 Calendar Based Timed Transition Model

### 3.2.1 Syntax

Next we capture bounded message transfer delay associated with an asynchronous communication. Towards that the ToM is extended with a calendar data structure. A calendar is a linear list of bounded size, where each element of the list contains the following information: message, sender\_id, receiver\_id, and expected\_delivery\_time. Assuming C to denote the calendar array, a globally shared object, we set

$$\mathcal{U} = \{t\} \cup \mathcal{T} \cup \mathcal{X} \cup Var \cup \mathcal{C}$$

Sending a message in a TTD of process  $P_i$  is represented using the following edge:

$$l_{j}^{i} \stackrel{\rho \Rightarrow \langle send(m,i,\Omega), \tau_{i} := update_{i}, \gamma, f \rangle}{\longrightarrow} l_{k}^{i}$$

where  $\Omega \subseteq R \times \Lambda$ ,  $R \subseteq \{1, 2, ..., n\}$  is the index set for the processes and  $\Lambda$  is the set of expected message delays. send(...) specifies that a message m is to be sent to each of the processes  $P_r$  with expected delivery time of  $\lambda_r$  where  $(r, \lambda_r) \in \Omega$ . On taking a transition on this edge an entry  $\{m, i, r, \lambda_r\}$  is added to C for each  $(r, \lambda_r) \in \Omega$ .

Receiving of the corresponding message is represented in the TTD for each of the processes  $P_r, \forall r \in R$ using the following edge:

$$l_{j}^{r} \xrightarrow{True \Rightarrow \langle receive(m,i,r), \tau_{r} := update_{r}, \gamma, g \rangle} l_{k}^{r}$$

where receive(...) specifies that a message m sent by process  $P_i$  is to be received by the process  $P_r$ . On taking a transition on this edge, the entry  $\{m, i, r, \lambda_r\}$  is deleted from C.

#### 3.2.2 Semantics

Given a calendar C, we assume that the set of delays for all undelivered messages at any state  $\sigma$  can be found using the function

$$\Delta: \sigma(\mathcal{C}) \to 2^{\mathbb{N}}$$

Again  $\Gamma = \Gamma_e \cup \Gamma_+ \cup \Gamma_0 \cup \Gamma_{syn\_comm} \cup \Gamma_{asyn\_comm}$  is the set of transitions in the calendar based clocked transition system (CCTS). Both  $\Gamma_e$  (set of Entry Transition) and  $\Gamma_{syn\_comm}$  (Synchronous Communication) are same as in TCTS defined earlier. The definitions for the edges in Time Progress Transition ( $\Gamma_+$ ) and those for Timeout Increment Transition ( $\Gamma_0$ ) are modified using calendar C as follows:

Time Progress Transition: The first kind of edges  $\nu_+$  are those where the global clock is increased to the minimum of all the timeouts and message delays. In particular,

$$\nu_{+} \equiv (\sigma, \sigma') \in \Gamma_{+} \Leftrightarrow \begin{cases} 1. & \sigma(t) < \min\{\sigma(\mathcal{T}) \cup \Delta(\sigma(\mathcal{C}))\} \\ 2. & \forall \tau \in \mathcal{T} : \sigma'(\tau) = \sigma(\tau) \\ 3. & \forall x \in \mathcal{X} \cup Var : \sigma'(x) = \sigma(x) \\ 4. & \forall i : \sigma'(\pi_{i}) = \sigma(\pi_{i}) \\ 5. & \sigma'(t) = \min\{\sigma(\mathcal{T}) \cup \Delta(\sigma(\mathcal{C}))\} \end{cases}$$

Timeout Increment Transition: For the second kind of edges  $\nu_0^i$  where global clock equals the minimum of all the timeouts and message delays, we have: if an edge in the TTD of process  $P_i$  connects source location  $l_i^i$  to target location  $l_k^i$  and is labeled by the instruction  $\rho \Rightarrow \langle \tau_i := update_i, \gamma, f \rangle$ , then

$$\nu_{0}^{i} \equiv (\sigma, \sigma') \in \Gamma_{0} \Leftrightarrow \begin{cases} 1. \quad \rho \text{ holds in } \sigma \\ 2. \quad \sigma'(t) = \sigma(t) \\ 3. \quad \text{If } [\sigma(t) = \min\{\sigma(\mathcal{T})\}] \land [\sigma(\tau_{i}) = \sigma(t)] \\ \quad \text{then } \sigma'(\tau_{i}) = update_{i} > \sigma(\tau_{i}) \\ else \, \sigma'(\tau_{i}) = \sigma(\tau_{i}) \\ 4. \quad \forall x \in \gamma : \ \sigma'(x) = \sigma(t) \text{ and} \\ \forall x \in \mathcal{X} \setminus \gamma : \ \sigma'(x) = \sigma(x) \\ 5. \quad \forall v \in G \cup L_{i} : \sigma'(v) = f(\sigma(v)) \text{ and} \\ \forall v \in Var \setminus (G \cup L_{i}) : \ \sigma'(v) = \sigma(v) \\ 6. \quad \sigma(\pi_{i}) = l_{j}^{i} \text{ and } \sigma'(\pi_{i}) = l_{k}^{i} \end{cases}$$

We additionally define new transitions corresponding to send() and receive() to capture asynchronous communication:

Send Transition: If there is an edge in process  $P_i$ , which connects source location  $l_j^i$  to target location  $l_k^i$ and is labeled by the instruction  $\rho \Rightarrow \langle send(m, i, \Omega), \tau_i := update_i, \gamma, f \rangle$ , then we have the corresponding edge  $\nu_{send}^i \in \Gamma_{asyn\_comm}$ , which adds  $|\Omega|$  cells to the calendar array C:

$$\nu_{send}^{i} \equiv (\sigma, \sigma') \Leftrightarrow \begin{cases} 1. \quad \rho \text{ holds in } \sigma \\ 2. \quad \sigma'(t) = \sigma(t) \\ 3. \quad \sigma'(\tau_{i}) = update_{i} > \sigma(\tau_{i}) \\ 4. \quad \forall x \in \gamma : \ \sigma'(x) = \sigma(t) \text{ and} \\ \quad \forall x \in \mathcal{X} \setminus \gamma : \ \sigma'(x) = \sigma(x) \\ 5. \quad \forall v \in G \cup L_{i} : \sigma'(v) = f(\sigma(v)) \text{ and} \\ \quad \forall v \in Var \setminus (G \cup L_{i}) : \ \sigma'(v) = \sigma(v) \\ 6. \quad \forall (r, \lambda_{r}) \in \Omega : \sigma'(\mathcal{C}) := \sigma(\mathcal{C}) \cup \{\text{m, i, r, } \lambda_{r}\} \\ 7. \quad \sigma(\pi_{i}) = l_{i}^{i} \text{ and } \sigma'(\pi_{i}) = l_{k}^{i} \end{cases}$$

Receive Transition: If there is an edge in process  $P_r$ , which connects source location  $l_j^r$  to target location  $l_k^r$  and is labeled by the instruction  $True \Rightarrow \langle receive(m, i, r), \tau_r := update_r, \gamma, g \rangle$ , then we have the corresponding edge  $\nu_{receive}^r \in \Gamma_{asyn\_comm}$ , which deletes the entry  $\{m, i, r, \lambda_r\}$  from the calendar array  $\mathcal{C}$  when the clock t reaches  $\lambda_r$ :

$$\nu_{receive}^{r} \equiv (\sigma, \sigma') \Leftrightarrow \begin{cases} 1. \quad \exists \{m, i, r, \lambda_r\} \in \sigma(\mathcal{C}) \text{ s.t. } \sigma(t) = \lambda_r \\ 2. \quad \sigma'(t) = \sigma(t) \\ 3. \quad \sigma'(\tau_r) = update_r > \sigma(\tau_r) \\ 4. \quad \forall x \in \gamma : \ \sigma'(x) = \sigma(t) \text{ and} \\ \quad \forall x \in \mathcal{X} \setminus \gamma : \ \sigma'(x) = \sigma(x) \\ 5. \quad \forall v \in G \cup L_r : \sigma'(v) = g(\sigma(v)) \text{ and} \\ \quad \forall v \in Var \setminus (G \cup L_r) : \ \sigma'(v) = \sigma(v) \\ 6. \quad \sigma'(\mathcal{C}) := \sigma(\mathcal{C}) \setminus \{m, i, r, \lambda_r\} \\ 7. \quad \sigma(\pi_r) = l_j^r \text{ and } \sigma'(\pi_r) = l_k^r \end{cases}$$

Similar to the case of TCTS, this semantic model also defines the set of possible computations of the calendar based ToM as a (possibly infinite) set of state sequences starting with some initial state in  $\Sigma_0$  and following consecutive edges in  $\Gamma$ . Let  $[S_P]$  be the set of all these computations of a calendar based ToM P as defined by its CCTS  $S_P$ .

**Models for Time:** It remained unspecified as to what would be the underlying model of time for clock, timeouts etc that appear in the definitions of TCTS and CCTS. There are two natural choices for time, the set of non-negative integers  $\mathbb{N}$  (discrete time) or the set of non-negative reals  $\mathbb{R}$  (dense time). Given the model of time as TIME, let  $[S_P]_{TIME}$  be the set of all the computations of a ToM (or calendar based ToM) P as defined by its TCTS (or CCTS)  $S_P$ .

When we consider that the underlying model of time as  $\mathbb{R}$ , we need to add the following non-zenoness condition to ensure effective time progress in the model. There must not be infinitely many time progress (or timeout increment) transitions effective within a finite interval. Formally,

nonzenoness:

$$\forall \xi: \ \sigma_0 \to \sigma_1 \to \ldots \in [S_P]_{\mathbb{R}}, \forall \delta \in \mathbb{R}, \exists i \ge 0, \sigma_i(t) > \delta$$

#### 3.3 Parametric Processes

We consider the case of finite family of processes specified in a parametric way. A completely parametric process family would be specified as

$$\{\theta\}[\{P(i)\}_{i=1}^{i=N}]$$

where  $N \ge 1$  is some finite positive integer and  $\theta = \theta_1 \land \ldots \land \theta_N$  such that  $\theta_i$   $(1 \le i \le N)$  initializes the variables for the *i*<sup>th</sup> copy of the process. Process P(i) could be a TTD or a calender based TTD.

The semantic interpretation of such parametrically specified process family is given by first flattening the specification as

$$\{\theta\}[P(1)||\ldots||P(N)]$$

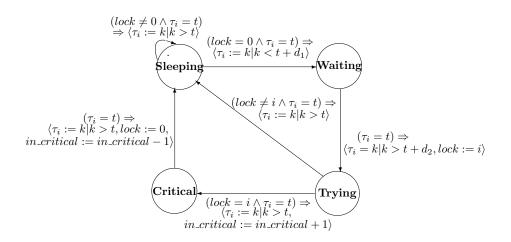

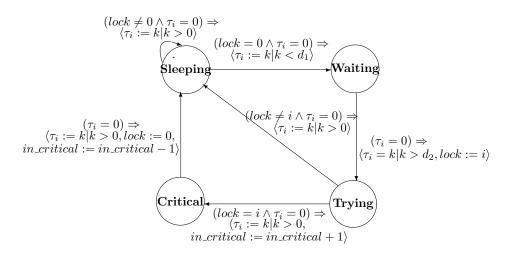

Figure 2: TTD for the  $i^{th}$  process in the Fischer's Protocol

and then applying the semantics presented before as per the case of P(i) being a TTD or a calendar based TTD.

Such parametric specification can be generalized to a homogeneous set of process families as

$$\{\theta\}[\{P(i_1)\}_{i_1=1}^{i_1=N_1}||\dots||\{P(i_l)\}_{i_l=1}^{i_l=N_l}]$$

where  $N_1, \ldots N_l$  are some finite positive integers and  $\theta = \theta_1 \wedge \ldots \wedge \theta_l$  such that  $\theta_i = \theta_{i1} \wedge \ldots \wedge \theta_{iN_i}$ initializes the variables for the  $i^{th}$  process family. The term homogeneous arises because processes in all the process families should uniformly be either TTDs or calender based TTDs. We do not consider the case of hetrogeneous set of process families, where processes across different process families might be different. Similar to the case of a single parametric process family, the generalized process family can be interpreted by flattening the process specification.

### 4 Examples

Following two examples would illustrate the expressiveness and effectiveness of the proposed timeout and calendar based modeling framework.

### 4.1 Fisher's Mutual Exclusion Protocol

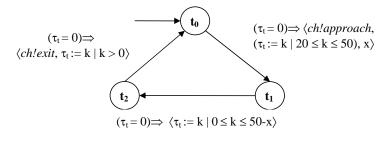

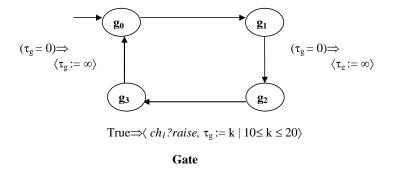

Fischer's protocol is a well studied protocol to ensure mutual exclusion among real time concurrent processes. Let there be *n* processes  $P_1, \ldots, P_n$  trying to access shared resources in a real-time fashion to be discussed later. A process  $P_i$  is initially idle (*Sleeping* state), but at any time, may begin executing the protocol provided the value of a global variable *lock* is 0 and then move to *Wait* state. There it can wait up to maximum of  $d_1$  time units before assigning the value *i* to *lock* and moving to *Trying* state. It may enter the *Critical* section after a delay of at least of  $d_2$  time units provided the value of *lock* is still *i*. Otherwise it has to move to *Sleeping* state. Upon leaving the *Critical* section, it re-initializes *lock* to 0. There is another global variable, *in\_critical*, used to keep count of the number of processes in the critical section. The auto-increment (auto-decrement) of the variable is done before a process enters the *Critical* section (leaves the *Critical* section). Mutual exclusion is ensured if  $d_1 < d_2$ . The timeout-based TTD of the *i*<sup>th</sup> process  $P_i$  executing Fischer's protocol is shown in Figure 2.

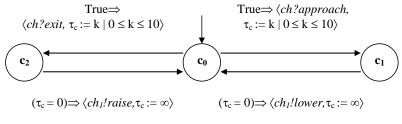

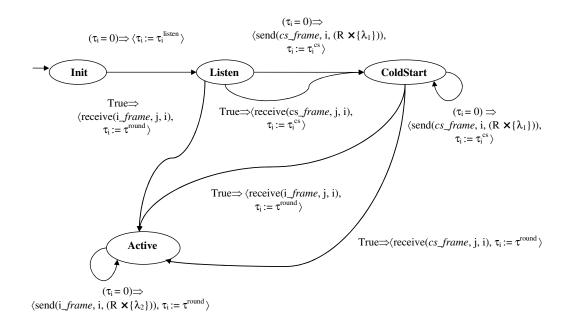

### 4.2 TTA Startup Algorithm

The TTA startup algorithm can be formalized using the calendar based model described above. This algorithm executes on a logical bus meant for safety-critical application in both automotive and aerospace industries. In a normal operation, N processors or nodes share a TTA bus using a TDMA schedule. The goal of the startup algorithm is to bring the system from the power-up state, in which the processors are not synchronized, to the normal operation mode in which all processors are synchronized and follow the same TDMA schedule.

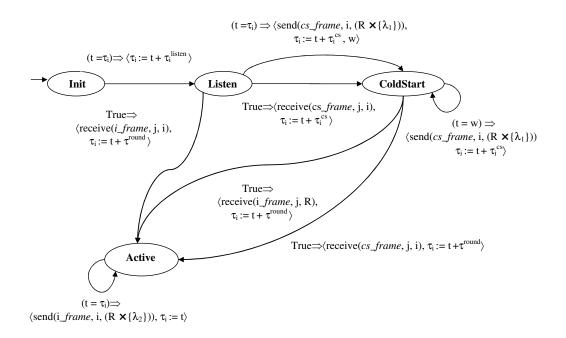

Figure 3: Calendar-based TTD for the  $i^{th}$  node in TTA Startup algorithm

In TTA startup algorithm each node  $i \in \{1..., N\}$  has two unique timeout parameters,  $\tau_i^{listen}$  and  $\tau_i^{cs}$ , for *listen* and *coldstart* states respectively. These are defined as follows:

$$\tau_i^{listen} = 2\tau^{round} + \tau_i^{startup}$$

$$\tau_i^{cs} = \tau^{round} + \tau_i^{startup}$$

where  $\tau^{round}$  represents the TDMA round duration and  $\tau_i^{startup}$  denotes the duration between the start of a TDMA cycle and the time when the slot for node *i* starts. If  $\tau$  denotes the duration of each slot then

$$\tau^{round} = N\tau, \ \tau_i^{startup} = (i-1)\tau$$

When a node is powered-on, it performs some internal initialization, and transits to the *Listen* state. In this state it listens for the unique duration  $\tau_i^{listen}$  to determine if there is a synchronous set of nodes communicating on the medium. The nodes which are in the *Active* state are already synchronized, and periodically transmit i-frames that carry the TDMA cycle structure. If a node in the *Listen* state receives such an i-frame, it adjusts its state to the frame contents and is thus synchronized with the set of already synchronous nodes. If the above does not happen, there are two possibilities. Each node listens for a cold-start message (cs-frame) from another node indicating the beginning of the cold-start sequence; cs-frames are similar to i-frames but carry a protocol state suggested by the sending node. When a node completes the reception of a cs-frame, it enters the *Coldstart* state and resets its local clock to  $\delta_{cs}$  (that is the transmission duration of the cs-frame). Thus, all nodes that received the cs-frame have synchronized local clocks (within system tolerances, including the propagation delay). Each node that receives neither an i-frame nor a cs-frame during the *Listen* phase enters the *Coldstart* state on its listen timeout, resets its local clock to 0 and broadcasts a cs-frame. Thus, after the transmission of the cs-frame ( $\delta_{cs}$  later), the local clock of the sending node is also synchronized to the local clocks of the set of receiving nodes.

Each node in the *coldstart* state waits for reception of another cs-frame or i-frame until its local clock reaches the value of its individual cold-start timeout. If it receives such a frame it synchronizes on its contents and enters the *Active* state; if not, it resets its local clock and again broadcasts a cs-frame. No further collision can occur at this point, because cold-start timeouts have a strict order and that is why no two nodes that caused a collision can collide again. The listen timeout of any node is greater than coldstart timeout of any node. No node which has come in the *Listen* state after the collision cannot move to the *Coldstart* state before the collision is resolved. For further details of startup protocol, we refer the reader to [StP02].

The calendar based TTD of the  $i^{th}$  node is depicted in Figure 3. In TTA startup algorithm, all the communications are asynchronous and hence, message delivery delays, which are finite and specified by

the designer have to be taken into account for correct operation of the protocol. The timeouts  $\tau_i^{listen}$ and  $\tau_i^{cs}$  represent how much time a node spends in *Listen* state and *Coldstart* state respectively, if no external signal is received. The timeout  $\tau^{round}$  denotes the time a node spends in *Active* state before sending its next massage.  $R_i = \{1, \ldots, N\} \setminus \{i\}$  represents the set of nodes except the sender *i* that are required to receive the message in the network. We use  $\lambda_i$ 's to denote the message delivery time for the corresponding send events. In TTA, message delivery times for all the receivers are considered to be the same, and that is why we have considered a single variable  $\lambda_i$  to represent that delay.

# 5 Verification Results for Digitization

In literature the verification problem for real-time systems assumes two descriptions of real-time behavior, implementation I and specification S, and poses the question whether I implements/satisfies S. The implementation language  $\mathcal{L}_I$  describes systems and behavior over time while the specification language  $\mathcal{L}_S$  describes the timing requirements of the system. The verification obligation involves presenting algorithms and/or proof rules that facilitate a formal argument that a particular implementation meets the requirement of a particular system under some particular assumption of semantics of computation and time. Assuming C and T to be mathematical models of computation and time respectively, the real-time verification problem parameterized by  $(C, T, \mathcal{L}_I, \mathcal{L}_S)$  states: does the implementation of the system I, given as an expression of  $\mathcal{L}_I$  meet the specification  $\phi$  given as an expression of  $\mathcal{L}_S$ , with respect to the semantical assumption (C, T), written as

$$I \models^?_{(C,T)} \phi$$

In particular, we would consider two important instances of the real-time verification problem - one with an *integral* model of time and one with a *dense* model of time. In the following, we assume TTS as the implementation language and linear time temporal logic (LTL) as the specification formalism.

#### 5.1 Timed Sequences

We shall adopt discrete trace model (using the terminology from [HMP92a, Bos99]) as a mathematical model of computation. By discrete trace model one can capture the behavior of a system as an infinite sequence of snapshots of the global system state at certain times. We assume our time domain TIMEhas a total ordering  $\leq$  defined on it. We define an observation to be a pair  $(\sigma_i, T_i)$ , where  $\sigma_i$  is a state and  $T_i \in TIME$ . A timed state sequence  $\eta = (\sigma, T)$  is an infinite sequence  $\eta : (\sigma_0, T_0) \to (\sigma_1, T_1) \to$  $(\sigma_2, T_2) \to \cdots$  of observations<sup>2</sup>. Further, the infinite sequence  $T_i \in T$  of time stamps in  $\eta$  satisfy (i) monotonicity:  $T_i \leq T_{i+1}$  for all  $i \geq 0$ , and (ii) progress: time progresses, for all  $T \in TIME$ ,  $T_i \geq T$  for some  $i \geq 0$ .

Now onwards, we shall work with dense-time models when  $TIME = \mathbb{R}$  and integral-time models when  $TIME = \mathbb{N}$ . A timed state sequence under dense-time model will be referred to as *precisely timed* and under integral-time model as *digitally timed*.

Let us denote the set of all timed state sequences over the TIME domain as  $TSS_{TIME}$ . A real-time property is a subset of  $TSS_{TIME}$ . Every real-time system S defines a real-time property, denoted as [S], which is the set of all timed state sequences of S. Also, every real-time specification  $\phi$  defines a real-time property [ $\phi$ ], the set of real-time sequences that satisfy  $\phi$ .

Now let us formulate the real-time verification problem. We say a real-time system S satisfies the specification  $\phi$ , written as

$$S \models_{TIME} \phi$$

if and only if

$$[S]_{TIME} \subseteq [\phi]_{TIME}$$

Consider a dense-time property  $\Pi_{\mathbb{R}} \subseteq TSS_{\mathbb{R}}$ , a set of of timed state sequences over  $\mathbb{R}$ . Its *clock-independent semantics*  $\mathbb{N}(\Pi_{\mathbb{R}})$  is the subset of digitally timed state sequences in  $\Pi_{\mathbb{R}}$ , *i.e.*,  $\mathbb{N}(\Pi_{\mathbb{R}}) = \Pi_{\mathbb{R}} \cap TSS_{\mathbb{N}}$ . In [HMP92a], it is shown that clock-independent semantics is not very adequate for reasoning about dense time. As a remedy of this, another approximate semantics was introduced, which was called *digitization*.

<sup>&</sup>lt;sup>2</sup>Note that any  $\xi \in [S_P]$  (previously defined) essentially defines a timed state sequence. This is because, states in  $\xi$  have implicit representation for time stamps as  $\sigma_0(t), \sigma_1(t), \ldots$ , which are otherwise explicitly present in the definition of  $\eta$  as  $T_0, T_1, \ldots$

The following definitions will be useful for our subsequent discussions. For any timed state sequence  $\eta = (\sigma, T)$ , we introduce it untime operation  $\eta^-$  as its state component  $\sigma$ . Also,  $\eta^i = (\sigma^i, T^i)$ , for  $i \ge 0$ , denotes the timed state sequence that results from  $\eta$  by deleting the first *i* observations (note,  $\eta^0 = \eta$ ).

### 5.2 Digitization

Given  $x \in \mathbb{R}$  and  $\epsilon \in (0, 1]$ , we define  $[x]_{\epsilon} = \lfloor x \rfloor$  if  $x \leq \lfloor x \rfloor + \epsilon$ , otherwise  $[x]_{\epsilon} = \lceil x \rceil^3$ . Given a precisely timed sequence  $\eta = (\sigma, T)$  and  $\epsilon \in (0, 1]$ , we define the  $\epsilon$ -digitization  $[\eta]_{\epsilon} = (\sigma, [T]_{\epsilon})$  of  $\eta$  be the digitally timed sequence

$$(\sigma_0, [T_0]_{\epsilon}) \to (\sigma_1, [T_1]_{\epsilon}) \to \cdots,$$

For any dense-time property  $\Pi$  (a set of timed sequences over dense time) let

$$[\Pi] = \{ [\eta]_{\epsilon} \mid \eta \in \Pi \text{ and } \epsilon \in (0, 1] \},\$$

which is a digitization of  $\Pi$ . We write  $[\eta]$  instead of  $[\{\eta\}]$ .

We state some concepts from [HMP92a]. Let  $\Pi$  be a dense-time property.  $\Pi$  is closed under digitization iff for all  $\eta \in TSS_{\mathbb{R}}, \eta \in \Pi$  implies  $[\eta] \subseteq \Pi$ .  $\Pi$  is closed under inverse digitization iff  $[\eta] \subseteq \Pi$  implies  $\eta \in \Pi$ , for all  $\eta \in TSS_{\mathbb{R}}$ . Finally,  $\Pi$  is digitizable iff it is closed under both digitization and inverse digitization, *i.e.*,  $\eta \in \Pi$  iff  $[\eta] \subseteq \Pi$  for all  $\eta \in TSS_{\mathbb{R}}$ . We state the following important result (see [HMP92a]).

**Fact 5.1** Assume a real-time system S whose dense-time semantics  $[S]_{\mathbb{R}}$  is closed under digitization, and a specification  $\phi$  whose dense-time semantics  $\phi_{\mathbb{R}}$  is closed under inverse digitization. Then in order to prove  $S \models_{\mathbb{R}} \phi$  it suffices to check if  $S \models_{\mathbb{N}} \phi$ .

A dense-time property  $\Pi$  is said to be *qualitative* if  $\eta \in \Pi$  implies  $\eta' \in \Pi$  for all precisely timed sequences  $\eta$  and  $\eta'$  with identical state components (*i.e.*,  $\eta^- = \eta'^-$ ).

Fact 5.2 [HMP92a] Every qualitative property is digitizable.

#### 5.3 Digitization of Timeout and Calendar based Transition Systems

Recall a TCTS is  $S = (\mathcal{V}, \Sigma, \Sigma_0, \Gamma)$  (we drop the subscript P because we assume the ToM P is implicit) where  $\mathcal{V}$  is a set of variables,  $\Sigma$  a set of states,  $\Sigma_0 \subseteq \Sigma$  a set of initial states and  $\Gamma$  a set of transitions. We would like to show that the computations for this transition system are digitizable. Our approach follows [Bos99].

A run of S over a timed state sequence  $\eta : (\sigma_0, T_0) \to (\sigma_1, T_1) \to \cdots$  is a sequence of pairs of S of the form  $\zeta : (\sigma_0, \nu_0) \xrightarrow{T_1} (\sigma_1, \nu_1) \xrightarrow{T_2} \cdots$  where  $\sigma_i$  denotes the state and  $\nu_i$  the mapping of variables in  $\mathcal{U}$  in state  $\sigma_i$  and further, it satisfies the following conditions:

- 1. (initiation:)  $\sigma_0 \in \Sigma_0$  and  $\nu_0(t) = T_0$ ,  $\forall i \ge 0.\nu_0(\pi_i) = \bot$ ,  $t \in \mathcal{V}, \pi_i \in \mathcal{V}$ .

- 2. (consecution:) for  $i \ge 1$  there is an edge  $(\sigma_{i-1}, \sigma_i) \in \Gamma = (\Gamma_e \cup \Gamma_+ \cup \Gamma_0 \cup \Gamma_{syn\_comm})$  such that the following hold:

- if  $(\sigma_0, \sigma_1) \in \Gamma_e$  then  $T_0 = \nu_0(t) \le \nu_1(t) = T_1$  and  $\forall \tau \in \mathcal{T}. \sigma_1(\tau) \ge T_1$ .

- if  $(\sigma_{i-1}, \sigma_i) \in \Gamma_+$  then  $T_{i-1} = \nu_{i-1}(t) < \min\{\sigma_{i-1}(\mathcal{T})\} = \nu_i(t) = T_i$ .

- if  $(\sigma_{i-1}, \sigma_i) \in \Gamma_0$  then  $T_{i-1} = \nu_{i-1}(t) = \nu_i(t) = T_i$ .

- if  $(\sigma_{i-1}, \sigma_i) \in \Gamma_{syn\_comm}$  then  $T_{i-1} = \nu_{i-1}(t) = \nu_i(t) = T_i$ .

- 3. (time progress:) for any real number T there exists an  $i \ge 0$  such that  $T_i > T$ .

We say that  $\eta \in TSS_{\text{TIME}}$  is time-consistent (for S) if S has a run over it. In the sequel we consider only time-consistent behaviors  $\eta \in [S]_{\text{TIME}}$  of S, *i.e.*,  $\eta \in [S]_{\text{TIME}}$  iff there is run over  $\eta$ . If TIME =  $\mathbb{N}$ then we get integral behavior of TCTS. Now it is obvious that time at state  $j \ge 1$  in a given run, is given by  $\nu_j(t) = T_j$ . We define  $\epsilon$ -digitization of the mapping  $\nu_j$  for any variable  $x \in \mathcal{U} \subseteq \mathcal{V}$  as  $\langle \nu_j(x) \rangle_{\epsilon} = [\nu(x)]_{\epsilon}$ .

Given a computation  $\zeta : (\sigma_0, \nu_0) \xrightarrow{T_1} (\sigma_1, \nu_1) \xrightarrow{T_2} \cdots$  its  $\epsilon$ -digitization is the computation  $[\zeta]_{\epsilon} : (\sigma_0, \langle \nu_0 \rangle)_{\epsilon}) \xrightarrow{[T_1]_{\epsilon}} (\sigma_1, \langle \nu_1 \rangle)_{\epsilon} \xrightarrow{[T_2]_{\epsilon}} \cdots$ , where  $\langle \nu_j \rangle_{\epsilon}$  for  $j \ge 1$  are defined above, and  $\langle \nu_0(t) \rangle_{\epsilon} = [T_0]_{\epsilon}$ .

<sup>&</sup>lt;sup>3</sup>where  $|\cdot|$  and  $[\cdot]$  are the floor and ceiling rounding operations on real numbers respectively

Now we need to analyze the extent to which the set of dense-time computations of a TCTS are closed under digitization. Suppose  $\zeta : (\sigma_0, \nu_0) \xrightarrow{T_1} (\sigma_1, \nu_1) \xrightarrow{T_2} \cdots$  is a run of S over  $\eta$ . For digitization,  $[\zeta]_{\epsilon}$ would be a run of S over  $[\eta]_{\epsilon}$ . We have  $\langle \nu_0(t) \rangle_{\epsilon} = [T_0]_{\epsilon}$ . Observe if  $T_{i-1} = T_i$  then  $[T_{i-1}]_{\epsilon} = [T_i]_{\epsilon}$ . When  $T_{i-1} < T_i$ , except for the case of  $0 < (T_i - T_{i-1}) < 1$ , we have  $[T_{i-1}]_{\epsilon} < [T_i]_{\epsilon}$ . So, if there is an edge  $(\sigma_{i-1}, \sigma_i) \in \Gamma$  and  $(T_i = T_{i-1}) \lor (T_i \ge T_{i-1} + 1)$ , there would be an edge  $(\langle \sigma_{i-1} \rangle_{\epsilon}, \langle \sigma_i \rangle_{\epsilon})$  in  $\Gamma$  under  $[\zeta]_{\epsilon}$ . Also we can ensure time progress for  $[\zeta]_{\epsilon}$ . Hence:

**Fact 5.3** The set of dense-time computations of a TCTS are closed under digitization if and only if all timeout increments are at least 1 time unit.

The result above indicates a precise characterization for the digitization for a TCTS. All timeout increments in (0, 1) result into a TCTS, which are not closed under digitization and therefore cannot be model checked for all LTL properties under discrete time dynamics.

A similar argument can be used to show that the dense computations of a (digitizable) calendar based clocked transition system (CCTS) are also closed under digitization.

#### 5.4 Linear Temporal Logic

Let us briefly describe propositional linear temporal logic [Pnu77], more popularly known as LTL. The vocabulary of LTL consist of a set  $\mathcal{P}$  of atomic propositions. The formulas of LTL are built using boolean connectives, next operator  $\bigcirc$  and *until* operator  $\mathcal{U}$  as follows:

$$\phi ::= p |\neg \phi | \phi_1 \land \phi_2 | \bigcirc \phi | \phi_1 \mathcal{U} \phi_2, \quad p \in \mathcal{P}$$

The other temporal operators can be introduced as abbreviations, e.g.,  $F\phi \stackrel{c}{=} True \mathcal{U} \phi, G\phi \stackrel{c}{=} \neg F \neg \phi$ .

The formulas of LTL can be interpreted over timed state sequences whose states are from  $\Sigma$  such that each state in  $\Sigma$  gives rise to an interpretation for propositions in  $\mathcal{P}$ . Let  $\eta = (\sigma, T)$  be a timed state sequence with  $\sigma_i \in \Sigma$  for  $i \geq 0$ . The satisfaction relation  $\eta \models \phi$  is defined inductively as follows:

| $\eta \models p$                         | iff | $\sigma_0 \models p;$                                                            |

|------------------------------------------|-----|----------------------------------------------------------------------------------|

| $\eta \models \neg \phi$                 | iff | $\eta \not\models \phi;$                                                         |

| $\eta \models \phi_1 \land \phi_2$       | iff | $\eta \models \phi_1 \text{ and } \eta \models \phi_2$                           |

| $\eta \models \bigcirc \phi$             | iff | $\eta^1 \models \phi \text{ and } T_1 \ge T_0,$                                  |

| $\eta \models \phi_1 \mathcal{U} \phi_2$ | iff | $\exists i \geq 0. \exists \alpha \in \mathbb{N}. \eta^i \models \phi_2$ , where |

|                                          |     | $T_i \ge T_0 + \alpha$ , and $\forall j.0 \le j < i.\eta^j \models \phi_1$ .     |

For a LTL-formula  $\phi$ , let the set  $[\phi]_{TIME} \subseteq TSS_{\text{TIME}}$  contain all timed state sequences  $\eta$  over the time domain TIME such that  $\eta \models \phi$ . Thus,  $[\phi]_{\mathbb{R}}$  is the analog dense-time property for the formula  $\phi$ . Note that for any specification  $\phi$  expressed in LTL,  $[\phi]_{\mathbb{R}}$  is closed under inverse digitization. To see this consider two timed sequences  $\eta$  and  $\eta'$  with identical state components. Suppose  $\eta \models \phi$ , *i.e.*,  $\eta \in [\phi]_{\mathbb{R}}$ . Now the proof is by induction on the structure of  $\phi$ . At the induction stage, we only consider the case  $\phi = \phi_1 \mathcal{U}\phi_2$ . Now  $\eta \models \phi_1 \mathcal{U}\phi_2$  iff for some  $i \ge 0, \alpha \in \mathbb{N}, \eta^i \models \phi_2$ , where  $T_i \ge T_0 + \alpha$ , and  $\eta^j \models \phi_1$  for all  $0 \le j < i$ . By induction hypothesis, we have  $\eta'^i \models \phi_2$  and  $\eta'^j \models \phi_1$ . Since,  $T'_i \ge T'_0$ , there exists some  $\alpha' \in \mathbb{N}$  such that  $T'_i \ge T'_0 + \alpha'$ . Therefore  $\eta' \models \phi$  and hence  $\eta' \in [\phi]_{\mathbb{R}}$ .

### 5.5 An Integral Verification Problem

We conclude this section with this important observation. Given a TCTS or CCTS S, corresponding to a timeout-based or a calender-based model and a specification formula  $\phi$  in LTL we may check  $S \models_{\mathbb{R}} \phi$  by verifying whether  $S \models_{\mathbb{N}} \phi$ . In the next section we shall try to further simplify this problem.

### 6 Clockless Modeling

A finite state model-checker like Spin [Hol93] uses finite state automata to model the behavior of concurrent processes in distributed systems. The combined execution of a system of asynchronous processes is described as a product of automata each of which models an individual process. The product automaton is finite if the number of processes, message channels, number of messages in a channel, and the range of values for various variables are finite in the automaton for each individual process. Though timeout and calendar based models can be used to efficiently capture dense time semantics without using a continuously varying clock, it is difficult to use these models for finite state model checking, even though we have seen that in most of the cases the verification problem reduces to an integral one thanks to digitization. The difficulty arises from the fact that the value of the global clock t and the values of the timeout variables in  $\mathcal{T}$  diverge and thus are not bounded by a finite domain. Unlike TA there is no provision of resetting the global clock or timeouts in these models, as a result of which the timeout and calendar based models cannot be directly used for finite state model checking.

We propose a finitary reduction technique, which is formalized in terms of clockless modeling and semantics in the next section. This technique effectively reduces the timeout and calendar based transition systems with discrete dynamics into finite state systems, which, in turn, can be expressed and model checked by finite state model checkers. The assumption of discrete time as the underlying model is particularly relevant to cases where we are left with integral verification problem exploiting digitization results.

From the semantics of the timeout based systems it is clear that to implement time progress transition, a special process is required to increase the global clock to the minimum of timeouts, when each of the timeout values is strictly greater than the current value of the clock. A process  $P_i$  waits until its timeout is equal to global clock, and when it is so,  $P_i$  takes the discrete transition and updates its own timeout according to the specified updation rule. We model this special process, which is responsible for time progress transition in such a way that it does not explicitly use the clock variable and prevents the timeout variables from growing infinitely. We call this process as *time\_progress*.

The process time\_progress is implemented as follows. When the global clock is less than all the timeouts no discrete transition is possible in the system. In such a situation, time\_progress finds out the minimum of all the timeouts in  $\mathcal{T}$  and scales down all these timeouts in  $\mathcal{T}$  by this amount. In this way at least one of the timeouts becomes zero. The guards of the processes are defined in such a way that the processes wait until their timeouts become zero. When it happens the process updates its timeout and does other necessary jobs.

If *update* function always increments the timeouts by a finite value then it is guaranteed that the value of a timeout will always be in a finite domain. But in some cases it is possible that a timeout may take any value in the future. In those cases, the value of the timeout is taken as the largest possible value defined by the system. This approach can also be extended for the calendar based models as well.

The discussion above is formalized in terms of "clockless" modeling as below:

#### 6.1 Timeout based Models: Clockless Modeling

#### 6.1.1 Clockless Syntax

In order to capture the effect of finite state reduction in a timeout model, we restrict the set  $\mathcal{U}$  and redefine  $update_i$  as follows:

$$\mathcal{U} = \mathcal{T} \cup \mathcal{X} \cup Var.$$

$update_i^-$  is given by the following rule:

$$update_i^- = k_1 \mid k_2 \mid \infty \mid \max(\mathcal{M}),$$

where  $l - z \prec k_1 \prec' m - z'$  for  $\prec, \prec' \in \{<, \le\}$  and  $k_2 \succ l - z$  for  $\succ \in \{>, \ge\}$ ;  $z, z' := w \mid 0$  and  $l, m \in \mathbb{N}$  are non negative integer constants. For any  $z \in U$  let  $\sigma_i^-(z)$  stand for the value of the variable z in (clockless) state  $\sigma_i^-$ . Note that  $update_i^-$  is different from the update function  $update_i$  for clocked transition system in the sense that this one updates the timeouts in bounded domain.

#### 6.1.2 Clockless Semantics

For clockless modeling of timeout based models we associate a transition system  $S_P^- = (\mathcal{V}^-, \Sigma^-, \Sigma_0^-, \Gamma^-)$ , where  $\mathcal{V}^- = \mathcal{V} \setminus \{t\}$  is a set of variables,  $\Sigma^-$  a set of clockless states,  $\Sigma_0^- \subseteq \Sigma^-$  initial clockless states (defined in an analogous manner as for clocked transition systems) and  $\Gamma^-$  a set of clockless transitions. We remark that given a timeout based model, the set of states  $\Sigma$  for clocked transition system and the set of states  $\Sigma^-$  for clockless transition system are exactly similar modulo the assignment of the global clock variable t. The same is true for initial states too. Note  $\Gamma^- = \Gamma_e^- \cup \Gamma_+^- \cup \Gamma_0^- \cup \Gamma_{syn\_comm}^-$ , while  $\Gamma_e^-$  is identical to  $\Gamma_e$  for clocked transitions, we shall only define Time Progress Transition  $\Gamma_+^-$ , Timeout Increment Transition  $\Gamma_0^-$ , and Synchronous Communication Transition  $\Gamma_{syn\_comm}^-$  by modifying the same for the clocked timeout transition system as defined earlier. Time Progress Transition: The edges  $\nu_+$  are redefined such that all the timeouts are decremented by the minimum of the current timeout values. In particular,

$$\nu_{+} \equiv (\sigma^{-}, \sigma'^{-}) \in \Gamma_{+}^{-} \Leftrightarrow \begin{cases} 1. & \min\{\sigma^{-}(\mathcal{T})\} > 0\\ 2. & \forall \tau \in \mathcal{T} : \sigma'^{-}(\tau) = \sigma^{-}(\tau) - \min\{\sigma^{-}(\mathcal{T})\}\\ 3. & \forall x \in \mathcal{X} \cup Var : \sigma'^{-}(x) = \sigma^{-}(x)\\ 4. & \forall i : \sigma'^{-}(\pi_{i}) = \sigma^{-}(\pi_{i}) \end{cases}$$

Timeout Increment Transition: For the edges  $\nu_0^i$ , if there is an edge in the TTD for process  $P_i$  connecting source location  $l_i^i$  to target location  $l_k^i$  and is labeled by the instruction  $\rho \Rightarrow \langle update_i^-, \gamma, f \rangle$ , then

$$\nu_{0}^{i} \equiv (\sigma^{-}, \sigma'^{-}) \in \Gamma_{0}^{-} \Leftrightarrow \begin{cases} 1. \quad \rho \text{ holds in } \sigma^{-} \\ 2. \quad \mathbf{If } \sigma^{-}(\tau_{i}) = 0 \text{ then} \\ \sigma'^{-}(\tau_{i}) = update_{i}^{-} > 0 \\ \mathbf{else } \sigma'^{-}(\tau_{i}) = \sigma^{-}(\tau_{i}) \\ 3. \quad \forall y \in \gamma : \ \sigma'^{-}(y) = \sigma'^{-}(\tau_{i}) + \sigma^{-}(y) \text{ and} \\ \forall x \in \mathcal{X} \setminus \gamma : \ \sigma'^{-}(x) = \sigma^{-}(x) \\ 4. \quad \forall v \in G \cup L_{i} : \sigma'^{-}(v) = f(\sigma^{-}(v)) \text{ and} \\ \forall v \in Var \setminus (G \cup L_{i}) : \ \sigma'^{-}(v) = \sigma^{-}(v) \\ 5. \quad \sigma^{-}(\pi_{i}) = l_{j}^{i} \text{ and } \sigma'^{-}(\pi_{i}) = l_{k}^{i} \end{cases}$$

Observe that  $update_i^-$  is a slight modification of  $update_i$ . If  $update_i^- = k_1$  s.t.  $l - z \prec k_1 \prec m - z'$ , then  $update_i^-$  arbitrarily selects a value  $\delta$  such that  $l - \sigma^-(z) \prec \delta \prec m - \sigma^-(z')$ . If  $update_i^- = k_2$  s.t.  $k_2 \succ l - z$ , then  $update_i^-$  arbitrarily selects a value  $\delta$  such that  $\delta \succ l - \sigma^-(z)$ , else if  $update_i^- = \infty$ , then it selects the largest possible constant defined by the system and returns  $\delta$ . If  $update_i^- = \max(\mathcal{M})$ ,  $update_i^-$  nondeterministically selects any integer  $\delta$  in [0, M + 1], where M is the maximum of all the integers in  $\mathcal{M}$ . Unlike the local timing variables appearing in  $\gamma$  in a (clocked) ToM, these timing variables incrementally capture the value of next timeout in a clockless ToM. An observant reader can see that the relative delay captured by these local timing variables between events are same in both those models.

Synchronous Communication For a pair of processes  $P_s, P_r$  having edges  $(e_s, e_r)$ :

$$\nu_{syn\_comm}^{sr} \equiv (\sigma^-, \sigma'^-) \in \Gamma_{syn\_comm}^- \Leftrightarrow \begin{cases} 1. \quad \rho \text{ holds in } \sigma^-\\ 2. \quad \sigma'^-(\tau_s) = update_s^- > \sigma^-(\tau_s) \\ \sigma'^-(\tau_r) = update_r^- > \sigma^-(\tau_r) \end{cases}$$

$$3. \quad \forall y \in (\gamma) : \ \sigma'^-(y) = \sigma'^-(\tau_s) + \sigma^-(y), \text{ and} \\ \forall y' \in (\gamma') : \ \sigma'^-(y') = \sigma'^-(\tau_r) + \sigma^-(y') \text{ and} \\ \forall x \in \mathcal{X} \setminus (\gamma \cup \gamma') : \ \sigma'^-(x) = \sigma^-(x) \end{cases}$$

$$4. \quad \sigma'^-(\bar{m}) = \sigma^-(m)$$

$$5. \quad \forall v \in G \cup L_s : \sigma'^-(v) = g(\sigma^-(v)), \text{ and} \\ \forall v \in G \cup L_r : \sigma'^-(v) = h(\sigma^-(v)) \text{ and} \\ \forall v \in Var \setminus (G \cup L_r \cup L_s) : \ \sigma'^-(v) = \sigma^-(v) \end{cases}$$

$$6. \quad \sigma^-(\pi_s) = l_j^s, \sigma^-(\pi_r) = l_j^r \text{ and} \\ \sigma'^-(\pi_s) = l_s^k, \sigma'^-(\pi_r) = l_k^r \end{cases}$$

#### 6.2 Calendar based Models: Clockless Modeling

#### 6.2.1 Clockless Syntax

Similar to the ToM, calendar based models can also be defined in a clockless manner. However we restrict the set  $\mathcal{U}$  to,

$$\mathcal{U} = \mathcal{T} \cup \mathcal{X} \cup Var \cup \mathcal{C},$$

where  $update_i^-$  is defined using same rule as in the case of clockless ToM.

#### 6.2.2 Clockless Semantics

Similar to the clockless ToM, we can define a transition system for clockless calendar based models. Here we need to modify the Time Progress, Timeout Increment, Send, and Receive Transitions as defined earlier for CCTS. Synchronous Communication transition is similar to the one for timeout based model

with clockless semantics.

Time Progress Transition: The first kind of edges  $\nu_+$  are redefined so that all the timeout and calendar delay entries are decremented by the minimum of all timeouts and the message delays in calendar. In particular,

$$\nu_{+} \equiv (\sigma^{-}, \sigma'^{-}) \in \Gamma_{+}^{-} \Leftrightarrow \begin{cases} 1. & \min\{\sigma^{-}(\mathcal{T}) \cup \Delta(\sigma^{-}(\mathcal{C}))\} > 0\\ 2. & \forall \tau \in \mathcal{T} : \ \sigma'^{-}(\tau) = \sigma^{-}(\tau) - \min\{\sigma^{-}(\mathcal{T}) \cup \Delta(\sigma^{-}(\mathcal{C}))\}\\ 3. & \forall \lambda \in \Delta(\sigma^{-}(\mathcal{C})) : \ \sigma'^{-}(\lambda) = \sigma^{-}(\lambda) - \min\{\sigma^{-}(\mathcal{T}) \cup \Delta(\sigma^{-}(\mathcal{C}))\}\\ 4. & \forall x \in \mathcal{X} \cup Var : \ \sigma'^{-}(x) = \sigma^{-}(x)\\ 5. & \forall i : \ \sigma'^{-}(\pi_{i}) = \ \sigma^{-}(\pi_{i}) \end{cases}$$

Timeout Increment Transition: For the second kind of edges  $\nu_0^i$ , if there is an edge in process  $P_i$  connecting source location  $l_j^i$  to target location  $l_k^i$  and is labeled by the instruction  $\rho \Rightarrow \langle \tau_i := update_i^-, \gamma, f \rangle$ , then

$$\nu_{0}^{i} \equiv (\sigma^{-}, \sigma'^{-}) \in \Gamma_{0}^{-} \Leftrightarrow \begin{cases} 1. \quad \rho \text{ holds in } \sigma^{-} \\ 2. \quad \mathbf{If } \min\{\sigma^{-}(\mathcal{T})\} = \sigma^{-}(\tau_{i}) = 0 \\ \quad \mathbf{then } \sigma'^{-}(\tau_{i}) = update_{i}^{-} > 0 \\ \mathbf{else } \sigma'^{-}(\tau_{i}) = \sigma^{-}(\tau_{i}) \\ 3. \quad \forall y \in \gamma : \ \sigma'^{-}(y) = \sigma'^{-}(\tau_{i}) + \sigma^{-}(y) \text{ and} \\ \forall x \in \mathcal{X} \setminus \gamma : \ \sigma'^{-}(x) = \sigma^{-}(x) \\ 4. \quad \forall v \in G \cup L_{i} : \sigma'^{-}(v) = f(\sigma^{-}(v)) \text{ and} \\ \forall v \in Var \setminus (G \cup L_{i}) : \ \sigma'^{-}(v) = \sigma^{-}(v) \\ 5. \quad \sigma^{-}(\pi_{i}) = l_{j}^{i} \text{ and } \sigma'^{-}(\pi_{i}) = l_{k}^{i} \end{cases}$$

Send Transition: If there is an edge in process  $P_i$ , which connects source location  $l_j^i$  to target location  $l_k^i$ and is labeled by the instruction  $\rho \Rightarrow \langle send(m, i, \Omega, \Lambda), update_i^-, \gamma, f \rangle$ , then we have corresponding edge  $\nu_{send}^i$  which adds  $|\Omega|$  cells to the calendar array C:

$$\nu_{send}^{i} \equiv (\sigma^{-}, \sigma'^{-}) \Leftrightarrow \begin{cases} 1. \quad \rho \text{ holds in } \sigma^{-} \\ 2. \quad \text{If } \min\{\sigma^{-}(\mathcal{T})\} = \sigma^{-}(\tau_{i}) = 0 \\ \quad \text{then } \sigma'^{-}(\tau_{i}) = update_{i}^{-} > 0 \\ \text{else } \sigma'^{-}(\tau_{i}) = \sigma^{-}(\tau_{i}) \\ 4. \quad \forall y \in \gamma : \sigma'^{-}(y) = \sigma'^{-}(\tau_{i}) + \sigma^{-}(y) \text{ and} \\ \forall x \in \mathcal{X} \setminus \gamma : \sigma'^{-}(x) = \sigma^{-}(x) \\ 5. \quad \forall v \in G \cup L_{i} : \sigma'^{-}(v) = f(\sigma^{-}(v)) \text{ and} \\ \forall v \in Var \setminus (G \cup L_{i}) : \sigma'^{-}(v) = \sigma^{-}(v) \\ 6. \quad \forall (r, \lambda_{r}) \in \Omega : \sigma'^{-}(\mathcal{C}) := \sigma^{-}(\mathcal{C}) + \{\text{m, i, r, } \lambda_{r}\} \\ 7. \quad \sigma^{-}(\pi_{i}) = l_{i}^{i} \text{ and } \sigma'^{-}(\pi_{i}) = l_{k}^{i} \end{cases}$$

**Receive Transition**: If there is an edge in process  $P_r$ , which connects source location  $l_j^r$  to target location  $l_k^r$  and is labeled by the instruction  $True \Rightarrow \langle receive(m, i, r), \gamma, f \rangle$ , then we have corresponding edge  $\nu_{receive}^r$  which deletes the cell containing  $\{m, i, r, \lambda_r\}$  from the calendar array C: