#### ANDREI RIMSA ÁLVARES

## PRACTICAL DYNAMIC RECONSTRUCTION OF CONTROL FLOW GRAPHS

Dissertation presented to the Graduate Program in Computer Science of the Universidade Federal de Minas Gerais, Instituto de Ciências Exatas, Departamento de Ciência da Computação. in partial fulfillment of the requirements for the degree of Doctor in Computer Science.

Advisor: Fernando Magno Quintão Pereira Co-Advisor: José Nelson Amaral

> Belo Horizonte November 5, 2020

© 2020, Andrei Rimsa Álvares Todos os direitos reservados.

|       | Álvares, Andrei Rimsa.                                                                                                                                                                                                                                                                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A473p | Practical dynamic reconstruction of control flow graphs [manuscrito] /Andrei Rimsa Álvares. — 2020. xxv, 88 f.; il.; 29cm.                                                                                                                                                                                                                                                          |

|       | Orientador: Fernando Magno Quintão Pereira.<br>Coorientador: José Nelson Amaral.                                                                                                                                                                                                                                                                                                    |

|       | Tese (doutorado) - Universidade Federal de Minas<br>Gerais, Instituto de Ciências Exatas, Departamento<br>de Ciência da Computação.<br>Referências: f. 83-88                                                                                                                                                                                                                        |

|       | 1. Computação – Teses. 2. Compiladores<br>(Programas de computador) – Teses. 3. Linguagem<br>de programação (Computadores) – Teses. 4. Fluxo de<br>dados (Computação) – Teses. I. Pereira, Fernando<br>Magno Quintão. II. Amaral, José Nelson. III.<br>Universidade Federal de Minas Gerais, Instituto de<br>Ciências Exatas, Departamento de Ciência da<br>Computação. IV. Título. |

CDU 519.6\*33(043)

Ficha catalográfica elaborada pela bibliotecária Irénquer Vismeg Lucas Cruz CRB 6ª Região nº 819.

#### UNIVERSIDADE FEDERAL DE MINAS GERAIS INSTITUTO DE CIÊNCIAS EXATAS PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

#### FOLHA DE APROVAÇÃO

#### Practical Dynamic Reconstruction of Control Flow Graphs

#### ANDREI RIMSA ÁLVARES

Tese defendida e aprovada pela banca examinadora constituída pelos Senhores:

Europhi M Q Bruin PROF. FERNANDO MAGNO QUINTÃO PEREIRA - Orientador Departamento de Ciência da Computação - UFMG

PROF. JOSÉ NELSON AMARAL Department of Computing Science - University of Alberta

Joi Eduardo Moreira IBM Research - IBM

Rodolfo Azvedo Prof. Rodolfo Jardim de Azevedo Instituto de Computação - UNICAMP

PROF. LEONÁRIO BARBOSA E OLIVEIRA Departamento de Ciência da Computação - UFMG

Marco Augusto Augusto Menezes Vieira Prof. Marcos Augusto Menezes Vieira Departamento de Ciência da Computação - UFMG

Belo Horizonte, 5 de Novembro de 2020.

To my parents, brothers and wife.

## Acknowledgments

I am thankful...

To my advisor Fernando for taking me as a student earlier in the masters and later in the phd. His friendship and partnership through all these years have been invaluable for my growth as a person, student and professor.

To my co-advisor Nelson for the insights and support through all of this work. His kindness is always with me.

To my friends in the compiler's laboratory for the fruitful discussions on this thesis, computers and life in general. You guys and girls are awesome.

To my fellow professors in the department of computing of CEFET-MG for the pleasant working environment. This made the persuit of this work sustainable in the long run.

To my parents, Frederico and Zilza, for my upbringing. Their unconditional support have been crucial for the accomplishment of every milestone in my life, including this one.

To my brothers, Vitor and Ivan, for being there with me all the time, even afar. This unity is paramount in my life.

And to my wife May for the love and care during the adversities of this path. I love you.

"Life begins at the end of your comfort zone." (Neale Donald Walsch)

## Resumo

A recuperação automática de informações de alto-nível de programas em formato binário é um importante problema estudado em linguagens de programação. Contudo, a maioria das soluções para esse problema são baseadas puramente em abordagens estáticas: técnicas como análise de fluxo de dados ou inferência de tipos são utilizadas para converter os bytes que constituem o executável de volta para o formato de um grafo de fluxo de controle (GFC). Esse trabalho se afasta desse tal modus operandi para mostrar que análises dinâmicas podem ser efetivas e úteis, tanto como uma técnica independente, quanto como uma forma de melhorar a precisão das abordagens estáticas. Os resultados experimentais mostram evidências que completude, ou seja, a habilidade de concluir que todos os caminhos de um GFC foram cobertos, é alcançada em muitas funções de benchmarks de nível industrial. Os experimentos também indicam que informações coletadas dinamicamente melhoram consideravelmente a habilidade de DYNINST, um reconstrutor estático estado-da-arte, de lidar com códigos binários sem símbolos de depuração. Esses resultados foram obtidos com CFGGRIND, um reconstrutor dinâmico de códigos binários, construído sobre a infraestrutura de VALGRIND. Quando aplicado sobre CBENCH, CFGGRIND é 9% mais rápido que CALLGRIND, uma ferramenta de VALGRIND capaz de rastrear alvos de chamadas de funções; e 7% mais rápido em SPEC CPU2017. CFGGRIND recupera GFCs completos em 40% de todos os procedimentos invocados durante a execução padrão de programas em SPEC CPU2017, e 37% em CBENCH. Quando combinado com CFGGRIND, DYNINST encontra 15% mais GFCs para CBENCH e 7% mais GFCs para SPEC CPU2017. Finalmente, CFGGRIND é 7 vezes mais rápido que DCFG, um reconstrutor de GFC desenvolvido pela Intel, e é 1.28 vezes mais rápido que BFTRACE, um reconstrutor usado em pesquisa. CFGGRIND é também mais preciso que essas duas ferramentas. Ele suporta tratamento de sinais de sistema operacional, códigos compartilhados em funções, instruções desalinhadas, programas multi-thread, profiling exato e refinamentos incrementais.

Palavras-chave: Grafo de fluxo de controle, Análise dinâmica, Instrumentação.

## Abstract

The automatic recovery of a program's high-level representation from its binary version is a well-studied problem in programming languages. However, most of the solutions to this problem are based on purely static approaches: techniques such as dataflow analyses or type inference are used to convert the bytes that constitute the executable code back into a control flow graph (CFG). This work departs from such a modus operandi to show that a dynamic analysis can be effective and useful, both as a standalone technique, and as a way to enhance the precision of static approaches. The experimental results provide evidence that completeness, i.e., the ability to conclude that the entire CFG has been discovered, is achievable on many functions that are part of industry-strong benchmarks. Experiments also indicate that dynamic information greatly enhances the ability of DYNINST, a state-of-the-art binary reconstructor, to deal with code stripped of debugging information. These results were obtained with CFGGRIND, a new implementation of a dynamic code reconstructor, built on top of VALGRIND. When applied to CBENCH, CFGGRIND is 9% faster than CALLGRIND, VALGRIND's tool used to track targets of function calls; and 7% faster in SPEC CPU2017. CFGGRIND recovers the complete CFG of 40% of all the procedures invoked during the standard execution of programs in SPEC CPU2017, and 37% in CBENCH. When combined with CFGGRIND, DYNINST finds 15% more CFGs for CBENCH, and 7% more CFGs for SPEC CPU2017. Finally, CFGGRIND is more than 7 times faster than DCFG, a CFG reconstructor from Intel, and 1.28 times faster than BFTRACE, a CFG reconstructor used in research. CFGGRIND is also more precise than these two tools, handling operating system signals, shared code in functions, and unaligned instructions; besides supporting multi-threaded programs, exact profiling and incremental refinements.

Keywords: Control flow graph, Dynamic analysis, Code instrumentation.

# List of Figures

| 2.1          | (a) Example program. (b) CFG after first call with positive argument for $x$ . (c) Refined CFG after second call with negative argument for $x$                                                                         | 10 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1          | (a) Example program with alarm handler. (b) Assembly code for this example. (c) CFG obtained with CFGGRIND. (d) Simplified CFG obtained with DCFG, showing "unknown" node that emerges after signal handling.           | 15 |

| 3.2          | (a) Example program with two distinct calls to function add. (b) Assembly code with a tail call optimization for this example. (c) CFGs obtained with CFGGRIND for each function. (d) Simplified CFG obtained with DCFG | 10 |

|              | for this program.                                                                                                                                                                                                       | 17 |

| 3.3          | Objdump snippet for functions <u></u>                                                                                                                                                                                   |    |

|              | $[eb86a_{16}, eb86a_{16} + 22_{16}] \cap [eb860_{16}, eb860_{16} + 77_{16}] \neq \emptyset. \dots \dots \dots \dots$                                                                                                    | 19 |

| 3.4          | (a) Hand-crafted example of two overlapping sequences of assembly instruc-<br>tions. (b) CFG obtained with CFGGRIND and BFTRACE. (d) Simplified                                                                         |    |

|              | CFG obtained with DCFG                                                                                                                                                                                                  | 20 |

| $4.1 \\ 4.2$ | (a) Program written in C. (b) static assembly representation of the program.<br>Execution trace of the program in Figure 4.1. Instructions are grouped                                                                  | 23 |

|              | according to Def. 2. Arrows show order in which groups are processed. $\ .$ .                                                                                                                                           | 23 |

| 4.3          | State after processing each of the six groups listed by Figure $4.1$                                                                                                                                                    | 26 |

| 4.4          | The resulting CFGs for functions MAIN (a) and TOTAL (b) in the $mapping$                                                                                                                                                |    |

|              | produced by Algorithm 1. $\ldots$                                                                                                                                                                                       | 29 |

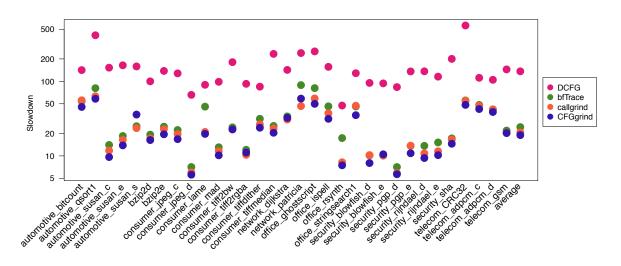

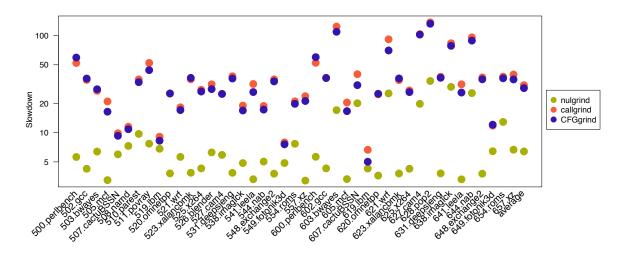

| 5.1          | Slowdown of different tools that reconstruct CFGs relative to the original                                                                                                                                              |    |

|              | program execution without instrumentation for CBENCH                                                                                                                                                                    | 41 |

| 5.2          | Slowdown of builtin tools in VALGRIND and CFGGRIND relative to the orig-                                                                                                                                                |    |

|              | inal program execution without instrumentation for SPEC CPU2017. $\ldots$                                                                                                                                               | 42 |

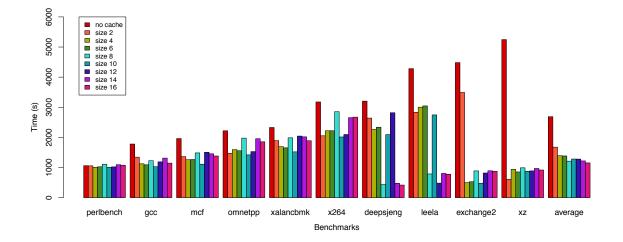

| 5.3          | The impact of cache size on the runtime of CFGGRIND.                                                                                                                                                                    | 43 |

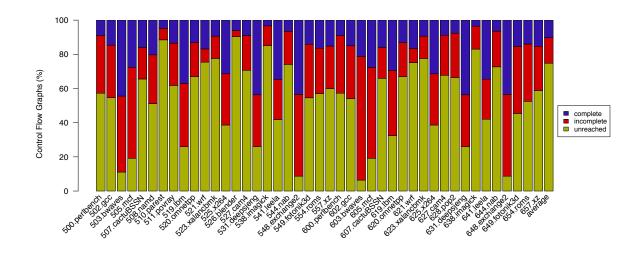

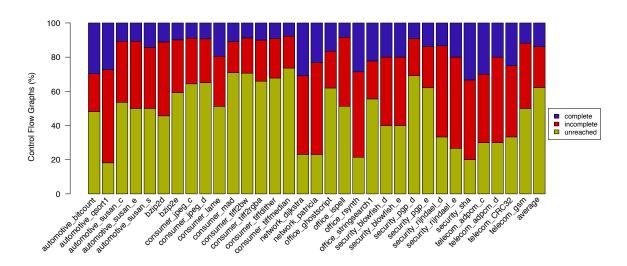

| 5.4 | Number of complete/incomplete/unreached flow graphs for each of the $43$            |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | programs in Spec Cpu2017.                                                           | 45 |

| 5.5 | Number of complete/incomplete/unreached flow graphs for each of the $32$            |    |

|     | programs in CBENCH                                                                  | 45 |

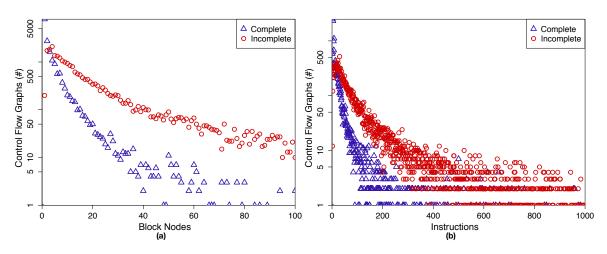

| 5.6 | Relation between the number of complete/incomplete CFGs (y-axis, $\ln$              |    |

|     | scale) per number of blocks (a) and instructions (b) for the SPEC CPU2017 $$        |    |

|     | benchmark. X-axis shows number of blocks (a) and instructions (b)                   | 46 |

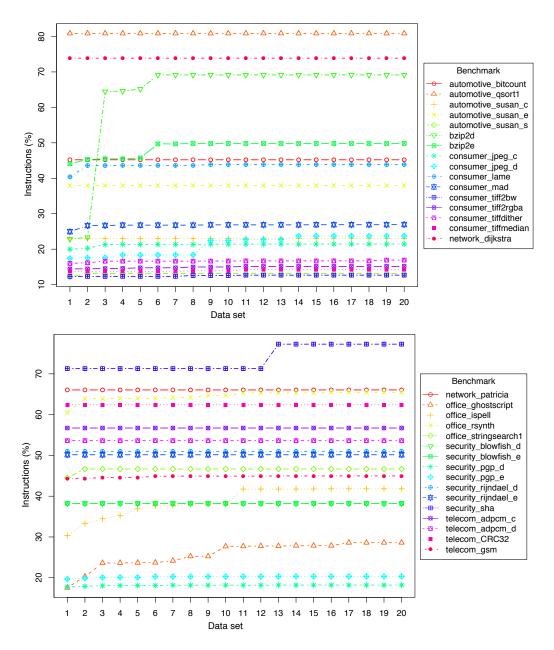

| 5.7 | Evolution of instruction coverage (y-axis) due to incremental execution of          |    |

|     | inputs for CBENCH                                                                   | 47 |

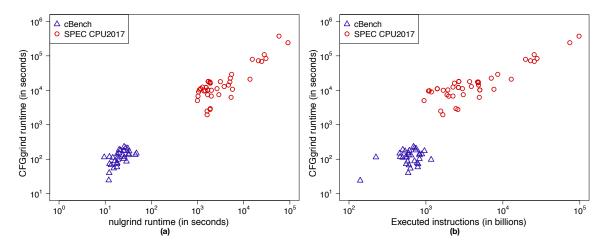

| 5.8 | Relation between execution time of non-instrumented programs with                   |    |

|     | NULGRIND (emulation only) and programs instrumented with CFGGRIND,                  |    |

|     | for CBENCH and SPEC CPU2017 (a); Relation between the number in-                    |    |

|     | structions observed during the execution of CBENCH and SPEC CPU2017 $$              |    |

|     | programs, and the running time of these programs, when instrumented with            |    |

|     | CFGgrind (b)                                                                        | 50 |

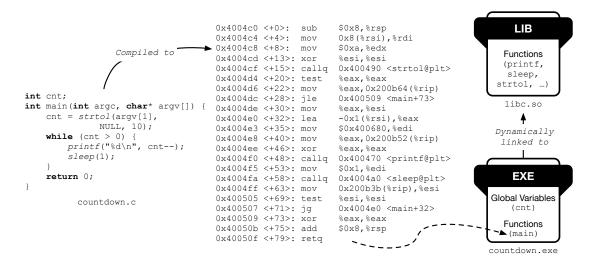

| 6.1 | Example code in C (left) compiled to x86-64 assembly instructions (middle)          |    |

|     | produced the executable file that is dynamically linked to the libc library         |    |

|     | (right)                                                                             | 55 |

| 6.2 | (Left) data-structures used to represent groups of instructions: a list of          |    |

|     | instruction addresses, plus a counter. (Right) dynamic instrumentation, in          |    |

|     | boldface, that precedes the execution of a group of instructions. $\ldots$ $\ldots$ | 56 |

| 6.3 | Files mapping onto memory with range addresses specified as base address            |    |

|     | and size                                                                            | 57 |

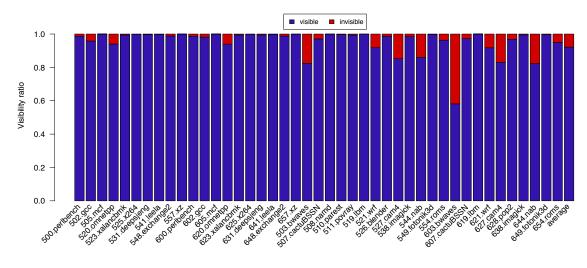

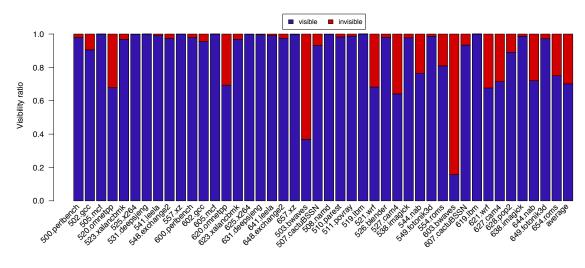

| 6.4 | Visibility ratio of SPEC CPU2017 programs compiled using GCC with -O0,              |    |

|     | running with reference inputs                                                       | 59 |

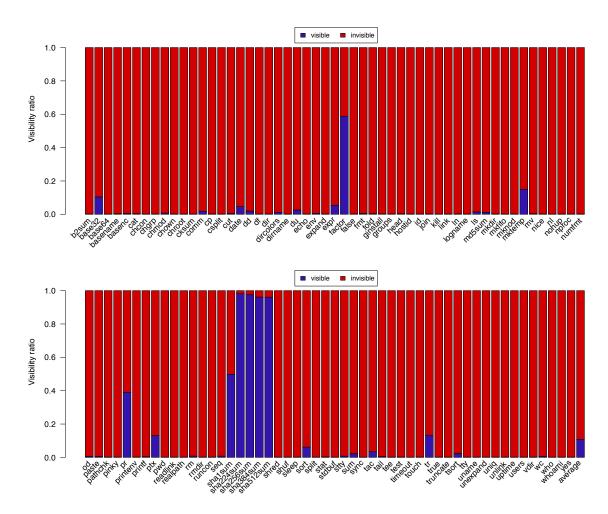

| 6.5 | Visibility ratio of GNU COREUTILS programs compiled using GCC with -O0.             | 59 |

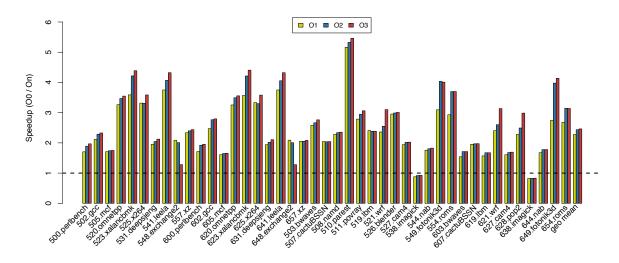

| 6.6 | Speedup produced by different optimization levels of GCC, when applied              |    |

|     | onto the SPEC CPU2017 programs                                                      | 62 |

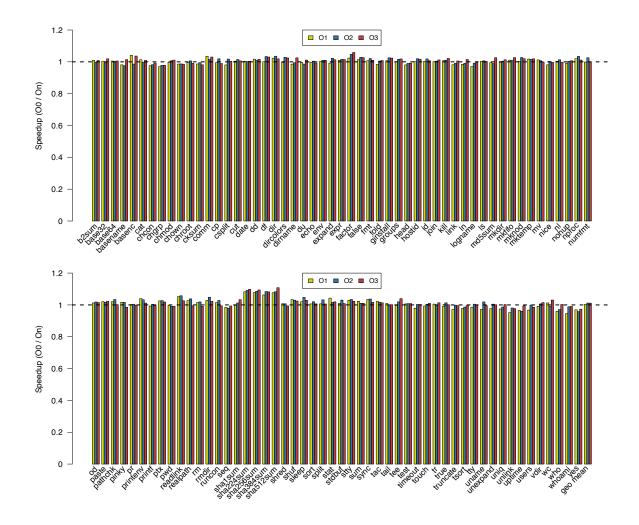

| 6.7 | Speedup produced by different optimization levels of GCC, when applied              |    |

|     | onto the GNU COREUTILS programs.                                                    | 63 |

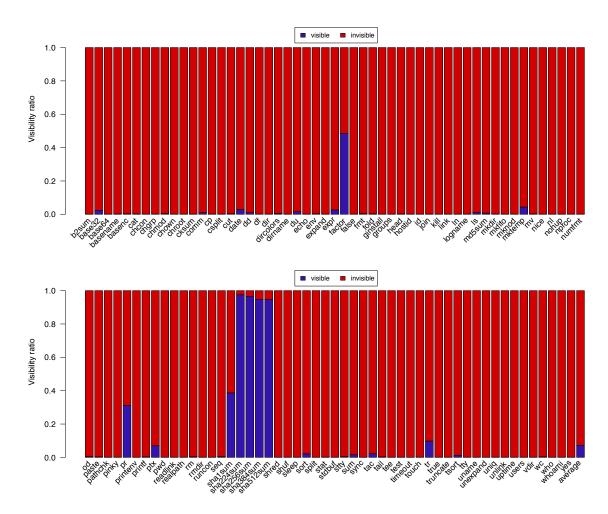

| 6.8 | Visibility ratio of SPEC CPU2017 programs compiled using GCC with -O2,              |    |

|     | running with reference inputs                                                       | 64 |

| 6.9 | Visibility ratio of GNU COREUTILS programs compiled using GCC with -O2.             | 64 |

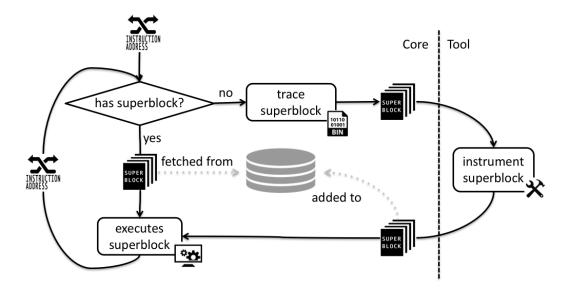

| 7.1 | VALGRIND's execution workflow.                                                      | 71 |

# List of Tables

| 3.1 | Qualitative comparison of the different tools considered in this work | 14 |

|-----|-----------------------------------------------------------------------|----|

| 5.1 | Comparison between CFGGRIND and DYNINST for CBENCH. In the column     |    |

|     | between the intersection of CFGGRIND and DYNINST, the percentage is   |    |

|     | given in relation to CFGGRIND and DYNINST, respectively               | 48 |

| 5.2 | Similar to Table 5.1, but for SPEC CPU2017                            | 48 |

|     |                                                                       |    |

# Contents

| A             | cknov | vledgments                                     | - |

|---------------|-------|------------------------------------------------|---|

| R             | esum  | o vii                                          | i |

| $\mathbf{A}$  | bstra | ct viii                                        | i |

| $\mathbf{Li}$ | st of | Figures ix                                     | - |

| $\mathbf{Li}$ | st of | Tables                                         | i |

| 1             | Intr  | oduction 1                                     | - |

|               | 1.1   | Contributions                                  | 2 |

|               | 1.2   | Publications                                   | ŀ |

|               | 1.3   | Outline                                        | Į |

| <b>2</b>      | Pre   | iminary Definitions 6                          | ; |

|               | 2.1   | Instruction                                    | ; |

|               | 2.2   | Group of Instructions                          | , |

|               | 2.3   | Control Flow Graph                             | 3 |

|               | 2.4   | Completeness                                   | ) |

|               | 2.5   | Conclusion                                     | - |

| 3             | The   | Need for CFG Reconstruction Tools 13           | 5 |

|               | 3.1   | On the Precise Representation of CFGs          | F |

|               | 3.2   | On Exact Profiling Information                 | ; |

|               | 3.3   | On the Incremental Construction of CFGs 18     | 3 |

|               | 3.4   | On the Execution of Multi-Threaded Programs 18 | ; |

|               | 3.5   | On Other Assembly Idiosyncrasies               | ) |

|               | 3.6   | Conclusion                                     | - |

| 4        | Dyı            | namic Reconstruction of CFGs                            | <b>22</b> |

|----------|----------------|---------------------------------------------------------|-----------|

|          | 4.1            | The Machine                                             | 22        |

|          | 4.2            | The Algorithm                                           | 24        |

|          |                | 4.2.1 Processing Programs                               | 25        |

|          |                | 4.2.2 Processing the Type of a Group's Tail Instruction | 29        |

|          |                | 4.2.3 Processing Groups of Instructions                 | 32        |

|          | 4.3            | Extensions to the Basic Algorithm                       | 34        |

|          |                | 4.3.1 Caching Strategy                                  | 34        |

|          |                | 4.3.2 Support to Multi-Threaded Programs                | 36        |

|          |                | 4.3.3 Handling Signal Events                            | 37        |

|          | 4.4            | Conclusion                                              | 38        |

| <b>5</b> | Eva            | luation                                                 | 39        |

|          | 5.1            | RQ1: Efficiency                                         | 40        |

|          | 5.2            | RQ2: The Impact of the Cache                            | 43        |

|          | 5.3            | RQ3: CFG Completeness                                   | 44        |

|          | 5.4            | RQ4: Incremental Construction of CFGs                   | 46        |

|          | 5.5            | RQ5: Combining Static and Dynamic CFG Reconstruction    | 48        |

|          | 5.6            | RQ6: Empirical Estimate of Asymptotic Complexity        | 49        |

|          | 5.7            | Conclusion                                              | 51        |

| 6        | Cas            | se Study                                                | <b>52</b> |

|          | 6.1            | Introduction                                            | 53        |

|          | 6.2            | Visible and Invisible Instructions                      | 54        |

|          | 6.3            | Analyzing Instruction Provenance                        | 56        |

|          |                | 6.3.1 Instrumenting Groups of Instructions              | 57        |

|          |                | 6.3.2 Classifying Instructions                          | 57        |

|          | 6.4            | Measuring Visibility Ratio                              | 58        |

|          |                | 6.4.1 RQ1: Visibility ratio in SPEC CPU2017             | 58        |

|          |                | 6.4.2 RQ2: Visibility Ratio in GNU COREUTILS            | 60        |

|          |                | 6.4.3 RQ3: the Impact of Compiler Optimizations         | 60        |

|          |                | 6.4.4 Reflection on the Results                         | 61        |

|          | 6.5            | Conclusion                                              | 63        |

| 7        | $\mathbf{Rel}$ | ated Work                                               | 66        |

|          | 7.1            | On Control Flow Graphs                                  | 66        |

|          | 7.2            | On Instructions Categorization                          | 68        |

|          | 7.3            | On Binary Instrumentation                               | 69        |

|    | 7.4 Conclusion | 72 |

|----|----------------|----|

| 8  | Conclusion     | 73 |

| Bi | bliography     | 75 |

# Chapter 1

## Introduction

The Control Flow Graph (CFG) [Aho et al., 2006, p.525] is a fundamental structure supporting the analysis and optimization of programs. A CFG is a directed graph where the vertices represent *basic blocks*. A basic block is a maximal sequence of instructions without branches, except at the end. Edges in the CFG denote possible program flows. Since its introduction in the 70's, likely due to the work of Allen [1970], CFGs have emerged as a mandatory program representation adopted in compilers, virtual machines and program verifiers. In program analyses based on source code, a CFG is produced either directly from that source code or from some high-level intermediate representation. However, there exists also much interest in recovering the CFG from the program's binary representation, as many researchers have demonstrated throughout the 90's [Cifuentes and Gough, 1995; Schwarz et al., 2002; Sites et al., 1993; Theiling, 2000]. However, while the construction of a CFG from source has a trivial solution, and is routinely performed by compilers, the reconstruction of a CFG from the binary representation is undecidable. Undecidability is easy to see: indirect branches, plus a simple extension of Rice's Theorem [Rice, 1953], hinder any algorithm from determining with certainty every possible flow in a program.

There are two ways to recover a CFG from a program's binary representation. The first approach, henceforth called *static*, tries to recover the program flow via static analysis of the binary program, i.e., from its .text section [Sutter et al., 2000; Kästner and Wilhelm, 2002; Bruschi et al., 2007]. This is the technique of choice employed by a number of well-known tools, such as DYNINST [Meng and Miller, 2016], BAP [Brumley et al., 2011], JAKSTAB [Kinder and Veith, 2008], SECONDWRITE [Smithson et al.,

2013], IDA PRO [Eagle, 2011], GNUOBJDUMP<sup>1</sup>, and OLLYDBG<sup>2</sup>. The second approach, henceforth called *dynamic*, seeks to construct a CFG out of instruction traces generated during the execution of a program. The dynamic reconstruction of CFGs is not as wide-spread as its static counterpart. We know one industrial-strength tool that provides such capability: Yount's DCFG [Yount et al., 2015], a software built on top of Intel's PIN [Luk et al., 2005], and released in 2015. Dynamic CFG builders can also be found as part of different research artifacts [Gruber et al., 2019; Xu et al., 2009; Shoshitaishvili et al., 2016], a few of which are publicly available<sup>3</sup>.

Static and dynamic approaches yield different results. Whereas the static approach gives a conservative approximation of the program's control flow, possibly containing paths that might never be traversed, the dynamic approach gives an underapproximation of the program flow. Every flow discovered by a dynamic tool is a true path within the execution of the program analyzed. However, the dynamic technique might miss paths that are not exercised by the inputs used in the reconstruction. Such differences lead to distinct applications. Static CFG reconstruction is typically used for security analyses [Song et al., 2008] and binary optimization [Panchenko et al., 2019; Zhou and Jones, 2019]. Dynamic reconstruction, in turn, is used to build dynamic slices [Agrawal and Horgan, 1990; Korel and Laski, 1988], and finds services in any situation where such slices are in need [Tip, 1994], such as malware detection, deobfuscation and profiling. Nevertheless, in spite of three decades of progress in dynamic slicing, the dynamic reconstruction of CFGs is still poorly understood, its benefits are often understated, and its engineering still leaves much room for improvement. Motivated by such observations, this work brings the following thesis:

Dynamic CFG reconstructors can be practical tools able to augment the coverage of static reconstructors and provide users with completeness information.

## 1.1 Contributions

This work brings the following improvements to the recovery of CFGs from binary code:

<sup>&</sup>lt;sup>1</sup>GNUOBJDUMP is a disassembler for GNU Linux. To know more, see https://www.gnu.org/ software/binutils/.

$<sup>^2</sup> OLLYDBG$  is a disassembler for Microsoft Windows. To know more, see <code>http://www.ollydbg.de/</code>.

<sup>&</sup>lt;sup>3</sup>As an example, tools available at https://docs.angr.io/, and https://github.com/toshipiazza/LLVMCFG provide some limited form of CFG reconstruction.

- **Completeness:** a new definition to quantify the coverage of CFG reconstruction (Chapter 2) and an empirical evaluation (Section 5.3) that reveals that a standard execution of the SPEC CPU2017 suite yields complete CFGs for 40% of the invoked functions. For CBENCH this number is similar: 37%.

- **Precision:** a suite of techniques that, once combined, yield more precise CFGs than the state-of-the-art approaches available today. Chapter **3** explains how our techniques support precise profiling information, deal with overlapping instructions and code shared by different functions, handle signals from the operating system, support multi-threaded programs and the incremental construction of CFGs from multiple inputs.

- Efficiency: new algorithms (Chapter 4) that support faster reconstruction of CFGs than state-of-the-art dynamic reconstructors. Our approach is  $\sim 7x$  faster than DCFG, a tool built over Intel's PINPLAY, and  $\sim 28\%$  faster than BFTRACE, the reconstructor from Gruber et al. [2019]. Our efficiency is due to extensive use of caching, as Section 5.2 shows.

- Complementarity: the demonstration that static and dynamic analyses can be combined to generate more complete CFGs. Section 5.3 shows that the combination of our technique with DYNINST, a state-of-the-art static CFG builder [Meng and Miller, 2016], increases coverage in CBENCH from 42% to 57%, and in SPEC CPU2017 from 39% to 46%.

The importance of the techniques introduced in this thesis are demonstrated in the following tools, produced as artifacts of this work:

- 1. CFGGRIND (https://github.com/rimsa/CFGgrind), a dynamic CFG reconstructor that runs in VALGRIND's infrastructure. The internals of this tool is described in details in Chapters 2 and 4.

- 2. DUMPCFGS (https://github.com/rimsa/dumpcfgs), a static CFG reconstructor that uses the DYNINST API. This tool is used as a counterpart in the evaluation of the the dynamic CFGGRIND tool in Chapter 5.

- 3. CMPCFGS (https://github.com/rimsa/cmpcfgs), a tool to compare the outputs produced by CFGGRIND and DUMPCFGS. The precision of both tools is compared in Section 5.5.

- 4. INSTRGRIND (https://github.com/rimsa/instrgrind), a tool to count executed instructions. This tool is used in the case study presented in Chapter 6.

#### 1. INTRODUCTION

CFGGRIND is mature enough to be used on every program of SPEC CPU2017. It supports the reconstruction of CFGs for programs that run in parallel. It also admits incremental construction of CFGs, meaning that a partial CFG built during one run of the program can be retrofitted into a new execution with different inputs in order to complement it. Thus, if new paths are traversed, more information is added to the CFG. This feature is specially important for programs that require multiple runs to construct a complete CFG. CFGGRIND can be used in tandem with DYNINST, a static binary analyzer, allowing it to discover the target of dynamic jumps, and to handle difficult code sections that would be missed in programs stripped of symbols and debugging information. Additionally, CFGGRIND provides exact profiling information. Contrary to sampling based techniques, it tracks how many times every instruction of the target program was executed, respecting the equity of flows: the number of program flows that enter any basic block equals the number of flows that leave it.

## 1.2 Publications

This work led to the publication of two papers. A first version of CFGGRIND with preliminary results was published in the 2019 edition of Simpósio Brasileiro de Linguagens de Programação (SBLP). Then, a more mature version of CFGGRIND with several improvements was developed. This enhancements combined with stronger results and better comparison between other CFG reconstructions tools was published in Software: Practice and Experience in 2020, a reputable Wiley's journal. This latter paper is responsible for the bulk of this thesis.

- Andrei Rimsa, José Nelson Amaral, and Fernando Magno Quint ao Pereira. 2019. Efficient and Precise Dynamic Construction of Control Flow Graphs. In Proceedings of the XXIII Brazilian Symposium on Programming Languages (SBLP 2019). ACM, New York, NY, USA, 19-26. DOI: https://doi.org/10.1145/3355378. 3355383

- Andrei Rimsa, José Nelson Amaral, and Fernando Magno Quint ao Pereira. 2020. Practical dynamic reconstruction of control flow graphs. In Softw Pract Exper. 2020; 1-32. DOI: https://doi.org/10.1002/spe.2907

## 1.3 Outline

This thesis is structured in the following seven chapters:

#### 1. INTRODUCTION

**Chapter 2.** This chapter provides preliminary definitions. It builds from the definition of an instruction, passes through the notion of groups, and leads to the definition of what is a control flow graph. Later, the concept of CFG completeness is presented.

**Chapter 3.** This chapter discusses five desired features that, despite decades of dynamic CFG reconstruction knowledge, are still not supported or partially handled by many tools. A comparison against CFGGRIND exposes the deficiencies of such tools.

**Chapter 4.** This chapter dives into how to perform the dynamic reconstruction of CFGs. First, an abstract machine that simulates the execution of a program is defined. Then, algorithms responsible for the reconstruction are provided. Also, a discussion about how to optimize them using caches and support for parallelism.

**Chapter 5.** This chapter handles the evaluation of the proposed solution. This evaluation is classified into five research questions, namely: how efficient is CFGGRIND, how the cache impact performances, what is the ratio between complete and incomplete CFGs, what is the impact of different input sets in the incremental refinement of CFGs, and how much information CFGGRIND adds to a static reconstructor.

**Chapter 6.** This chapter provides a case study on the visibility of instructions in the SPEC CPU2017 benchmark.

**Chapter 7.** This chapter compares our solution to related works. CFGGRIND is analyzed against other dynamic CFG reconstruction tools. How CFGGRIND relates to dynamic program slicing. Finally, how CFGGRIND compares against static CFG reconstructors.

**Chapter 8.** This chapter provides final remarks and future directions for this work.

## Chapter 2

## **Preliminary Definitions**

The definition of a CFG is readily available in any compiler textbook; however, given its central role in this thesis, this chapter revisits it. This chapter provides preliminary definitions for an instruction (Definition 1 in Section 2.1), and a group of instructions (Definition 2 in Section 2.2). These concepts are the required for the definition of control flow graphs (Definition 3 in Section 2.3). This formalism might differ from standard definitions because it uses a number of terms that are necessary to explain the CFG reconstruction algorithm in Chapter 4. This chapter brings, to the best of our knowledge, a novel definition of completeness (Definition 4 in Section 2.4). This definition allows the classification of the reconstructed CFG in respect to coverage: if all the paths of a given CFG were explored by the execution. This characteristic of completeness is further analysed in Section 5.3 of the evaluation (Chapter 5).

#### 2.1 Instruction

The building blocks of a CFG are instructions. In the binary representation of a program, each instruction is bound to an address. Each instruction also has an associated textual representation, e.g. *push %rbp*. An instruction can be formally defined as follows:

**Definition 1.** An instruction is a tuple I = (@addr, size, type, text), where @addr is the address of I in memory; size is the space that I occupies, measured in bytes; type represents a class to which I belongs; and text is the assembly textual representation of I. For the purposes of this thesis, instructions are classified according to their effect on the flow of control of the program. Therefore an instruction belongs to one of the following types: standard: flows to the next instruction;

- jump(@target, mode: (direct | indirect)): unconditionally jumps to @target address, either directly or indirectly;

- branch(@target, @fallthrough, mode: (direct | indirect)): conditionally branches to @target or @fallthrough address, either directly or indirectly;

- call(@target, mode: (direct | indirect)): invokes the function stored at the @target address, either directly or indirectly;

*return*: transfers control back to caller;

The standard instructions flow the execution to the instruction immediately after it. The jump, branch and call instructions can transfer control flow directly — the address is embedded in the instruction itself (e.g.: jmp @addr); or indirectly — the address is computed either from registers or memory (e.g.: jmp %rax). A NIL value is used as the @target address in case of indirect control flows. A return instruction transfers the execution back to the caller using the address immediately after the corresponding function call; hence, it behaves like an indirect branch. A return instruction is usually used to terminate a function, but it can also be used for irregular control flows, either maliciously or not. The tuple (@0x400580, 2, branch(@0x40058c, @0x400582, direct), 'jg 0x40058c') is an example of an instruction.

#### 2.2 Group of Instructions

Instructions can be logically organized in groups if they can be executed in sequence, without diverging the execution flow. A group of instructions can be formally defined as follows:

**Definition 2.** A group is an ordered sequence of instructions  $S = \{I_1, I_2, \ldots, I_n\}$  containing at least one instruction (|S| > 0). The instructions in a group are consecutive in the program  $(I_{n+1}.@addr = I_n.@addr + I_n.size)$ . The first instruction of a group is the *leader*. The last instruction is the *tail*. The *leader* is either the first instruction in a program, the target of a *jump*, *branch* or *call*, or the fall-through instruction of a non-taken *branch*. Instructions of type *jump*, *branch*, *call* and *return* cannot be followed by any other instruction.

Instructions are executed in order unless the program flow reaches an operation that diverts execution. Therefore, groups can be formed according to Definition 2 by tracing the sequential execution of instructions from a *leader* to a *tail*. The target of a *tail* instruction will be the *leader* of a next group to be formed. Thus, chains of groups are created during runtime. The sequence of instructions  $\{(@0x400597, 1, standard, 'leaveq'), (@0x400598, 1, return, 'retq')\}$  is an example of group, assuming that the program flow is diverted to @0x400597 at some point during execution.

### 2.3 Control Flow Graph

With the definition of an instruction 1 and a group 2, we can proceed with the definition of a control flow graph (CFG):

**Definition 3.** A Control Flow Graph (CFG) is a connected, directed graph G = (V, E), where:

• A node  $n \in V$  must be in one of the following categories:

entry: marks the start of the CFG.

*block(group, calls, signals)*: is a basic block that contains:

a group, according to Def. 2;

- a map of *calls* that associates the addresses of functions with pairs (CFG, count). The first element in the pair is the CFG of a function, and the second is the number of times that function was invoked by a call instruction in the *group*;

- a map of *signals*, similar to the map of calls, except that keys are signal ids, and the CFG, in the pair (CFG, count) is a signal handler with how many times it was invoked.

*phantom(@addr)*: is an undiscovered node represented by its address.

*exit*: marks the return of control to the caller of this CFG.

- *halt*: marks the stop of the execution of the program no further instructions can be executed from this point forward.

- An edge  $(n_1, n_2, count) \in E$  connects two nodes,  $n_1$  and  $n_2$   $(n_1, n_2 \in V)$ , with its execution count for profiling information,  $count \in \mathbb{N}$ , iff:

One of the following conditions is true:

1. The *tail* of  $n_1$  is not an unconditional jump and the *leader* of  $n_2$  immediately follows the tail of  $n_1$  in program order.

2. The *leader* of  $n_2$  is the target of a branch or jump instruction that is the *tail* of  $n_1$ .

And *count* is:

- 1. Zero, iff  $n_2$  is a *phantom* node, or when profiling information is not required.

- 2. A positive integer with the exact count of how many times this edge was visited during execution.

- Phantom, exit and halt nodes have no successors. The entry node has no predecessors. Thus, given an edge  $(n_1, n_2, count) \in E$ ,  $n_1 \notin \{phantom, exit, halt\}$  and  $n_2 \notin \{entry\}$ .

During the reconstruction of a CFG, the algorithm may process branches whose un-taken target has not been visited thus far. These targets are represented by phantom nodes.

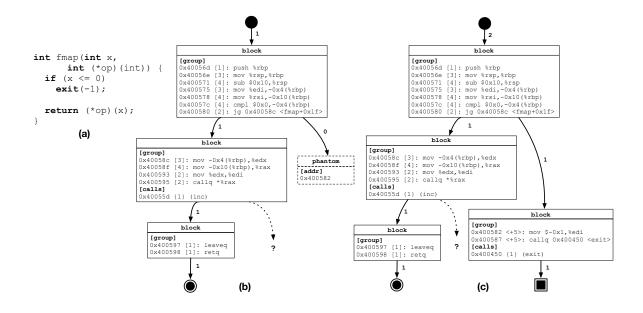

**Example 2.3.1.** Figure 2.1(a) shows the function FMAP written in C, and Figures 2.1(b,c) show two snapshots of FMAP's CFG. This function receives two parameters: an integer x; and a pointer to a function that returns an integer. It performs an indirect function call if  $\mathbf{x}$  is greater than zero. For this example, consider that function inc — not shown in Fig. 2.1(a) — was called. The filled oval in Figures 2.1(b,c) are entry nodes. The double filled ovals represent exit nodes. A double filled square denotes the *halt* node. Note that there is only one *exit* node and/or *halt* node per CFG. Functions with multiple exit points, either that terminate the function or terminate the program, must be connected to their respective *exit* or *halt* nodes. Figure 2.1(b)contains three basic blocks, each one with a group of instructions. The block at address @0x40058c holds that a call to function INC was invoked one time. This target is the value stored in the function pointer **\*op**. If FMAP is called with other arguments, more target functions will appear in the calls section of this block. Neither block contains invocations of signal handlers, and thus are not shown. The *phantom* nodes are represented with dashed outlines. The question mark represents possible unknown flows when the last instruction in the block is either a *jump*, *branch* or *call* node with *indi*rect mode. Note that dashed edges are used to connect question marks, but they serve merely as an indication of an indirect flow for this block.

Previous works have modelled the entire program as a single CFG [Theiling, 2000; Bernat and Miller, 2012; Meng and Miller, 2016]. The boundary of functions can still be recorded in such representation, as long as edges in the CFG are marked

Figure 2.1. (a) Example program. (b) CFG after first call with positive argument for x. (c) Refined CFG after second call with negative argument for x.

as *intraprocedural* or *interprocedural*. This formalism departs from that convention: a CFG, according to Definition 3, represents the instructions of a single function. Formalizing a CFG in this way makes it easier to combine the CFG representation with information extracted from compilers such as GCC and LLVM. In particular, representing each function as a separate CFG facilitates the task of tracking the entry and exit points of procedures. In rare occasions, the binary representation of a program can be built in such a way that a set of instructions can be executed through calls to multiple addresses. Meng and Miller solved this problem by allowing a CFG to have multiple entry points [Meng and Miller, 2016]. We enforce a constraint that a CFG must have a single point of entry. Thus, in CFGGRIND two different CFGs may execute a common subset of instructions. This duplication of information, however, has no penalties in the execution. Example 2.3.1 illustrate these concepts.

#### 2.4 Completeness

When a CFG contains an indirect jump, an indirect branch, or an indirect call, it is not possible to ensure that all possible execution paths have been discovered. Future executions of the program with different workloads may follow new execution paths. Also, the presence of phantom nodes indicates the existence of paths that have not yet been discovered. The concept of CFG completeness, for the purposed of dynamic reconstruction, can be defined as follows:

**Definition 4.** Given a control flow graph G = (V, E) (Definition 3), G is said to be **complete** iff, V contains an *entry* and at least an *exit* or a *halt* node; and  $\forall n \in V$ , the following conditions are true:

- 1. the successors of n are in V.

- 2.  $n \neq phantom$ .

- 3. if n is a block then the mode of the tail of the group of n is direct.

A CFG is complete if all its paths are known. Definition 4 uses a more restrictive notion of completeness: even if all indirections are proven to be constrained inside the same CFG, the existence of indirect jumps still classifies this CFG as incomplete.

**Example 2.4.1.** The examples in Figures 2.1(b-c) present an incomplete CFG because they contains both a *phantom* node and a *block* with an indirect call. Note that edges connecting phantom nodes, although known to exist, are never executed. Thus, they have a count of zero.

This classification is useful in the evaluation of complex code executions. For instance, malware programs may deliberately hide some part of their execution. In order to do so, they rely on constructs such as indirect jumps or calls to avoid exposing the address of the offending code. In such cases, CFGGRIND will mark the CFGs as incomplete. In other words, code that contains indirect control flow will invariably contain either phantom nodes or an indirect marking — the question mark in Figure 2.1. Further executions of the same program, with different inputs, might improve coverage; hence, reducing the number of incomplete CFGs. The reconstruction of dynamic CFGs is based on successive refinements. Example 2.4.2 shows how re-execution refines CFGs.

**Example 2.4.2.** Figure 2.1(c) shows the CFG that results from a new activation of the same function, but with different arguments. In this case, the branch at @0x400580 is not taken and leads to the discovery of the block at address @0x400582. In this example, the *phantom* node becomes a *block* node that is connected to the *halt* node.

#### 2.5 Conclusion

This chapter covered important definitions — instruction (Def. 1), group of instruction (Def. 2), and control flow graph (Def. 3) — that are used by the dynamic reconstruction

#### 2. PRELIMINARY DEFINITIONS

of CFGs by the algorithms discussed in Chapter 4. A new definition of completeness (Def. 4) was given to quantify the coverage of CFG reconstruction. The completeness of CFGs are evaluated in Section 5.3 (Chapter 5).

## Chapter 3

# The Need for CFG Reconstruction Tools

There are at least two tools that perform the dynamic reconstruction of control flow graphs, namely, DCFG [Yount et al., 2015] and BFTRACE [Gruber et al., 2019].  $DCFG^1$  is part of PINPLAY<sup>2</sup> — a framework for deterministically replaying a program execution. PINPLAY is publicly available, albeit closed-source. BFTRACE, in turn, is the first part of a four-staged implementation of dependence analysis Gruber et al., 2019. It builds intraprocedural control flow graphs and interprocedural call graphs. Revisiting these technologies, the need for further work in this area stems from two simple observations about state-of-the-art tools. On the one hand, the most precise of these tools, DCFG, incurs a heavy performance slowdown that makes its usage prohibitive in programs with long execution traces. On the other hand, BFTRACE, the faster dynamic analyzer, leaves too much information out from the CFGs that it reconstructs — namely, precise profiling data. This thesis shows that it is possible to reconstruct CFGs faster than BFTRACE, and still more exactly than DCFG. Chapter 5 provides empirical evidence to support this efficiency claim. This chapter explains why CFGGRIND's CFGs are more complete than similar structures produced by the other tools.

Table 3.1 presents a summary comparison of the three tools and indicates the section where each feature is discussed. Beware, however, that these tools are not strictly equivalent: being conceived with different goals, each of them has a distinct representation for CFGs. For instance, BFTRACE is part of a larger system whose purpose is to track dependencies between memory regions in order to advise for or

<sup>&</sup>lt;sup>1</sup>DCFG: https://software.intel.com/en-us/articles/pintool-dcfg

<sup>&</sup>lt;sup>2</sup>https://software.intel.com/en-us/articles/program-recordreplay-toolkit

against program parallelization. Nonetheless, BFTRACE is a standalone application whose sole purpose is to reconstruct a program's CFGs and call graph. DCFG is also part of a larger system, PINPLAY, which logs program state to allow re-execution, e.g., to support debugging. The code of DCFG is not open; hence, we cannot affirm that its only purpose is to reconstruct CFGs for PINPLAY. Nevertheless, from what we could infer from DCFG's documentation, such seems to be the case.

| Feature                  | CFGgrind   | BFTRACE     | DCFG                   | Section |

|--------------------------|------------|-------------|------------------------|---------|

| Completeness             | Reported   | Absent      | Absent                 | 3.1     |

| Program exit             | Present    | Absent      | Absent                 | 3.1     |

| OS Signals               | Tracked    | Absent      | Imperfect              | 3.1     |

| Edge count               | Present    | Absent      | Present                | 3.2     |

| Flow equity              | Present    | Absent      | Imperfect              | 3.2     |

| Incremental analysis     | Present    | Absent      | Absent                 | 3.3     |

| Multi-threading          | Handled    | Not handled | Handled                | 3.4     |

| Overlapping instructions | Different  | Different   | $\operatorname{Split}$ | 3.5     |

| Shared code in functions | Duplicated | Duplicated  | Shared                 | 3.5     |

Table 3.1. Qualitative comparison of the different tools considered in this work.

### 3.1 On the Precise Representation of CFGs

BFTRACE, DCFG and CFGGRIND adopt different representations for the program's control flow graph. CFGGRIND and BFTRACE associate a CFG for each identified program function, while DCFG provides a single, flattened, CFG for the entire program. However, the CFGs produced by CFGGRIND have a few features that are absent from the CFGs produced by at least one, and sometimes both, of the other tools.

First, CFGGRIND reports the **completeness**, a notion formalized in Definition 4, of a CFG. Neither DCFG nor BFTRACE let users know if a CFG had all its basic blocks visited during the execution of the program. CFGGRIND provides this functionality by augmenting the concept of a CFG with *phantom* nodes and annotations for indirect flows.

Second, the precise recognition of **exit points** is another feature missing in DCFG and BFTRACE. These tools, like CFGGRIND, track paths between different functions along the program's call graph. However, in both DCFG and BFTRACE it is not possible to know if a basic block ends only a function, or terminates the entire

program. Our experience using CFGGRIND as a debugger tells us that such differentiation is important to correctly identify the points where no other instructions can be executed.

Third, CFGGRIND tracks signal events that may occur during the program execution. Signals are particularly difficult to handle because they do not originate from specific instructions, e.g., call or jmp. Some instructions, such as div, mod, store and load can produce signals (SIGSEGV, SIGILL, SIGFPE, etc). Signals can come from outside the program, e.g., due to interruptions (SIGINT), or can be scheduled to happen, e.g., due to alarms (SIGALRM). Example 3.1.1 compares the support for this feature in CFGGRIND in contrast with the other tools.

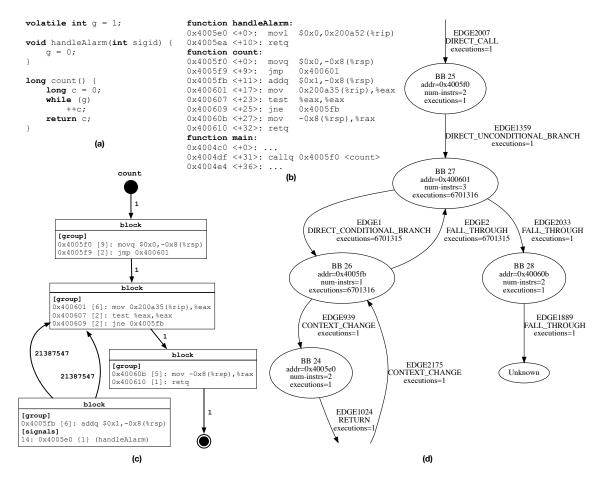

**Figure 3.1.** (a) Example program with alarm handler. (b) Assembly code for this example. (c) CFG obtained with CFGGRIND. (d) Simplified CFG obtained with DCFG, showing "unknown" node that emerges after signal handling.

**Example 3.1.1.** Figure 3.1 shows a sample program that has a signal handler (a) with its respective assembly code (b), and shows how signals are processed by CFGGRIND

(c) and DCFG (d). When a signal handler is activated, BFTRACE crashes and is unable to produce the CFGs for such a program. CFGGRIND records the address of the function handler called with its associated signal id at the basic block where the event originated. DCFG creates a special edge marking the function handler as a context switch, but without an associated signal id. Also, DCFG fails to track reliably the correct execution flow after the return of the signal handler. In Figure 3.1(d) the edge at address @0x400610 in BB 28, is misidentified as a fall-through edge, whereas it should have been marked as a return edge. Furthermore, the target of this edge points to a special Unknown node due to an invalid target address calculated at this point. Note that if a signal handler is never activated, none of the three tools are able to find its CFG. Also, the signal registration is not relevant to the context of the control flow graph, and thus is not tracked by any of the these tools.

## 3.2 On Exact Profiling Information

A profiler provides users with either exact or approximate information. In the latter category we have all the *sampling-based profilers*. In the former, we have *instrumen-tation* and *emulation* based profilers. CFG reconstructors can be used as a supporting infrastructure to build exact profilers. To fulfill this goal, three features are desirable: **edge count**, **call count** and **signal count**. Edge count gives the number of times each edge in the CFG was traversed by the program flow. Call count provides the number of times each function has been called during the execution of the program. Signal count holds similar information, but for signal handlers instead of functions calls. Both, CFGGRIND and DCFG provide these three features. They are absent in BFTRACE.

Edge counts, when available, should be subject of the Law of Flows, which Tarjan [1974], among other graph theoreticians, have postulated as: "the sum of incoming flows must equal the sum of outgoing flows on each vertex of a directed graph, except on its start and end nodes." In the context of this work, the count in the incoming edges must add up to the sum of the counts of the outgoing edges for any basic block traversed during program execution. The two exceptions are the program entry point, whose in-degree is zero, and the program exit point, whose out-degree is zero. This principle is true for CFGGRIND; however, it is not entirely true for DCFG.

**Example 3.2.1.** Figure 3.2(a) shows an example program where the compiler can optimize the invocation of function add depending on its calling context. As can be observed by the assembly code produced in Fig 3.2(b), the call in function normx was

**Figure 3.2.** (a) Example program with two distinct calls to function add. (b) Assembly code with a tail call optimization for this example. (c) CFGs obtained with CFGGRIND for each function. (d) Simplified CFG obtained with DCFG for this program.

optimized to use a jump instruction. However, the compiler was unable to use the same strategy for the call in function twice. Thus, function add is used in two distinct contexts. Similar situation is commonly observed in code in general. For example, LIBGFORTRAN (version 3.0.0) has some data transfer functions, e.g. transfer\_integer or transfer\_real, to copy data between different container types. These functions are used externally — using call instructions — , but are also used internally — using jump instructions after tail call optimization. Therefore, CFG reconstruction tools must be able to handle properly such cases. The three CFGs in Fig. 3.2(c) were produced both by CFGGRIND and by BFTRACE. Each CFG has its own distinctive copy of

a shared block — the block with address @0x400507 is duplicated in the CFGs for normx and add. DCFG on the other hand uses a single block (BB 17) in both contexts. Consequently, it is not possible to determine if the transfer of control happened due to a function call or due to an unconditional branch. In Figure 3.2(d), there are two return edges going out of BB 17, but only one incoming call — the other return edge is due to the jump from BB 18.

## 3.3 On the Incremental Construction of CFGs

Dynamic analyses require good datasets: the more inputs are available for a program, the more information can be inferred from the program's behavior. This principle applies to the dynamic reconstruction of CFGs. However, neither DCFG nor BFTRACE support the **incremental construction** of CFGs. In other words, it is not possible to combine events observed in two different executions of a program to build a refined version of its CFGs. CFGGRIND provides this functionality, as Example 2.3.1 illustrates. Thus, additional program inputs lead to successive refinements of this program's CFG; hence, increasing code coverage. Section 5.4 quantifies the benefits of incremental construction in the CBENCH suite. Note that this capability is only supported if, for each execution, the program is always loaded in the same memory region. Security protections, such as Address Space Layout Randomization (ASLR), must be disabled to achieve incremental construction coverage. This is not an issue for CFGGRIND since VALGRIND manages its own memory mappings when emulating programs execution. More details on how CFGGRIND supports incremental constructions of CFGs can be found in Section 4.2.

## 3.4 On the Execution of Multi-Threaded Programs

A parallel program can span multiple threads during its execution. Both CFGGRIND and DCFG supports tracking the execution of such threads; however, BFTRACE crashes in this scenario. DCFG provides detailed profiling information, where each edge in the control flow graph contains the execution count for each thread separately; CFGGRIND compounds the result of all threads as a total for each edge.

CFGGRIND leverages the serialization performed natively by VALGRIND, where the execution of multi-threaded programs is converted into a single-threaded application by using VALGRIND's own scheduling policy. CFGGRIND tracks each thread's context switch to account for the correct execution flow of programs. More details about the implementation of this feature can be found in Section 4.3. It is unclear how DCFG works internally to support this feature.

## 3.5 On Other Assembly Idiosyncrasies

Although low-level assembly code is usually derived from high-level languages via a compilation chain, some aggressive optimizations can dramatically change the structure of the target code. For instance, optimizations might force code sharing between multiple functions. Also, some sections of assembly code can have overlapping instructions. Overlapping happens mostly in hand-crafted code, which either implements some optimization or encodes malware. In this last category, we have examples of return oriented programming attacks [Shacham, 2007]. In all these cases, binary code presents idiosyncrasies that a reconstructor must handle.

**Figure 3.3.** Objdump snippet for functions \_\_read and \_\_read\_nocancel, from glibe 2.17, that share code. To see that overlapping happens, notice that  $[eb86a_{16}, eb86a_{16} + 22_{16}] \cap [eb860_{16}, eb860_{16} + 77_{16}] \neq \emptyset$ .

| 000eb86a l | F .text 00 | 000022read_nocance] | l |

|------------|------------|---------------------|---|

| 000eb860 w | F.text 00  | 000077read          |   |

**Example 3.5.1.** Figure 3.3 exemplifies the first situation: instructions shared between functions. A snippet of an object dump of mapped symbols available in GLIBC (version 2.17) for two function: <u>read</u> and <u>read</u> nocancel. The former function is mapped between addresses @@0xeb86a-@0xeb88c; while the latter is mapped between @0xeb860-@0xeb860-@0xeb867. Since there is an overlap of these two ranges, some instructions are shared by these functions. DCFG approaches this situation using an unique node that is shared across multiple parts of the entire control flow graph. This node can be interpreted as if a section of code has multiple access points. On the other hand, CFGGRIND and BFTRACE build a CFG for each function, which means that each CFG has its own copy of a block that contains these shared instructions. The same approach is employed by CFGGRIND to support functions with multiple entry points. Each entry point spawns a different CFG with its own copies of the shared instructions. Thus, every CFG in CFGGRIND has only a single entry point.

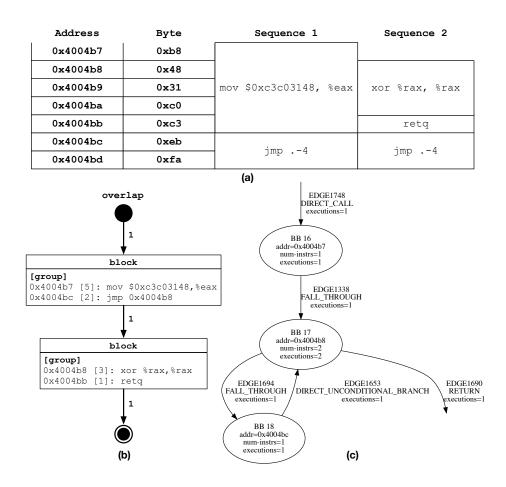

**Example 3.5.2.** Figure 3.4 exemplifies the second situation: a block of contiguous bytes can be interpreted as different sequences of assembly instructions. Such situation occurs when there is a jump or call to an unaligned target address. Fig. 3.4(b)

shows that CFGGRIND and BFTRACE obtained the same CFG, while Fig. 3.4(b) shows that DCFG splits the nodes incorrectly, leading to an unrealistic execution flow. A call to address @0x4004b7 activates Sequence 1 with two instructions. Its last instruction is a relative jump to the unaligned address @0x4004b8. Thus, Sequence 2 is activated. Of the three instructions of this sequence, the last one is never executed due to the return instruction. CFGGRIND and BFTRACE capture the correct behavior by treating the instructions individually in the blocks. However, DCFG treats the block as a range of addresses, disregarding how the instructions are read inside this range. This modus-operandi leads to the flawed split at node BB 16. Although seemly artificial, the unaligned access that this example illustrate is a key component in several real-world ROP-based program exploits, some of which are catalogued in the CVE database [Gorelik, 2018; Seebug, 2018; Alvarez-Perez, 2017].

**Figure 3.4.** (a) Hand-crafted example of two overlapping sequences of assembly instructions. (b) CFG obtained with CFGGRIND and BFTRACE. (d) Simplified CFG obtained with DCFG.

## 3.6 Conclusion

In this chapter CFGGRIND was compared against two other CFG reconstruction tools found in the literature: DCFG [Yount et al., 2015] and BFTRACE [Gruber et al., 2019]. An in-depth analysis of these three tools was conducted over several features concerning control flow graphs. Such features include how precise is the representation of the CFGs (Section 3.1), how exact are the profiling information provided (Section 3.2), how CFGs can be incrementally improved (Section 3.3), how multi-threaded programs are supported (Section 3.4), and how to handle specific assembly idiosyncrasies that can be generated by compilers (Section 3.5). We show that CFGGRIND is the most feature-rich tool available.

## Chapter 4

## Dynamic Reconstruction of CFGs

This chapter uses pseudo-code to explain the dynamic reconstruction of CFGs. CFGGRIND, the tool that prototypes the ideas presented in this thesis, is implemented in C, on top of VALGRIND. However, for ease of understanding, the algorithms in this chapter are presented in a Python-like format. Executable versions of these algorithms can be downloaded from CFGGRIND's repository.

Before diving into the algorithms, this chapter defines an abstract machine that is capable of simulation the execution of a program (Section 4.1). Then, the basic algorithm for the dynamic reconstruction of control flow graphs is presented (Section 4.2). Later, this algorithm is extended with features that highlight CFGGRIND's improved capabilities when compared to other evaluated tools (Section 4.3). These extensions are:

- the caching strategy employed by CFGGRIND that makes it the fastest tool among its competitors;

- the support for multi-threaded programs that makes CFGGRIND apart from BFTRACE [Gruber et al., 2019];

- and the effectiveness of the signal events handling that makes CFGGRIND more precise than DCFG [Yount et al., 2015].

## 4.1 The Machine

In the context of this work, a *machine* is any technology, be it based on interpretation, emulation or instrumentation, that produces traces representing the execution of programs. Typical machines include tools such as QEMU [Bellard, 2005], PIN [Luk et al., 2005], GDB and VALGRIND [Nethercote and Seward, 2007]. The instructions that appear in a trace are partitioned into groups according to Definition 2. Traces can be processed online, as soon as they are produced by the machine; or offline, as a *post-morten* analysis. The algorithm described in Section 4.2 is agnostic to this processing mode. CFGGRIND, implemented in VALGRIND, uses the online approach. The following example illustrates the notion of a trace.

| <pre>01: int total(int array[],<br/>02:</pre> | 0x400492 <+0>:<br>0x400493 <+1>:<br>0x400496 <+4>:<br>0x40049b <+9>:<br>0x4004a0 <+14>:<br>0x4004a2 <+16>:<br>0x4004a2 <+16>:<br>0x4004a4 <+18>:<br>0x4004a6 <+20>:<br>0x4004aa <+24>:<br>0x4004ac <+26>:<br>0x4004ae <+28>:<br>0x4004af <+29>: | cmp<br>jge<br>add<br>add<br>inc<br>jmp<br>pop | 0x4004ae <total+28><br/>(%rbx),%eax<br/>\$0x4,%rbx<br/>%ecx</total+28>                                                    |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| <pre>12: int main(int argc,<br/>13:</pre>     | 0x4004b0 <+0>:<br>0x4004b4 <+4>:<br>0x4004bc <+12>:<br>0x4004c1 <+17>:<br>0x4004c6 <+22>:<br>0x4004cb <+27>:<br>0x4004cf <+31>:                                                                                                                 | movl<br>lea<br>mov<br>callq<br>add            | <pre>\$0x10,%rsp<br/>\$0xa,0xc(%rsp)<br/>0xc(%rsp),%rdi<br/>\$0x1,%esi<br/>0x400492 <total><br/>\$0x10,%rsp</total></pre> |

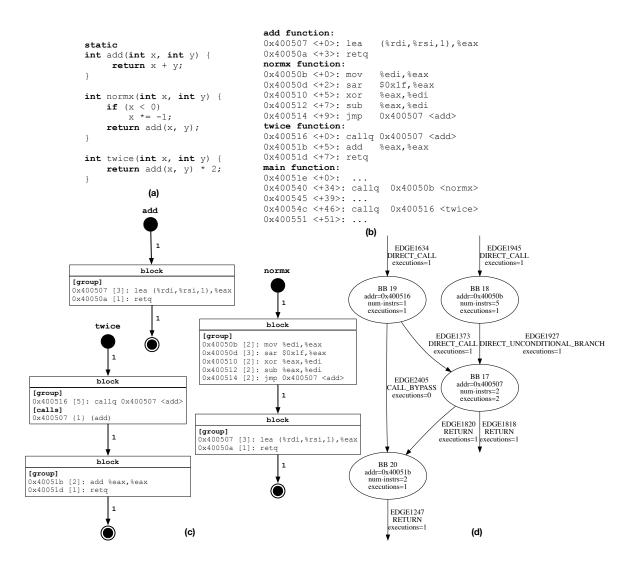

**Figure 4.1.** (a) Program written in C. (b) static assembly representation of the program.

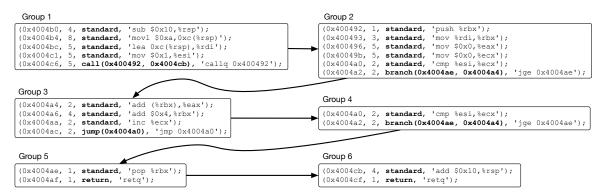

Figure 4.2. Execution trace of the program in Figure 4.1. Instructions are grouped according to Def. 2. Arrows show order in which groups are processed.

**Example 4.1.1.** Figure 4.1 shows a program (a) with two functions and its assembly representation (b). The execution of this program in a machine produces a trace formed by those assembly instructions. Such trace represents the paths traversed by the execution of the program. Figure 4.2 shows the different groups formed by the analysis of this execution trace. The *jump*, *branch* and *call* instructions in this trace are all direct, and thus the *mode* of each instruction is omitted. In this example, the body of the while loop in function total (Lines 5-8) executes only once.

# 4.2 The Algorithm

Central to the understanding of Algorithms 1-3, is the notion of a *state*, defined as follows:

**Definition 5.** A state is a tuple S = (current, callstack). Current is a pair (cfg, working), where cfg is the CFG (G = (V, E), Def. 3) currently being reconstructed, and working is one of this CFG's nodes  $(working \in V)$ . The callstack is a stack of  $(current, @ret_addr)$  pairs, where  $@ret_addr$  is a return address. The callstack's current pair is similar to the one in the state, except working must perform a function call (working.tail.type is call), and the  $@ret_addr$  is the address of the instruction immediately after this call (working.tail.type.fallthrough).

During the reconstruction of CFGs, the algorithms discussed in this section operate on a *state*. The processing of groups, such as those shown in Fig. 4.2, leads to changes in this state. Thus, Algorithms 1-3 are state-transition functions that map a state-group pair into another state (*state*  $\times$  *group*  $\mapsto$  *state*). When the algorithm processes a *working* node in the *current* CFG, another node becomes the *working* node. When the algorithm processes a function call, the *current* pair is pushed onto the *callstack* and its return address is set. A function return to an address matching a @*ret\_addr* in the *callstack* causes the stack to pop elements until this point is reached. The *current* pair associated with this return address is then restored as the *current* pair of the *state*. At initialization, the *current* is set to NIL and the *callstack* is empty (S = (NIL, [])).

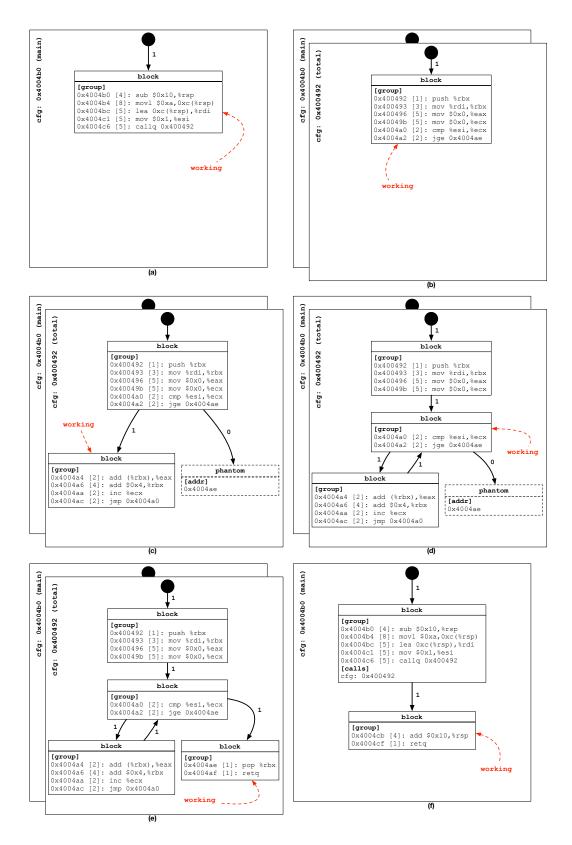

**Example 4.2.1.** Figure 4.3 shows the *state* after each one of the six groups in Figure 4.2 is processed. In this multi-layer representation, the front layer presents the *current* state, e.g., (*cfg, working*). Underneath layers represent the state's *callstack*. The front layer in Figures 4.3(a) and 4.3(f) represents the main function. The front layer in Figure 4.3(b-e) corresponds to the total function.

The algorithms discussed in this section use a core data structure, the cfg, with the following operations:

- *add\_node(node)*: adds a new node to the *cfg* if this new node is not already there.

- *add\_edge(src, dst, count)*: adds a new edge to the *cfg* from node *src* to node *dst* with *count* as the number of executions. If the edge already exists, increment the previous execution count by the value of *count*.

- find\_node\_with\_addr(@addr): searches for a block node with instruction at @addr, or a phantom node at @addr; returns NIL if not found.

- *phantom2block(phantom\_node, block\_node)*: replaces the phantom node with the block node, including moving its predecessors edges to the new node.

- $split(block\_node, @addr)$ : finds instruction  $i_j$  with address @addr in the group of the block node such that  $i_1 < i_j \le i_n$ , moves the instructions  $\{i_1, \ldots, i_{j-1}\}$ , and its predecessor to a new block node, and finally connects them with a new edge.

#### 4.2.1 Processing Programs

Algorithm 1 is the entry point for the process of CFG reconstruction. The algorithm assumes the existence of a global *state*, initialized as (NIL, []), that is readily available during processing. This global *state* can be externally manipulated to support features such as multi-thread programs and signal handlers (Sec. 4.3). The algorithm receives a *machine* and a *mapping* of CFGs indexed by their addresses. The *mapping* can be either empty or pre-populated with CFGs loaded from a previous run. This is they key to support incremental construction of CFGs as described in Section 3.3. By loading previously computed CFGs, the algorithms described in this section can further improve them, as they continue to refine the CFGs as new paths are explored during the execution.

Algorithm 1 expects a sequence of groups generated by the machine to reconstruct the CFGs dynamically. Each group is then processed individually (Lines 2-12) by this algorithm. Once the machine halts, i.e. no more groups are generated, the algorithm finalizes the remaining CFGs by connecting the *working* nodes, of the *state*'s *current* pair or of the *callstack* if present, to the *halt* node (Lines 13-17). Finally, Algorithm 1 returns the updated mapping with all reconstructed CFGs at line 17.

For each group (Lines 2-12), Algorithm 1 manipulates the state in two phases:

Figure 4.3. State after processing each of the six groups listed by Figure 4.1.

**Algorithm 1** Process program by handling each group of instructions generated by a machine during execution.

```

global: state

input: machine, mapping

output: mapping

1: function PROCESS PROGRAM(machine, mapping)

2:

for group in machine.RUN() do

3:

@addr = group.leader.addr

4:

if not state.current then

5:

initial = mapping.GET(@addr) if mapping.HAS(@addr) else mapping.PUT(@addr, CFG())

6:

state.current = (initial, initial.entry)

7:

else

8:

assert state.current.working instanceof Block

9:

mapping = PROCESS TYPE(mapping, state.current.working.group.tail.type, @addr)

10:

end if

11:

state.current.working = PROCESS GROUP(state.current.cfg, state.current.working, group)

12:

end for

13:

while state.current do

14:

state.current.cfg.ADD EDGE(state.current.working, state.current.cfg.halt, 1)

15:

state.current = state.callstack.POP() if not state.callstack.EMPTY() else nil

16:

end while

17:

return mapping

18: end function

```

- Phase 1 (Lines 4-10): takes an action based on the previous working node. In the absence of the working node, initializes the first CFG (Lines 4-6). The initial CFG is either fetched from the mapping based on the address of the group's leader instruction if existent, or it is created and set in the mapping (Line 5). Then, the state's current pair is configured with this CFG and its entry node (Line 6). Otherwise, ensures that working node is a basic block (Line 8) and activates Algorithm 2 (Line 9) passing the type of the tail instruction of the working node and the address of the next instruction of the group.

- Phase 2 (Line 11): activates Algorithm 3. This algorithm is responsible for building a new path or following an existing one in the CFG. It may create or split nodes in this process, but it will never transition between CFGs. At the end, Algorithm 3, sets the *working* node to the node which its *tail* is last instruction of the processed group.

**Example 4.2.2.** Each one of the six frames in Figure 4.3 is a snapshot of the state after each iteration of Algorithm 1. Snapshots are taken immediately after the processing of the group by Algorithm 3 (Line 11).

Group 1: (Figure 4.3(a)) In phase 1, the CFG for function MAIN is created with its entry node set as the working node. In phase 2 this group is processed leading to the creation of the block with address @0x4004b0 with all the instructions of the group. A new edge was created with execution count of 1 from the previous

#### 4. DYNAMIC RECONSTRUCTION OF CFGs

*working* node, i.e. *entry* node, to the current *working* node, i.e. the newly created block.

- **Group 2:** (Figure 4.3(b)) In phase 1, the pending call of the previous block is processed. The CFG for function TOTAL at address @0x400492 is created and inserted into mapping. This CFG is added to the call map of the working node (block @0x4004b0). Then, the state's current pair is pushed onto the state's call-stack with the return address @0x4004cb the fall-through of the instruction call. Finally, there is a switch to the new CFG by setting the state's current pair with this CFG and its entry node. In phase 2, the second group is processed in a similar fashion as the previous. A block with address @0x400492 is created, connected from the entry with execution count of one, and set as the new working node.

- **Group 3:** (Figure 4.3(c)) In phase 1, the pending branch of the previous block is processed. The algorithm creates a phantom node with address @0x4004ae for the target address of this branch. Note that no *phantom* node is created for this branch's fall-through address, since this path will be covered in phase 2 for this group. Thus, in phase 2 the block @0x4004a4 is created, connected, and set as the *working* node.

- Group 4: (Figure 4.3(d)) In phase 1, there is no action for the jump instruction of the previous block, since the jump target will be handled by this group. In Phase 2, there is a jump to the instruction @0x4004a0 that is inside block @0x4004a0. Therefore, this block must be split in two blocks: block @0x400492 with four instructions and block @0x4004a0 with two instructions. Then, a new edge with one execution is created between blocks @0x4004a4 and @0x4004a0. All the instructions of this group are matched against the ones in block @0x4004a0; thus no new information is added at this point. Afterwards, this block becomes the *working* node.

- Group 5: (Figure 4.3(e)) In phase 1, the branch of instruction @0x4004a2 is processed again, but both paths it can follow have already been covered; thus nothing is changed for this CFG. The execution followed the target of the branch, which lead to this group. In phase 2, the leader of this group matches the address of the phantom node at @0x4004ae. Thus, the *phantom* node is converted to a *block* node and it is populated with the instructions of this group and the update count of the edge increased by one. Finally, this new block becomes the *working* node.

**Group 6:** (Figure 4.3(f)) In phase 1, a function return occurs, because the tail instruction of the *working* node is a return. First, the *working* node is connected to the *exit* node with an edge count of one. Then, the algorithm checks if there is a return address in the *callstack* that matches the address of the leader of this group. In this case, the leader address of this group @0x4004cb matches the top of the stack. Thus, the *state's current* pair is restored by popping the top of the stack. At this point, the current *working* node is block @0x4004b0, and the *cfg* the CFG of the MAIN function. In phase 2, the block @0x4004cb is created, connected, and set as the *working* node.

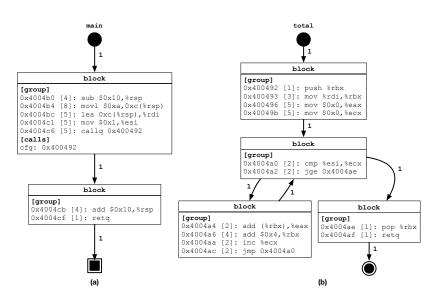

After processing all the groups, Algorithm 1 connects the state's *working* node to the *halt* node to conclude the execution (Lines 13-16). Then, Algorithm 1 returns the *mapping* containing the functions MAIN and TOTAL that were invoked during the execution of this program (Line 17). The final CFG for both functions can be seen in Figure 4.4.

Figure 4.4. The resulting CFGs for functions MAIN (a) and TOTAL (b) in the *mapping* produced by Algorithm 1.

#### 4.2.2 Processing the Type of a Group's Tail Instruction