# **UNIVERSITY OF CINCINNATI**

\_\_\_\_\_, 20 \_\_\_\_\_

\_,

in:

It is entitled:

Approved by:

# Memory Synthesis for FPGA-Based Reconfigurable Computers

A thesis submitted to the

Division of Research and Advanced Studies of the University of Cincinnati

in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

in the Department of Electrical and Computer Engineering and Computer Science of the College of Engineering

April 2001

by

## Amit Kasat

B.E. (Electronics and Instrumentation Engineering) Devi Ahilya University, Indore, India June 1998

Thesis Advisor and Committee Chair: Dr. Ranga Vemuri

#### Abstract

A design executing on Reconfigurable Computer (RC) typically reads from and writes to physical memories on the RC. For data intensive applications like Digital Signal Processing (DSP), Image Processing, Pattern Recognition, etc. memory reads and writes constitute a large portion of the total design execution time.

With the advent of on-chip memories available on various FPGA devices, a complete hierarchy of physical memories is now available on a RC. Different types of memories provide different access latencies, storage capacities, multiple ports etc. An intelligent usage of these memories can lead to significant improvement in the read/write latency of the design. Most automated synthesis tools targeted for RCs do a trivial form of memory mapping, which does not make use of this memory hierarchy. In order to exploit the memory hierarchy, more sophisticated logic partitioning and memory mapping tools are required.

This thesis presents an automated memory mapping methodology during high level synthesis flow. By memory mapping, we mean performing a detailed assignment of various data structures, which are part of the design, to the physical memories available on the RC. We use *Tabu Search* meta-heuristic to find a good mapping for various logical memories of the design onto physical memories available on the RC. We present a heuristic, called *Rectangle Carving*, to map a single logical memory onto the RC. Tabu search calls this heuristic at every iteration to get new solutions. To ensure correct functionality for the memory mapping, additional control logic is required. This logic is used to resolve potential memory access conflicts, and to make the details of memory mapping transparent to the accessing logic, thus keeping the implementation of the logic independent of memory mapping.

Quality of memory mapping is closely related to the way logic partitioning is done on the board. We present an integrated methodology to perform both logic partitioning and memory mapping together. A tabu search formulation is used to do the task. This helps in getting good overall design mapping in very little time.

The execution time of the tool on benchmark examples is found to be very small. For design containing 100 logical memories, the stand alone memory mapper took less than 150 seconds. The heuristic is produces results within 3.5% of the near optimal results produced by the ILP-approach. The spatial partitioner took less than 800 seconds for designs having 100 compute tasks and 100 logical memories.

I dedicate this work to my parents

### Acknowledgments

First and foremost, I would like to thank my advisor Dr. Ranga Vemuri. Working with him was a great learning opportunity for me. His guidance, suggestions and encouragement was the driving force for this work. I

I am greatful to Dr. Harold Carter and Dr. Karen Tomko for giving their valuable suggestions and comments on my thesis work and for taking time off their busy schedule for the thesis defese.

This research is supported in part by US Air Force, Wright Labs, WPAFB, under contract number F33615-97-C-1043. I thank Mr. Al Scarpelli for providing valuable suggestions. The comments and suggestions provided by Ms. Kerry Hill and Mr. Darrell Barker were very helpful.

I would like to extend special thanks to Iyad. I enjoyed and learnt a lot while working in close coordination with him. He was always present for help and suggestions. I recall the long and intense discussions with him at various times of my stay here. I have fond memories of the great time I had with Srini here. I can not imagine spending last year and a half without him being here. He was a constant source of help and support. I would like to thank Sree for her constructive suggestions and motivation and helping me sail through the tough times here. I would also like to thank Rajesh for his help and suggestions.

It was great to work with Madhu and Siva for the review meeting. It was nice to have friends like Vijay, Sairavi, Jawad and Manish. I would also like to thank Ela, Karam, Margret, and other *DDELites* for their help.

I am thankful to my roommates Mahesh and Swaroop to bear with me during the last few months of my stay here. I also recall the great time I had with Sid, Sathya and Neema. I am lucky to have made lots of friends in Cincinnati with whom I had a great time.

Last but not the least, I would like to express my gratitude to my parents for encouraging me with my endeavors and for being immensely patient and supportive towards me during my stay here. Without them, it would not have been possible for me to make it so far.

# Contents

| Li | List of Figures i |                                                          |    |

|----|-------------------|----------------------------------------------------------|----|

| Li | st of T           | Tables                                                   | vi |

| 1  | Intro             | oduction                                                 | 1  |

|    | 1.1               | Reconfigurable Computing Platforms                       | 1  |

|    | 1.2               | Memory Features on a RC                                  | 2  |

|    | 1.3               | Motivation                                               | 6  |

|    | 1.4               | Related Work                                             | 8  |

|    |                   | 1.4.1 Memory Mapping for Custom Hardware                 | 8  |

|    |                   | 1.4.2 Memory Mapping for Predefined Hardware             | 9  |

|    |                   | 1.4.3 Integrated Spatial Partitioning and Memory Mapping | 10 |

|    | 1.5               | Overview of the Thesis                                   | 10 |

|    | 1.6               | Organization of the Thesis                               | 11 |

| 2  | Defi              | nitions and Methodologies                                | 12 |

|    | 2.1               | Board Architecture                                       | 12 |

|    | 2.2               | Input Design                                             | 16 |

|    | 2.3               | Tabu Search                                              | 17 |

|    | 2.4               | Tabu Search Enhancements for Memory Synthesis            | 19 |

|    | 2.5               | Discussion and Summary                                   | 22 |

| 3  | Men               | nory Synthesis                                           | 24 |

|    | 3.1               | Design and Architecture Specification                    | 24 |

|   | 3.2                                                                                      | Mapping Definitions                          |                                                          |

|---|------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------|

|   | 3.3                                                                                      | Problem Definition                           | 27                                                       |

|   | 3.4                                                                                      | Modeling of Logical Memory as a Rectangle    | 27                                                       |

|   | 3.5                                                                                      | Heuristic : Rectangle Carving                | 28                                                       |

|   | 3.6                                                                                      | Control Logic                                | 34                                                       |

|   |                                                                                          | 3.6.1 Arbitration                            | 35                                                       |

|   |                                                                                          | 3.6.2 Address Translation and Enable Logic   | 36                                                       |

|   |                                                                                          | 3.6.3 Handling Multiple Ports                | 39                                                       |

|   |                                                                                          | 3.6.4 Putting It Together                    | 40                                                       |

|   | 3.7                                                                                      | Constraints                                  | 42                                                       |

|   |                                                                                          | 3.7.1 Architectural Constraints              | 42                                                       |

|   |                                                                                          | 3.7.2 Design Constraints                     | 43                                                       |

|   | 3.8                                                                                      | Cost Function and Estimation                 | 44                                                       |

|   | 3.9                                                                                      | Experimental Results                         | 46                                                       |

|   | 3.10                                                                                     | Observations and Summary                     | 53                                                       |

|   |                                                                                          |                                              |                                                          |

| 4 | Into                                                                                     | rested Logic Doutitioning and Mamour Manning | 54                                                       |

| 4 |                                                                                          | grated Logic Partitioning and Memory Mapping | 54                                                       |

| 4 | Integ<br>4.1                                                                             | Alternatives and Motivation                  | 54                                                       |

| 4 |                                                                                          | Alternatives and Motivation                  | 54<br>54                                                 |

| 4 | 4.1                                                                                      | Alternatives and Motivation                  | 54<br>54<br>56                                           |

| 4 | <ul><li>4.1</li><li>4.2</li></ul>                                                        | Alternatives and Motivation                  | 54<br>54<br>56                                           |

| 4 | 4.1                                                                                      | Alternatives and Motivation                  | 54<br>54<br>56<br>56                                     |

| 4 | <ul><li>4.1</li><li>4.2</li></ul>                                                        | Alternatives and Motivation                  | 54<br>54<br>56<br>56                                     |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                            | Alternatives and Motivation                  | 54<br>54<br>56<br>56<br>57                               |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                            | Alternatives and Motivation                  | 54<br>54<br>56<br>56<br>57<br>58<br>58                   |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                            | Alternatives and Motivation                  | 54<br>54<br>56<br>56<br>57<br>58<br>58<br>58             |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                | Alternatives and Motivation                  | 54<br>54<br>56<br>56<br>57<br>58<br>58<br>58             |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>              | Alternatives and Motivation                  | 54<br>54<br>56<br>56<br>57<br>58<br>58<br>58<br>58<br>59 |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul> | Alternatives and Motivation                  | 54<br>54<br>56<br>57<br>58<br>58<br>58<br>58<br>59<br>60 |

| 5.1 | Contributions of the Thesis | 64 |

|-----|-----------------------------|----|

| 5.2 | Directions for Future Work  | 65 |

66

# Bibliography

# **List of Figures**

| 1.1  | A Typical FPGA Based Reconfigurable Platform                                                                 | 2  |

|------|--------------------------------------------------------------------------------------------------------------|----|

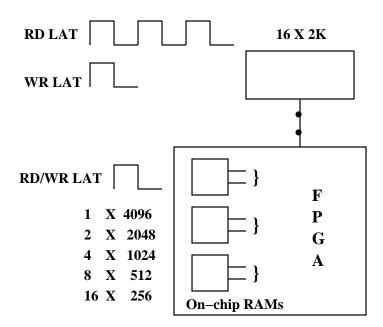

| 1.2  | Different Read and Write Latencies                                                                           | 4  |

| 1.3  | Different Configurations for same storage space                                                              | 5  |

| 1.4  | A Typical High Level Synthesis Flow for Reconfigurable Platforms                                             | 7  |

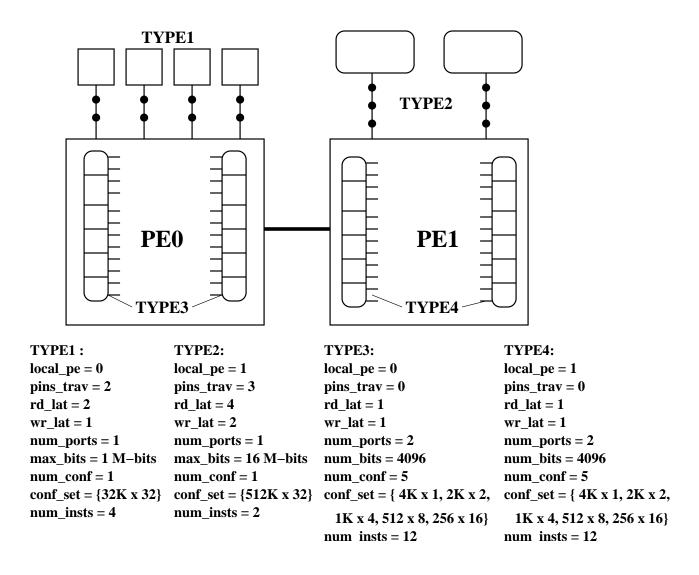

| 2.1  | Various Features of Memories Available on a RC                                                               | 14 |

| 2.2  | Tabu Search Algorithm                                                                                        | 18 |

| 2.3  | <i>Tabu List</i>                                                                                             | 19 |

| 2.4  | Flow Chart for Weighted Tabu Evaluation                                                                      | 21 |

| 3.1  | Design Specifications with and without logic partitioning information                                        | 25 |

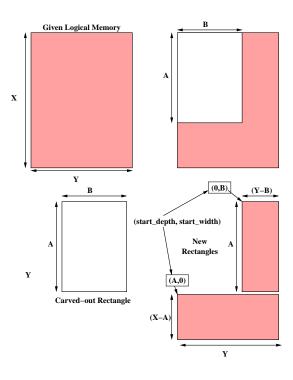

| 3.2  | Rectangle Model for A Logical Memory                                                                         | 28 |

| 3.3  | Possible Sub-rectangles for a Rectangle                                                                      | 29 |

| 3.4  | Algorithm for Mapping a Logical Memory                                                                       | 30 |

| 3.5  | Algorithm for Carving a mappable sub-rectangle from a given rectangle onto the given port                    | 31 |

| 3.6  | Algorithm for Generating Rectangles from unmapped part of another rectangle after carv-<br>ing has been done | 32 |

| 3.7  | Rectangle Carving Process                                                                                    | 32 |

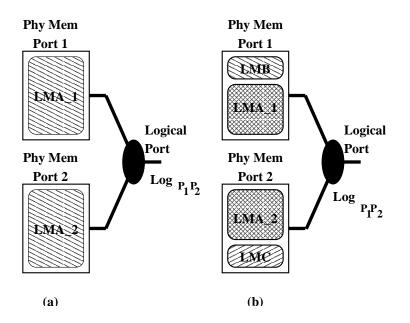

| 3.8  | Logical Port                                                                                                 | 35 |

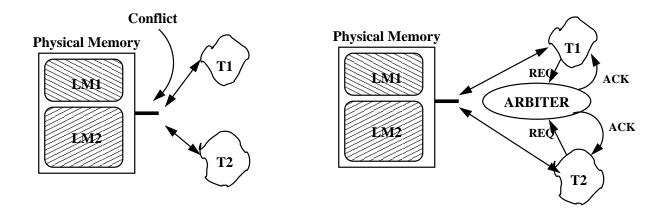

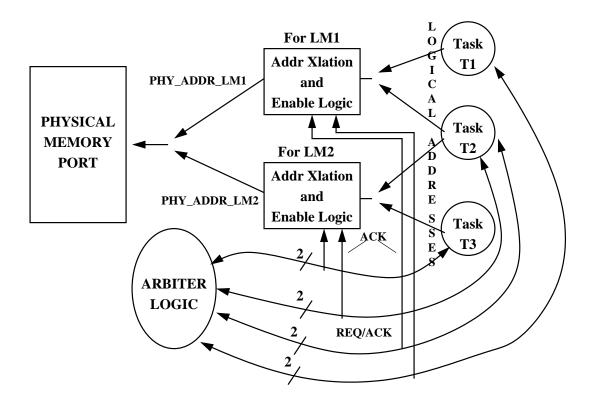

| 3.9  | Memory Access Conflict resolution using Arbiters                                                             | 37 |

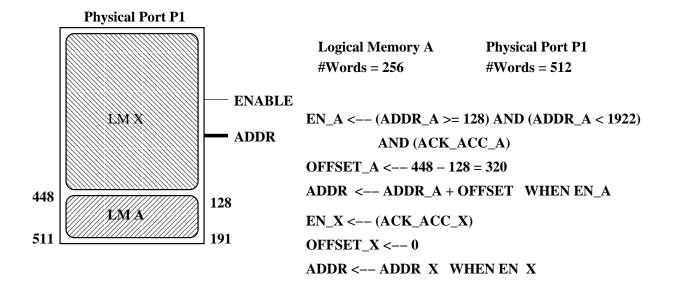

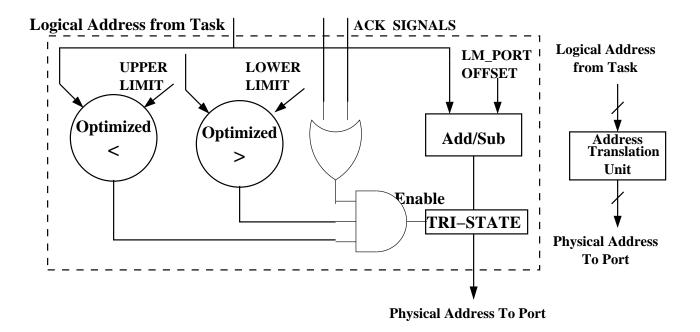

| 3.10 | Address Translation and Enable Logic                                                                         | 38 |

| 3.11 | An Implementation for the Address Translation and Enable Logic Unit                                          | 39 |

| 3.12 | Algorithm for assigning offset to ports of a multi-port physical memory                                      | 40 |

| 3.13 | The Overall Scheme                                                                                           | 41 |

| 3.14 | Target Architecture for Examples                                                         | 47 |

|------|------------------------------------------------------------------------------------------|----|

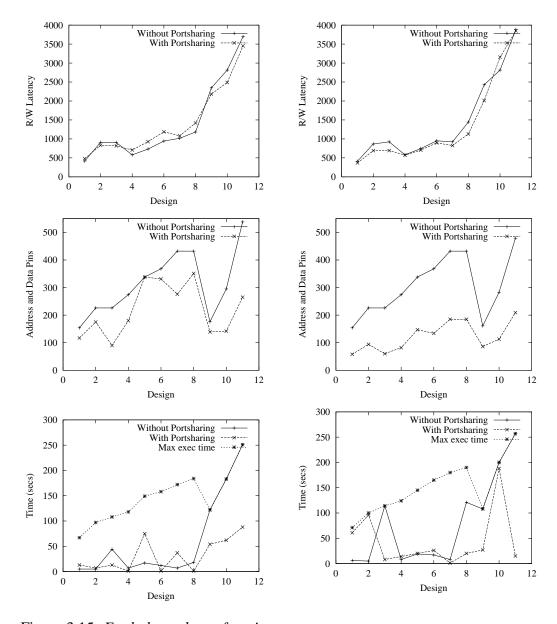

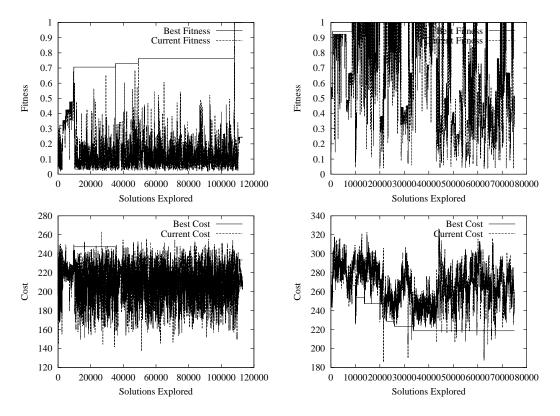

| 3.15 | For balanced cost function                                                               | 49 |

| 3.16 | For unbalanced cost function                                                             | 49 |

| 3.17 | Trace for no portsharing                                                                 | 50 |

| 3.18 | Trace for portsharing                                                                    | 50 |

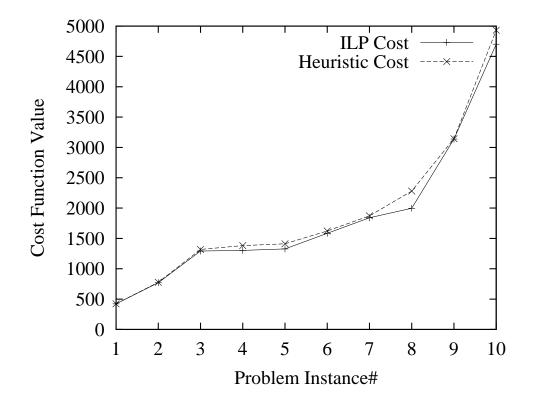

| 3.19 | ILP and Heuristic Cost Comparison                                                        | 52 |

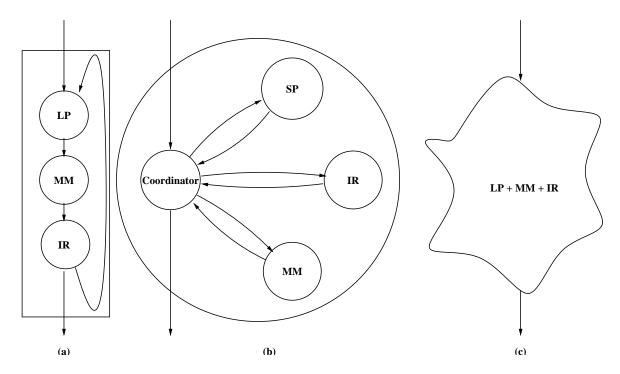

| 4.1  | Different Ways of performing Logic Partitioning, Memory Mapping and Interconnect Routing | 55 |

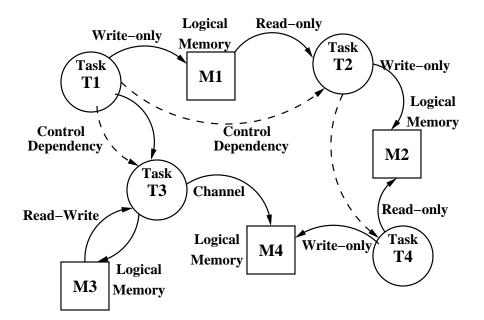

| 4.2  | An Example design specified in USM                                                       | 57 |

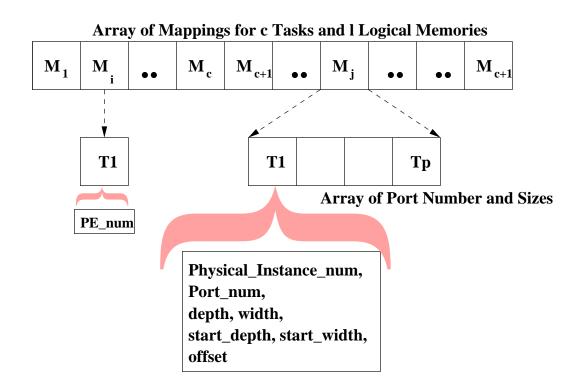

| 4.3  | Heterogeneous array of mappings for compute tasks and logical memories                   | 59 |

# **List of Tables**

| 1.1 | Number of Block RAMs on various devices of Virtex-E series     | 5  |

|-----|----------------------------------------------------------------|----|

| 1.2 | Different configurations for on-chip memories                  | 6  |

| 3.1 | Area occupied by arbiters of different sizes                   | 44 |

| 3.2 | Results of Memory Mapping for benchmark examples               | 47 |

| 3.3 | Comparison of results obtained from ILP and Heuristic Approach | 52 |

| 4.1 | Design Data for Benchmark Examples                             | 61 |

| 4.2 | Results of Logic Partitioning and Memory Mapping               | 62 |

# Chapter 1

# Introduction

Reconfigurable devices like *Field Programmable Gate Arrays (FPGAs)* have been the focus of attention because of the quick design turn-around time they allow. Most designers utilize *FPGAs* as a platform for prototyping of designs. For prototypes, the focus is on functionality rather than on performance. However, with the increasing pressure on time to market, and the tremendous increase in the density and complexity of FPGA devices available now, they have become a viable contender for being used in the final design itself. Today, FPGAs provide more than 3 million device equivalent logic capacity.

A *Reconfigurable Computer (RC)* is a hardware platform which can be reused by configuring the device for new design. This is possible by the virtue of its programmable devices. A RC comes ready to use, with the complete design environment. A wide variety of commercially available tools targeting FPGAs provide the complete design flow right from synthesis to place and route. Together, these have made reconfigurable platforms a feasible alternative to *Application Specific Integrated Circuits (ASICs)* for a range of applications.

# 1.1 Reconfigurable Computing Platforms

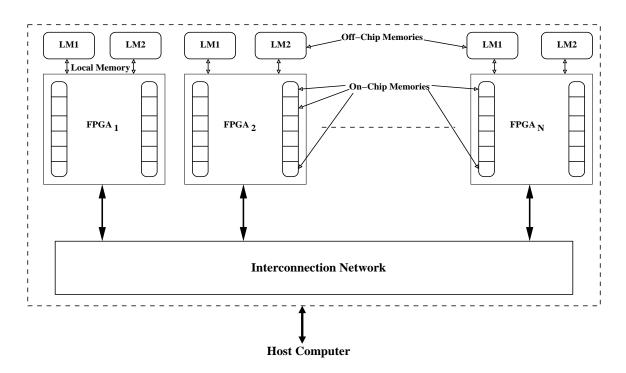

The aim of any reconfigurable platform is to provide the ability to put, with ease, user logic design on to the device. A non-trivial, RC is attached to a processor called the *host controller*. This machine is responsible for providing configuration bitstream, control signals, data for the design etc. In a typical RC, FPGAs provide the computational power. Memories are used to provide input and output data for the design. These memories can be shared between FPGAs or they can be local to a single FPGA. The host machine accesses the memories either directly or through the FPGA. For a multi-FPGA RC, a set of interconnection network is present for communication between various design parts mapped to different

Figure 1.1: A Typical FPGA Based Reconfigurable Platform

FPGAs. This interconnection may be programmable to provide additional flexibility to accommodate needs for a range of applications. A logical architecture of a typical RC is shown in Figure 1.1. Many RCs are available from both academia and industry. Some examples of commercial RCs are Annapolis Microsystem's Xilinx 4013 based *WildForce* [4] and Virtex based *WildStar* [5] series, and Altera's RIPP-10. University of Cincinnati's RACE [26] and University of Southern California's SLAAC-1V [32] are examples of RCs developed in the academia.

## **1.2 Memory Features on a RC**

A design, down-loaded onto the FPGA, needs some inputs, upon which it can operate and produce some outputs as the result. This can be looked upon as essential communication of the design with its environment. The input and output to the design can be given in following ways :

- Input is made part of the design itself and output is directed to either some device on the RC (e.g. display) or is read back by the controller immediately. In this case, inputs are synthesized, along with the design, onto the device. This is not a feasible option for a non-trivial design. Besides, the whole synthesis has to be carried out again for every set of input data.

- The host controller gives inputs to the design as and when required. Besides overhead logic for

handshaking between the design and the host, this approach will make the design very slow.

• The host controller writes inputs into some memories on the RC. The design can read from and write to these memories when required. The host can read-back these memories in the end. This approach can handle large amount of input and output data for the design, without slowing it down.

Clearly, the last approach is the most feasible and practicle. All contemporary RCs come with large sizes of memories which the logic inside the FPGA can access.

There are lots of variations in the type of memories found an RC. Some of the memories and their features found on the RC are described below.

#### 1. SRAM (Static Random Access Memory)

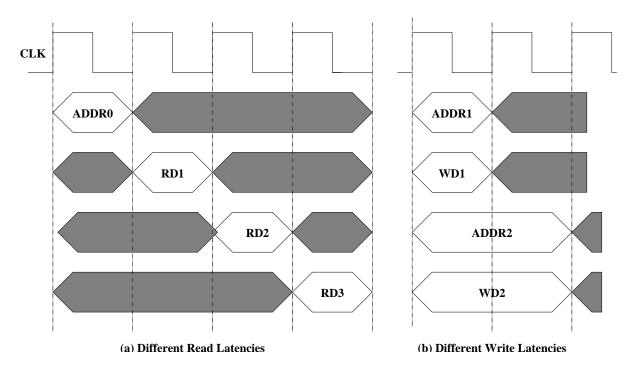

Cheap cost and easy availability makes SRAMs the most widely used memories, found on almost all RCs. They are also one of the biggest memories present on a RC. A typical SRAM based memory is around 32-bits wide and can have a depth from a few hundred K-words to a few Mega-words. Typically, SRAMs have read and write latencies of 1 clock cycle each. However, in most cases, FPGA logic can not access these memories directly. A Memory Interface, provided by the designer of the RC, controls all accesses to the memory. An interface serves many purposes, like, safeguarding memory against accidental simultaneous accesses by parallely executing logic, making actual pin location details transparent to the user, providing simpler access to memory port signals, making the design portable across device sizes by providing an interface for each device size etc. These memory interfaces generally govern the access latencies of SRAM, For example, in the WildForce [4] series of RCs, the interface provides a read latency of 2 clock cycles and a write latency of 1 clock cycle. In the *WildStar* [5] series of RCs, the interface provides read latency of 3 clock cycles. Even for the same interface, there can be different modes of accessing the memories. The SLAAC-1V series of RCs have two modes. One is the *pipelined* mode in which although the read latency is 4 clock cycles, the memory can be accessed at a clock frequency of up to 133 MHz. On the other hand, in the *flowthrough* mode, latency is only 3 clock cycles. However, the maximum memory clock frequency can be only 66 MHz. Thus we see that even for the same type of memory, the RC-designers can provide different access latencies, which practically makes them of different types. Figure

1.2 shows various read and write latencies.

#### 2. ZBT (Zero Bus Turnaround Memory)

ZBTs are memories which allow memory operations on two consecutive clock cycles. The logic can read-back the data from the same memory location to which it wrote in the previous clock cycle.

Figure 1.2: Different Read and Write Latencies

SRAMs typically require a *dead* clock cycle between two operations. These types of memories are useful for applications which process a large amount of data and where access latencies can make a big impact on the overall design latency.

## 3. On-Chip Memories

Most contemporary FPGA devices have memories on the chip. Such on-chip memories provide a different memory architecture. There are large number of small-size instances which provide fast access. The *Xilinx-Virtex* series of devices have small memory structures called the *Block RAMs* (*BRAMs*) [35] which are present on the chip. These memories can be used in either synchronous or asynchronous mode. In synchronous mode, they have a read and write latency of 1 clock cycle each. There are large number of BRAMs available on the chip, e.g XCV3200 has 108 BRAMs. Similarly, *Altera FLEX 10K* [3] series of devices have *Embedded Array Blocks* and *Altera APEX E* [2] devices have *Embedded System Blocks*. Table 1.1 shows the number of on-chip memories present on different families of reconfigurable devices.

#### 4. Different Number of Ports

Besides difference in size and speeds, memories can also differ in the number of ports through which they allow access, e.g. BlockRAMs in Xilinx Virtex FPGAs have 2 ports each. Multiple ports, which allow simultaneous access to same memory space, can be exploited to speed up designs.

| Device  | Logic Area(#CLBs) | #Block RAMs |

|---------|-------------------|-------------|

| XCV50   | 384               | 16          |

| XCV100  | 600               | 20          |

| XCV150  | 864               | 24          |

| XCV200  | 1176              | 28          |

| XCV400  | 1200              | 40          |

| XCV1000 | 6144              | 64          |

| XCV3200 | 16224             | 104         |

Table 1.1: Number of Block RAMs on various devices of Virtex-E series

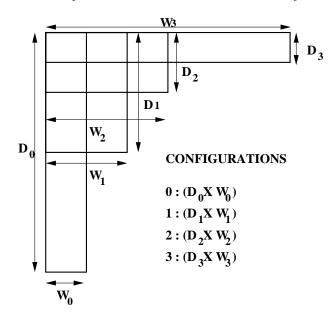

Figure 1.3: Different Configurations for same storage space

#### 5. Different Configurations

For certain types of memories, each port of an instance can be configured in a different way. In other words, each port provides a different view of the same physical storage space. This feature is most common for on-chip memories. e.g. Virtex BlockRAMs can be configured to have different Depth-Width combinations Table 1.2 shows the storage capacity and various configurations for memories on different devices. Depending on the type of data structure to be mapped, the memory can be configured in different ways, thus providing opportunity to use it in better ways. Figure 1.3 shows how changing configuration changes the memory accesses.

#### 6. Pins Traversed

The maximum clock speed at which a design operates depends on the length of the longest routed

| Device           | Max Number of Bits | Configurations                        |

|------------------|--------------------|---------------------------------------|

| Xilinx Virtex    | 4096               | $4096 \times 1,  2048 \times 2,$      |

|                  |                    | $1024 \times 4 \qquad 512 \times 8,$  |

|                  |                    | $256 \times 16$                       |

| Xilinx Virtex-II | 18432              | $16384 \times 1, 8196 \times 2,$      |

|                  |                    | $4096 \times 4 \qquad 2048 \times 9,$ |

|                  |                    | $1024 \times 18, 512 \times 36$       |

| Altera FLEX 10K  | 2048               | $2048 \times 1,  1024 \times 2$       |

|                  |                    | $512 \times 4$ , $256 \times 8$ ,     |

| Altera APEX E    | 4096               | $4096 \times 1,  2048 \times 2,$      |

|                  |                    | $1024 \times 4$ , $512 \times 8$ ,    |

|                  |                    | $256 \times 16$                       |

Table 1.2: Different configurations for on-chip memories

wire. Generally, a signal which crosses the chip boundary and traverses across pins causes the most delay. On a RC, different memories require different number of pins to be traversed before reaching the memory ports. On-chip memories do not require any wire to be routed outside the chip and hence can lead to higher clock speeds. Some off-chip memories are connected directly to the FPGA. Some others are connected through interconnect devices, like a cross-bar, thus increasing the path an accessing logic needs to traverse.

## 1.3 Motivation

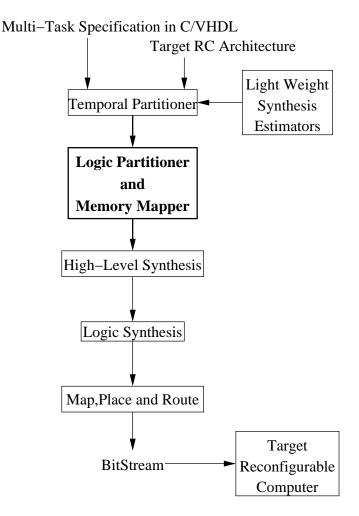

Since quick design turn around time and flexibility are one of the most attractive features of a RC platform, an environment which provides ease of designing is necessitated. The environment should be automated at various stages so that the need for designer's interaction, and hence the chances of mistakes, is minimized. A *High Level Synthesis (HLS) Flow* is a suitable option. A typical HLS flow takes a behavioral specification of the design as input. If the estimated area of the design is more than the total area available over all the devices, it has to be *temporally partitioned* [16]. For small designs, there will be only one temporal partition. If there are more than one FPGAs on the RC, each temporal partition may have to be further partitioned so that each part fits one device. Besides, various logical memories accessed by any logic in the spatial partition has to be mapped to some physical memory instance. Together, this can be termed as *spatial partitioning* [27]. This temporal and spatial partitioning results in a set of logic partitions. Each partition is estimated to fit on a single device. Design space exploration [23] can provide an implementation of each logical design segment such that the overall design has improved logic area and

Figure 1.4: A Typical High Level Synthesis Flow for Reconfigurable Platforms

latency characteristics. The output of a HLS flow is a structural specification at *Register Transfer Level* (*RTL*) [19]. These RTL specifications are then synthesized for the specific device to get gate level specifications. Synthesis is followed by mapping the gate level design onto the component-library available on the device. The mapped components are finally placed at some physical location and the interconnect signals are routed. The place and routed [36] design is converted into a bit-stream, which is used to configure the FPGA.

Figure 1.4 shows various steps involved in taking a design through a HLS Flow

The architecture of any RC is already decided at the time of its usage. Thus, there are fixed resources which can be used in certain ways. Any technique which attains better utilization of resources will results in better performance without incurring any extra cost. Thus, it is of utmost importance to exploit the available resources to extract best possible performance.

The previous section lists the features in which different types of physical memories can differ. With in-

crease in design sizes, the number of different logical data structures used in a design varies from a few to a few hundreds. The task of deciding which data structure of the design should be mapped to which physical memory becomes a non-trivial one. Before the arrival of on-chip memories, the total number of physical memories were very few. A RC would typically have between 1 to 10 physical memories, each being single-ported and providing same access latencies. Thus memory mapping could be done by hand. However, with the arrival of on-chip memories, there can be a few hundred physical instances available, having variations in features. With decreasing ratio of number of pins available per logic area available, it will become imperative to utilize *on-chip* memories as storage space. Not only do they alleviate pin requirements, but also provide faster access. Thus the problem of memory mapping becomes a combinatorial problem, its complexity directly increasing with increase in number of logical memories and physical instances. It is virtually impossible to do a good memory mapping by hand. For very large designs, it might be difficult to do even a constraint satisfying memory mapping by hand. For Data Intensive Applications like DSPs, Image Processing, Speech Recognition etc., significant improvements can be achieved by using a memory mapper which takes into account these factors. Besides, for proper working of any memory mapping, additional logic needs to be inserted into the design. There clearly is a necessity for an automated memory synthesis framework.

In this thesis, we present a heuristic memory synthesis methodology that tries to improve the overall design parameters like latency, routing resources required, design clock cycle etc. targeted towards RC platforms.

## 1.4 Related Work

Memory synthesis is the process of mapping various logical data structures used in the design to some appropriate physical instances. As outlined in [14], the process of mapping *logical to physical memory* can be divided into two steps: (*i*) translating the storage requirements onto logical memories, i.e. forming the data structures needed by the design, and (*ii*) mapping the logical memories onto the physical memories of the hardware; i.e. assigning the data structures to the memory banks.

Memory mapping can be broadly classified into two categories, based on the target of the synthesis, *Memory Mapping for Custom Hardware* and for *Predefined Hardware*.

#### 1.4.1 Memory Mapping for Custom Hardware

A lot of research has been done on the problem of memory synthesis for *Application Specific Integrated Circuits (ASICs)*. For ASICs, the problem is that of mapping various logical memory data structures

onto a predefined set of library components. The optimization goals include minimizing the number of different physical memory components used and placing the chosen components so as to minimize routing requirements and signal delay. Minimizing the resources required is as important as optimizing various performance parameters. The constraints are at more abstract level, in terms of the overall area available, design latency desired, number of available pins for off-chip communication etc. Restrictions also arise out of the availability of components in the library.

In research done as part of the *data path synthesis* problem, the tools map each logical memory to some specific component from the library and connect them to the accessing logic. In the context of high level synthesis, many researchers tried to form groups of variables. These groups are then partitioned to form data segments. Some researchers did not take interconnection cost into consideration [31], while others have taken this cost also during variable grouping [18]. An *Integer Linear Programming (ILP)* approach has been used in [1,6] to group registers to form multi-port memory modules. Interconnection cost incurred in routing address and data buses from memory modules to the accessing logic has been of significant importance in these approaches. Minimizing the number of memory modules required was an important way of reducing the interconnection cost and thus satisfying the pin constraints. In other approaches, [15] concentrate on minimizing the area while finding a legal packing of the logical segments

#### 1.4.2 Memory Mapping for Predefined Hardware

In the case of synthesis for RC platforms, an important difference is that the resources available are already fixed. Trying to minimize resource utilization may not be the best approach. The goal is to optimize performance while satisfying the constraints posed by the RC architecture.

In [7,34], researchers try to use on-chip memories available on FPGA devices for implementing logic. The approach does not exploit them as storage space for logical memories. [33] considers on-chip memories for memory mapping. In [11], the same technique is improved for dual-ported on-chip memories. In both cases, the framework considers only one type of physical bank and does not handle both single and dual ported at the same time.

In [21], Ouaiss and Vemuri approach the problem using ILP formulation. They target memory mapping for RC architecture. The framework considers all instances simultaneously and gives optimal mapping. However, as the problem size increases, the ILP formulation takes a long time to converge. In the extension of this work in [20], mapping is done in two stages. First, *Global Mapping* and *Detailed Mapping*. Global mapping predicts how mapping would be done if a logical memory is mapped to a particular type of physical memory. This prediction is done for all logical memory and physical memory type combinations.

Based on the predicted mapping, an optimal assignment of physical memory type is done for each logical memory. During *detailed mapping*, for each type of physical memory, all instances of that type and all logical memories assigned to it in the earlier stage are considered. Mapping a logical memory to specific instance(s) and port(s) is performed. This results in much faster execution time. However, if a logical memory is bigger than an instance, this approach allows the logical memory to be split only in some predefined manner, decided during the preprocessing stage. Thus, some of the solutions are excluded. This restriction may prohibit the mapper to find a solution where one may exist.

#### **1.4.3 Integrated Spatial Partitioning and Memory Mapping**

If a design is bigger than an individual logic device, it has be *spatially partitioned*. Spatial Partitioning is very closely linked to memory mapping. The quality of memory mapping depends heavily on where the accessing logic is placed. If accessing logic is placed in a device such that address and data signals need to be routed across chips, the clock period of the final design will significantly deteriorate. In addition, it will also consume the scarce interconnection resources. [17] and [8] present very early work done in the field of logic partitioning. However, they deal with a very fine level of granularity which is not suitable during high level synthesis. In [27], Srinivasan and Vemuri handle the two problems at the same time. However, the memory mapping part is simplified and does not consider on-chip memories or multi-ported memories. It assumes all physical instances to be of the same type. It further assumes only one physical instance local to every FPGA. Each logical memory was required to fit into a physical instance. Splitting across multiple instances was not permitted.

### **1.5** Overview of the Thesis

In the previous sections of this chapter, we presented the various steps involved during the high level synthesis flow targeted towards RCs. We motivated the use of a memory mapping methodology in the flow and showed the impact it can have on design quality.

The focus of this thesis is the memory synthesis technique used to improve design latencies. It can be done at various stages

• *Stand-alone Memory Mapping*: Mapping technique, used to minimize design latencies without directly considering the logic which accesses the memories, is presented. In the absence of any information about logic partitioning, the mapper tries to optimize various objectives like : (1) the access times of various logical memories, (2) the total number of address and data pins which might poten-

tially be routed across devices, (3) the number of blocks of data that can be processed, (4) the effect of physical location of memory instances on design clock frequency. The mapper assumes that there is only one FPGA and all logic has been mapped to this FPGA. It is also assumed that all physical memory types are local to the only FPGA. A heuristic called *Rectangle Carving* is presented in this thesis. This heuristic is used to map each logical memory to multiple instances of a type of physical memory. Tabu Search is used to guide this heuristic.

- *Partial Information from Logic Partitioner:* The mapping technique can take advantage of some of the information which might be available if logic partitioning has been performed. For example, if information regarding which FPGAs contain the tasks accessing a particular logical memory is known, various routing requirements can be determined. The effect of remote memory accesses (logic accessing physical memory not local to its FPGA) on clock can be estimated.

- *Integrated Logic Partitioning and Memory Mapping:* An integrated approach to perform both logic partitioning as well as memory mapping is presented. This approach promises to deliver high quality porting of the design to the target RC architecture. The search engine is guided by Tabu Search. At each iteration, some compute tasks and logical memories are re-mapped from their current position. Again, the heuristic, Rectangle Carving, is employed to find a mapping of logical memory for a different memory type.

# **1.6** Organization of the Thesis

The remainder of this thesis is organized as follows. Chapter 2 discusses various aspects of the target RC architecture. It presents various components of the input design which is to be mapped. The chapter deals in detail about the Tabu Search technique employed to guide both the memory mapping and logic partitioning algorithms and the adaption of these techniques to specifically suit the problem in hand.

Chapter 3 presents the main contribution of this thesis, the memory synthesis framework. It presents details of how the problem is formulated for Tabu Search and the algorithm used to perform mapping of individual logical memories. We also present various factors used to evaluate a given memory mapping solution and the results of memory mapping.

Chapter 4 presents the integrated logic partitioning and memory mapping technique. It discusses how the integrated approach is different from the stand-alone memory mapper presented in Chapter 3. Results of partitioning on various benchmark examples is presented to show the the effectiveness of the technique.

We present the summary and some directions for the future work in Chapter 5.

# Chapter 2

# **Definitions and Methodologies**

In this chapter, we introduce various terminologies related to the *memory mapping* and *logic partitioning* problem. These terms will be used in the rest of the thesis. Here, we will give a broad definition of every term. Different assumptions will be made about these definitions in various parts of the thesis. Depending upon the context of the discussion, we will state those assumptions, the need for them and their justification. We classify the definitions into two categories. *Board Architecture* related definitions are presented in Section 2.1, and *Input Design* related definitions are presented in Section 2.2

Section 2.3 outlines the *Tabu Search (TS)* algorithm, which is used to guide both memory mapping and partitioning algorithms. We present the basic Tabu Search algorithm which is independent of the problem it is used to solve. In Section 2.4, variations and enhancements of the TS used for both memory mapping and spatial partitioning are presented. We summarize the discussion by briefly mentioning about other methodologies which can be used for the problem in Section 2.5.

# 2.1 Board Architecture

A generic reconfigurable platform will essentially have a set of processing elements (PEs), a set of physical memories, and an interconnection network for communication between various PEs and memories. These are the relevant and significant parts of the RC board and hence discussed here.

#### 1. Processing Element (PE)

A processing element is the FPGA device present on an RC. It provides the computational power to the RC. A PE has limitation in the form of **total area** available for implementation of various logic components. Most of the area on a PE is typically consumed by components that are part of the

input design. Some area is also consumed by the components introduced by the memory mapper to implement memory control and arbitration logic. The aim of the synthesis process is to ensure that the total logic area requirements for a device does not exceed the maximum available area on the device.

#### 2. Memory Type

The various physical memories on a RC can be grouped into different clusters on the basis of similarities in some of their *invariant attributes*. Each such group is said to constitute a *memory type*. A memory type should be viewed as a collection of attributes of physical memories rather than that of physical memories themselves. The attributes which are common among elements of a group of memories are given below.

- **local\_pe** is the processing element which is local to the instances of this memory type. Any logic present in the *local\_pe* does not consume any additional routing resources. A fixed connection already exists on the RC between the instances of a memory type and its *local\_pe*. It is preferable to have all the accessing logic of a physical memory in its *local\_pe*.

- **pins\_traversed** is the number of pins which the logic in the local\_pe of this memory type needs to traverse in order to access an instance of this memory type.

- **read\_latency** is the number of clock cycles for which the logic has to wait before it gets the data requested.

- **write\_latency** is the number of clock cycles for which the data must be available at the input port of the memory so that it can be written reliably. The more clock cycles logic has to wait for accessing (read or write) the memory, more will be the overall design latency. It is desirable to use instances of those memory types which have smaller latencies.

- **num\_ports** is the number of ports available on **each** instance of this memory type. The storage space in a physical memory can be accessed through any of these ports in parallel.

- **max\_storage\_bits** is the maximum number of bits of data that can be stored in an instance of this memory type. The mapping tool should ensure that this upper limit on storage space is not exceeded. At the same time, it is desirable to use maximum possible storage space from each instance.

- num\_configurations is the number of different ways in which a port on instance of this memory type can be configured. configuration of a port is the way in which storage space is accessed through that port. It is specified by the (width,depth) pair. Each word of the memory has #width bits and there are total #depth words available for that configuration.

Figure 2.1: Various Features of Memories Available on a RC

- **configuration\_set** is the set of various configurations possible for this memory type. The number of elements in this set is equal to *num\_configurations*. The storage space can be viewed as a rectangle. There is an upper bound on the area of the rectangle. However, the width and depth of the rectangle can be chosen from the available options.

- group\_num is used as an identification for the memory\_type.

- **num\_instances** indicates the total number of elements of this memory type which are available on the board.

Figure 2.1 shows the variations in different features of memories available on the reconfigurable board. Note that memory type 3 and 4 are identical in all respects except the local\_pe.

#### 3. Physical Memories

Physical Memories are the data storage units available on the RC for storing inputs, outputs and intermediate data produced as part of the computation. Each physical memory *logically* belongs to a memory type. Attributes of a physical memory are given below:

**mem\_type\_num** is the identification of the memory type to which this instance belongs.

- instance\_num is the id of a memory instance over all the physical memories available on the board. Note that instance\_num includes instances of all memory types.

- **set\_of\_ports** are the ports which are part of this physical memory. The size of this set is equal to num\_ports of the memory type of this instance.

#### 4. Memory Port

A physical memory instance can have more than one port. All these ports provide access to the same storage space. Data written by one port can be overwritten by another port if care is not taken. Attributes of port are shown below

parent\_instance\_num is the instance\_num of the physical memory on which this port is present.

- **port\_num** is the identification of the port on the parent memory instance. If a physical memory has k ports, port\_num varies from 0 to k-1.

- **selected\_config** is the way in which this port is configured. If the memory type of the parent instance has c configurations, selected\_config can vary from 0 to c-1.

#### 5. Interconnection Network

If parts of a design, mapped to different PEs, communicate with each other, signals have to be routed between the PEs, through the pins. A direct connection may not be available between two PEs and the signal might need to be routed through another PE or through a interconnection device like a *crossbar*. Anything which facilitates *PE-to-PE* communication can be termed as part of the *interconnection network*. In our work, we assume that a direct connection is available between every pair of PE. If a direct path is not available, some pins from an indirect path can be set aside for communication between the PE-PE pair under consideration. This capacity is not considered for PEs which lie on the path. This assumption can be alleviated by integrating the tool with a smart board-level router. Since routing for generic board architectures is not the focus of this thesis, we simplify our framework without losing any important aspect of the problem under focus. A generic board router is presented in [24].

## 2.2 Input Design

A Unified Specification Model (USM) is presented in [13]. It identifies four main components of an input design. We use these definitions for input design. They are presented here for convenience.

#### 1. Compute Tasks

As the name suggests, the computational part of the design is done by *compute tasks*. They are synthesized into logic and mapped onto PEs. Each node is assumed to be the smallest unit of logic which can not be broken further. In the rest of this thesis, we will use the words Compute Task and Task interchangeably. Attributes of a compute task listed below

**area** represents the estimated size of the compute task. Note that the *area* is some multiple of the smallest measurable unit of area on the target devices, e.g. for a Xilinx Virtex FPGA, the smallest unit is a *Slice*. Thus, area of a task will change if the PE device in the target architecture changes.

**pe\_num** is the PE element on which this compute\_task will finally be mapped.

#### 2. Logical Memory

A logical memory can be defined as a set of data in the design which can be grouped together and abstracted into one component. The grouping is not on the basis of size but on the basis of the role played by the component in the design, e.g each data structure declared by user in High-Level specification of the design can form a logical memory. For this work, we assume that logical memories have already been formed. A logical memory task has the following attributes

depth represents the number of words present in the memory task.

width represents the number of bits per word.

- num\_reads indicates how many reads are performed on the logical memory during the run of the

design

- num\_writes indicates how many writes are performed on the logical memory during the run of the design. A heavily accessed memory has a greater influence on the overall latency of the design. This information can be of great help in producing good quality mapping. If this information is not available, both *num\_reads* and *num\_writes* are assumed to be equal to the *depth* of the design.

- **Mapping** for a memory task is a detailed specification of how and to which physical memory or memories it is assigned. We define mapping in more details later in the thesis.

Accessing\_compute\_task is a list of all the compute tasks which access this logical memory atleast once.

#### 3. Channels

Channels represent direct communication between *compute tasks*. The attributes of a channel include **writer\_task, reader\_task**, and **width**. If the writer and reader tasks are mapped onto different PEs, the channel will consume routing resources.

#### 4. Flags

Flags can be considered as single bit channels used to synchronize the execution of tasks. The attributes of a flag are **writer\_task** and **list\_reader\_task**.

For a detailed discussion, interested readers are referred to [13].

## 2.3 Tabu Search

Tabu Search (TS), was introduced by Fred Glover et al. [9]. It is a general purpose *meta-heuristic* for solving combinatorial optimization problems. It guides a local heuristic search procedure to explore the solution space beyond local optimality. One of the main components of TS is its use of adaptive memory, which creates a more flexible search behavior. Memory-based strategies are therefore the hallmark of tabu search approaches.

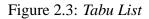

Figure 2.3 gives the outline of the Tabu Search Algorithm (as given in "Iterative Computer Algorithms with Applications in Engineering" by Sait and Youssef, 1999, IEEE Computer Society) [25]. The procedure starts from an initial feasible solution S (current solution) in the search space  $\Omega$ . A neighborhood  $\aleph(S)$  is defined for each S. A sample of neighbor solutions  $V^* \subset \aleph(S)$  is generated, called *trial solutions* ( $|V^*| =$  $\mathbf{n} \ll |\aleph(S)|$ ). From these trial solutions, the best solution, say  $S^* \in V^*$ , is chosen for consideration as the next solution. The move to  $S^*$  is considered even if  $S^*$  is worse than S, that is,  $Cost(S^*) > Cost(S)$ . It is this feature that enables escaping from local optima.

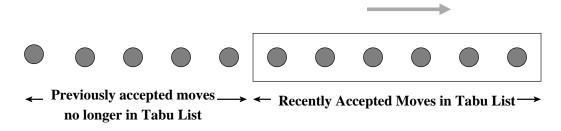

However, it is possible that the search reaches a local minima, ascends (by accepting moves to lower quality solutions), and then return back to the same local optimum, a phenomenon called *cycling*. To prevent this, a list called **tabu list** is maintained. Only selected move attributes are stored in the tabu list, since completely storing previously visited solutions, and comparing them with newly generated ones would be expensive in terms of both computation time and memory requirements. The tabu list can be visualized as a window on accepted moves, as shown in Figure 2.3. Based on the tabu (forbidden) attributes in this list, moves which tend to undo recently made moves are identified and are not accepted.

#### Algorithm Tabu\_Search();

```

\Omega: Set of feasible solutions.

S: Current Solution.

S*: Best admissible solution.

Cost: Objective function.

\Re(S): Neighborhood of S \in \Omega.

```

$V^*$ : Sample of neighborhood solutions.

**T** : Tabu list.

**AL** : Aspiration Level.

## Begin

Start with an initial feasible solution  $S \in \Omega$ ; Initialize tabu lists and aspiration level; For fixed number of iterations Do Generate neighbor solutions  $V^* \subset \aleph(S)$ ; Find best  $S^* \in \mathbf{V}^*$ ; If move S to  $S^* \notin \mathbf{T}$  Then Accept move and update best solution; Update tabu list and aspiration level; Increment iteration number; Else If  $Cost(S^*) < AL$  Then Accept move and update best solution; Update tabu list and aspiration level; Increment iteration number; Endif Endif EndFor End

Figure 2.2: Tabu Search Algorithm

Since tabu list has only some of the attributes of a move, it may also forbid moves to attractive *unvisited* solutions. The notion of *aspiration criterion* helps to relax the actions of the tabu list and overrule the tabu status of moves in certain situations. It temporarily overrides the tabu status if the move is sufficiently good. It must ensure that overriding the tabu status leads the search to an unvisited solution.

In Section 2.4, we discuss usage of long-term and intermediate-term memories for the memory mapping problem.

# 2.4 Tabu Search Enhancements for Memory Synthesis

Any search heuristic is very sensitive to the manner in which its features are exploited. In this section, we present more details into the various techniques adapted for *Tabu Search*.

## 1. Neighborhood Moves

Since neighborhood space is totally random, we make random choices to select neighbors of the current solution. We randomly pick out a small number of logical memories (LM). While retaining the mapping for the unselected LMs, we re-map the picked out LMs using the algorithm described in Section 3.5.

#### 2. Tabu Attributes of a Move

Once a move has been made, we store two attributes for each of the LMs re-mapped. If *l* is one of the LM that was moved, we store *from\_bank* i.e. the memory type to which *l* was mapped in the previous solution. Second is the *to\_bank* i.e. the memory type to which *l* is mapped after the move. A move which contemplates to re-map *l* from the *to\_bank* or to the *from\_bank* (i.e. a move which undoes a recently made move) will be tabued for next few iterations, called the *tabu tenure*. This contemplated move can still be made if it can override the tabu status by satisfying the *aspiration criterion*.

#### 3. Tabu Tenure

Tabu Tenure is nothing but the length of the tabu list. This is the number of iterations for which a move is kept tabu active. Search is highly sensitive to this parameter. Ideally, this parameter should depend on the problem size, and the type of attributes which are tabued. However, to make it independent of the problem size, we use a varying tabu tenure, between 4 and 9. New tabu tenure is randomly picked from this range after every  $2 \times curr\_tabu\_tenure$  moves have been made. This has shown to give good results for different sizes of problems.

#### 4. Aspiration Criterion

We use *Global Aspiration by Objective*. If the contemplated move has a value better than the best value seen so far, it indicates that the search has not visited this solution before, thus acceptance of this move is not leading to *cycling*.

#### 5. Residence Frequency

This is a long-term memory of the tabu search. It is a 2-dim array of size  $\#LM \times \#Memory\_Types$ , where each element indicates the total period for which the LM was mapped to that bank type. It is an indication of the suitability of mapping the LM to that bank type. If the search is in a region of high quality solutions, a hight residence frequency represents a desirable LM-bank\_type combination. By rewarding a high residence frequency, the search can focus on those solutions which have the good combination of LM-bank\_type. This can lead to *intensification* of the search leading to better solutions. Similarly, in the region of poor quality solutions, a high residence frequency represents a poor LM-bank\_type combination. By penalizing a high residence frequency, the search requency represents a poor LM-bank\_type combination. By penalizing a high residence frequency, the search requency is a poor LM-bank\_type combination. By penalizing a high residence frequency memory frequency is a poor LM-bank\_type combination. By penalizing a high residence frequency, the search requency is a poor LM-bank\_type combination. By penalizing a high residence frequency, the search can be forced to move away from such solutions leading to *diversification* of search, exploring new regions in solution space.

#### 6. Transition Frequency

This is another form of long-term memory. It is a *1-dim* array of size #LMs. Each element holds value equal to the number of moves which re-mapped that LM from one bank type to another. A higher value shows that those moves contemplating re-mapping this LM were readily accepted. LMs with high transition frequency generally are smaller in size and easily *fit* many bank types. A high transition frequency indicates *fine-tuning* moves, which do not change the solution by a great extent but cause localized search. This can be suitably rewarded or penalized to *intensify* or *diversify* the search.

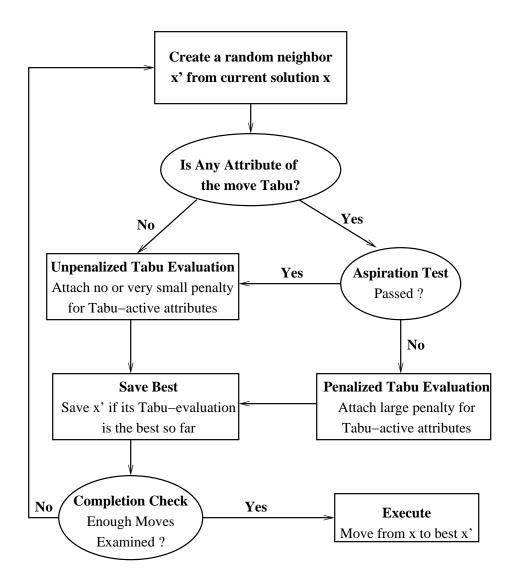

#### 7. Weighted Tabu Evaluation

The simple version of tabu search picks up the best neighbor based solely on the cost calculated

Figure 2.4: Flow Chart for Weighted Tabu Evaluation

by solution attributes. However, a modified cost function can also take into account the long term memory attributes of the move. The neighbor having best weight is chosen and tested for tabu status. Figure 2.4 shows the flowchart for weighted tabu evaluation.

$Weigh(next\_solution) = func(solution\_cost, transfreq, resifreq)$

#### 8. Restart

This is a form of medium term memory. The solution space for memory mapping can be pictured to be divided into regions. Solutions within a region have similar characteristics. Small changes obtained by re-mapping a few LMs will not lead to significant change in the solution quality. After a fixed number of iterations, an average cost of all the solutions explored in the current region so far is calculated in every iteration and examined. It can be used to judge whether further exploration of the current region will lead to a better solution or not. If this average cost is significantly higher than the cost of best solution found so far, chances of finding a new best solution in this region are very small. Then a new random solution is generated. This solution is compared with representative solutions from other regions to ensure that the search is conducted in a new region. This technique is specially useful in cases where it is difficult to find even a constraint satisfying solution. Every time the search is restarted, all the other short and long term memories are reset.

#### 9. Probabilistic Tabu Search

We explained the idea of performing a weighted tabu search earlier. There, we suggested to pick the solution with best weight. Another technique suggested in literature is to use these weights as relative probabilities of each solution. A solution with higher weight will have higher chances of being chosen. The basic idea is to introduce more randomness into the search as a hedge against risks of being too greedy. However, for memory mapping, we found that the quality of search, in terms of both time to find solution and the quality of solution itself, significantly **deteriorated**. Since introduction of probabilities reduces the localized greedy nature of tabu search, the ability to find solutions quickly is reduced. This technique might become helpful when the search needs to continue over a very long period. Our approach has randomization in choosing candidates from the neighborhood. *Restart* also provides a way of visiting new solution regions.

$probability\_acceptance \propto Weight(contemplated\_solution)$

### 2.5 Discussion and Summary

Meta-heuristic techniques have been classified as evolutionary methods and adaptive memory strategies. Evolutionary techniques manipulate a collection of solutions rather than a single solution at each stage. *Genetic Algorithm (GA)* is an example of such technique. *Simulated Annealing (SA)* is somewhat similar to TS in the way that both manipulate only one solution at a time. Our initial comparison between SA and TS showed that even basic TS outperformed SA in most cases. The basic TS implementation did not include any of the search enhancing techniques which can potentially make TS more powerful. Thus we decided to choose TS over SA.

In this chapter, we introduced the common terminologies used in the thesis. We introduced terms related to the target RC architecture. We introduced the essential components required to specify the input design,

namely *compute\_task* and *memory\_task*. We also discussed about what constitutes a mapping for each type of task.

We described the basic Tabu Search algorithm, which is the main driving algorithm used in our approach. The details about adapting the TS to the given problem is also presented here.

# Chapter 3

# **Memory Synthesis**

This chapter deals with the issues and algorithms for memory synthesis problem targeted towards FPGA based Reconfigurable Computers (RC). In Section 3.1, we present the details of the input specification and its variations accepted by the memory mapper. The details for mapping of a logical memory and formulation of the problem are presented in Section 3.2 and 3.3 respectively. Section 3.4 shows a model of logical memory used by the tool while performing mapping. Section 3.5 presents a heuristic mapping algorithm, called *Rectangle Carving*. This heuristic effectively makes use of the memory model. The tabu search is used to guide this heuristic.

After the memory mapping stage, the second stage in memory synthesis is control logic generation. This is discussed in Section 3.6. Section 3.7 presents the two different categories of constraints faced by the algorithm and their effect on the quality of result produced. Section 3.8 presents various factors which the algorithm tries to optimize to achieve better quality results. Experimental results are discussed in Section 3.9. Finally, in Section 3.10, we present conclusions and summary of observations.

# 3.1 Design and Architecture Specification

In Section 2.2, we have introduced four components, namely, compute tasks, logical memory, channels, and flags. However, as far as memory synthesis is concerned, we need to consider only logical memories. Later in this section, we will state how memory mapper can indirectly take the other factors into consideration.

The design specification input is a *set* of *logical\_memories* which are to be mapped onto the target architecture. Except *accessing\_tasks*, all other attributes of a *logical\_memory* are considered. The target architecture specification includes a *set* of *memory\_types*. Except *local\_pe*, all the attributes associated

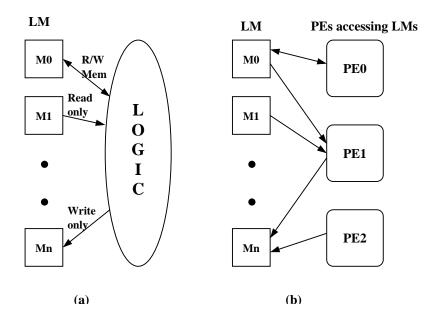

Figure 3.1: Design Specifications with and without logic partitioning information

with a *memory\_type* are provided as input. In the absence of any information from logic partitioner, information regarding *accessing\_tasks* and *local\_pe* can not be utilized. We assume that there is only one PE. All *memory\_types* are local to it and all *compute\_tasks* are present in this *PE*. This is shown in Figure 3.1 (a).

If information from logic partitioning is available in the form of which *compute\_task* is assigned to which PE, the memory mapper can also take this input. For each *logical\_memory*, there will be information about the PEs in which its accessing *compute\_tasks* are present. Memory mapper does not need to know any other details of the *compute\_tasks*. Alternatively, it can directly take the output of the logic partitioner as input, in which there are complete details about the compute\_tasks. The memory mapper can extract the information about which PEs are accessing a logical\_memory depending upon where its accessing compute\_tasks are placed. The architecture specification will need to specify the following additional information:

- number of FPGAs on the RC.

- local\_pe for each memory\_type.

- number of interconnection lines available between each PE-PE pair.

Figure 3.1 (b) shows the second forms of design input accepted by the memory mapper.

## 3.2 Mapping Definitions

A *Logical Memory* can be divided in an arbitrary manner across multiple instances of physical memories and multiple ports. If the logical memory is *split*, mapping should specify which part of the logical memory is mapped to which instance and port. We view a logical memory as a *rectangle*. We call this the *complete rectangle*. If split, the complete rectangle can be decomposed into *sub-rectangles*. A mapped sub-rectangle is specified by a tuple of 6 values described below.

physical\_mem\_num specifies the physical instance to which this sub-rectangle has been mapped.

port\_num specifies which port of that physical instance will be used to access this sub-rectangle.

depth and width are the dimensions of the sub-rectangle.

start\_depth and start\_width define the top-left corner of the sub-rectangle with respect to the complete

rectangle.

We define a mapping to be a set of sub-rectangles, one corresponding to each part into which the logical memory has been split.

$mapping = {subrect_1, subrect_2, subrect_3, \dots, subrect_N}$

In the best case scenario, the logical memory will not be split and there will be only one sub-rectangle. The *start\_depth* and *start\_width* of the only sub-rectangle will both be 0. The *depth* and *width* will be equal to that of the logical memory itself.

**Validity :** For a mapping to be valid, we require that all sub-rectangles of the mapping be mapped to physical instances of **same memory\_type**. We further require that no two sub-rectangles in a mapping share the same port.

**Justification :** Consider a scenario in which different parts of a logical memory are mapped to two physical memories whose *local\_pes* are not same. The address and data buses will need to be routed to both the PEs. This can greatly deteriorate the quality of the solution. Even if the *local\_pe* of the physical memories are same, they might differ in read and/or write latencies. If the width of the logical memory is split, a read operation will present different bits of the same word in different clock cycles. In this case, the accessing logic will have to change depending on which part of the logical memory is mapped to which physical instance. Our assumption excludes all such scenario from a valid solution. This leads to reduction in solution space without deterioration in the quality of the solution produced.

## 3.3 **Problem Definition**

Given

- Set  $\mathcal{L} = \{l : logical\_memory\}$ , where each  $l \in \mathcal{L}$  has the attributes specified in Section 2.2.  $\mathcal{L}$  specifies the input design.

- Set T = {t : memory\_type}, where each t ∈ T has attributes specified in Section 2.1. T is part of the target architecture.

- set  $\mathcal{P} = \{pm : physical\_mem\_instances | \forall pm : \exists_1 t \in \mathcal{T}\}$ . The physical\\_mem\\_instance is as specified in Section 2.1

- If logic partition information is available, the target architecture specification will also include  $num_fpgas$  and set  $\mathcal{I} = \{i_{f_1f_2} | 0 \leq f_1, f_2 < num_fpgas\}$ . Each element of  $\mathcal{I}$  specifies the number of interconnect pins available between the corresponding fpga pair.

The objective of the memory mapper is to produce another set

$\mathcal{M} = \{m : memory\_mapping | \forall l \in \mathcal{L}, \exists_1 l \leftrightarrow m \}$

such that

$\{ \forall pm \in \mathcal{P}, \ satisfies(Constraints_{pm}) \}$

## 3.4 Modeling of Logical Memory as a Rectangle

One of the essential features of a logical memory which we try to capture is its size. Size is a dominating factor in deciding the destination of a LM on the RC.

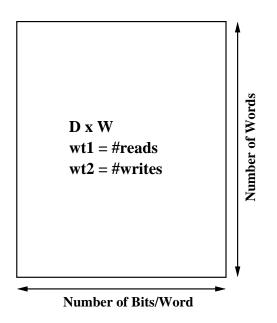

Figure 3.2 shows a model of a LM. The number of words of the logical memory is modeled as depth of a *rectangle* while the number of bits per word is represented by width of the *rectangle*. The weight of a rectangle is the number of times the LM is accessed in the design. If this information is lacking, we assume it to be equal to the number of words in the LM.

The aim is to map all parts of this rectangle to some physical memory on the RC. A good mapper should try to map the complete rectangle onto single physical instance. The splitting of LM over multiple physical

Figure 3.2: Rectangle Model for A Logical Memory

instances is indicated by the splitting of the rectangle into various sub-rectangles, each part mapped to a single physical port.

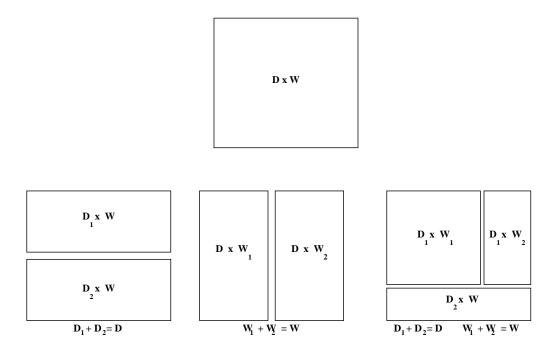

Figure 3.3 shows various ways in which a rectangle can be split. Rectangles might be split depth-wise if the physical instances are not deep enough, or they may be split width-wise if the ports are not wide enough to accommodate the complete width. Larger LMs might be split both ways. If after splitting, a sub-rectangle still does not fit the physical instance, it will be further split until all parts have been completely mapped.

## 3.5 Heuristic : Rectangle Carving

In Section 3.4, we presented how a logical memory is represented. In this section, we show how this representation is used in the mapping algorithm.

At every iteration, the Tabu Search contemplates a move which re-maps some of the logical memories to new physical banks. While Tabu Search decides which LMs to be re-mapped and to which memory type they should be re-mapped, the new mapping for LM is found by a lower level heuristic. The heuristic, which we call **Rectangle Carving**, efficiently makes use of the rectangle model of a logical memory. It takes as input the logical memory to be mapped and the physical bank to which it has to be mapped and returns a mapping of the LM for that memory type.

Figure 3.3: Possible Sub-rectangles for a Rectangle

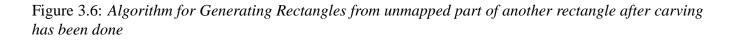

The algorithm reads in the logical memory as a rectangle. It maintains a list of rectangles which are to be mapped. This list is initialized with the rectangle corresponding to the LM being mapped. The algorithm maps each rectangle in this list, one at a time. New rectangles are created out of the unmapped part of this rectangle and appended to the list.

In each iteration, the algorithm tries to map the first rectangle in the list. It randomly picks one of the instances in the physical bank and then one of the ports of that instance.

**port\_usable** performs a check to see if this port has already been assigned to some other sub-rectangle, either of same or different logical memory. If port sharing between various sub-rectangles is permissible, *port\_usable* returns *true* indicating that this port can be used to map the rectangle under consideration.

**Carve\_rectangle** considers a *subset of configurations* of this port and calculates a fitness value of mapping the rectangle to each configuration. The fitness depends upon how much of the rectangle was mapped, whether the rectangle had to be split width-wise of depth-wise and how much storage space would go to waste (for configurations where width of the rectangle is less than that of the configuration). We put a higher penalty if rectangle has to be split width-wise. The fitness function has following factors.

$pct\_depth = assigned\_depth/rect\_depth$

$pct\_width = assigned\_width/rect\_width$

```

Algorithm: Map_LM

Input:

\mathcal{M}: Logical Memory

\mathcal{B} : Bank Type

Output:

S: Solution, a set of mapping to ports

begin

C, \mathcal{R}, \mathcal{N}: Rectangle

\mathcal{L}:List of Rectangles to map

\mathcal{P}: Physical Port

\mathcal{U}, \mathcal{FORCE}:Bool

\mathcal{R} \leftarrow Rectangle(\mathcal{M}.depth, \mathcal{M}.width);

\mathcal{S} \leftarrow \emptyset;

\mathcal{L} \leftarrow [\mathcal{R}];

/*initialize \mathcal L with the rectangle corresponding to \mathcal M */

while (\mathcal{L} \neq \emptyset) loop

\mathcal{R} \leftarrow \mathcal{L}.first();

\mathcal{P} \leftarrow random\_port(\mathcal{B});

\mathcal{U} \leftarrow \mathbf{port\_usable}(\mathcal{P}, \mathcal{M});

\mathcal{FORCE} \leftarrow (max\_fails\_reached);

\mathcal{C} \leftarrow \mathbf{carve\_rectangle}(\mathcal{R}, \mathcal{P}, \mathcal{FORCE});

if (\mathcal{FORCE} \text{ or } (is\_valid(\mathcal{C}) \text{ and } \mathcal{U})) then

add_new_subrect (\mathcal{R}, \mathcal{C}, \mathcal{L});

\mathcal{L} \leftarrow \mathcal{L} - [\mathcal{R}];

\mathcal{S} \leftarrow \mathcal{S} \cup \{\mathcal{C}\};

end if

end while

end

```

Figure 3.4: Algorithm for Mapping a Logical Memory

#### Algorithm: Carve\_Rectangle

#### Input:

R :Rectangle to map

P :Physical Port

FORCE :Bool

/\*indicates if mapping to be done forcefully\*/

## **Output:**

C :Rectangle /\* Carved from R such that it can be mapped onto P \*/

#### begin

*Fitness* : Array of fitness, one value for each configuration  $\mathcal{N}$  : A subset of Port Configurations

$\mathcal{N} \leftarrow \{n | n \in Configurations of \mathcal{P} \land n.width \geq \mathcal{P}.curr\_config.width\}$

## for each $(n \in \mathcal{N})$ loop

$get\_assignable\_rect(\mathcal{R}, \mathcal{P}, n);$ Fitness<sub>n</sub>  $\leftarrow$  **func**(assignable\\_depth, assignable\\_width, \mathcal{R}); save\\_best\\_assignable\\_rectangle();

## end for

```

if (BestFitness > 0) then

C \leftarrow Rectangle(best\_assignable\_depth, best\_assignable\_width);

```

```

\mathcal{P}.curr\_config \leftarrow best\_config;

```

#### else

end

```

/* Failed to carve out a rectangle */

if (\mathcal{FORCE}) then

/* Forcefully assign \mathcal{R} to \mathcal{C} */

\mathcal{C} \leftarrow \mathcal{R};

else

/* Try in future iterations */

\mathcal{C} \leftarrow \mathcal{NULL};

end if

end if

```

## Algorithm: add\_new\_subrect

**Input:**

$C, \mathcal{R}$ : Rectangle  $\mathcal{L}$ :List of Rectangles to map **Output:**  $\mathcal{L}$ :Modified List of Rectangles to map begin  $\mathcal{N}$ : Rectangle, newly created to append to L if  $(C.width < \mathcal{R}.width)$  then  $\mathcal{N} \leftarrow \text{Rectangle} (\mathcal{C}.depth, \mathcal{R}.width - \mathcal{C}.width);$  $\mathcal{L} \leftarrow \mathcal{L} \cup [\mathcal{N}];$ end if: if  $(C.depth < \mathcal{R}.depth)$  then  $\mathcal{N} \leftarrow \text{Rectangle} (\mathcal{R}.depth - \mathcal{C}.depth, \mathcal{R}.width);$  $\mathcal{L} \leftarrow \mathcal{L} \cup [\mathcal{N}];$ end if; end

Figure 3.7: Rectangle Carving Process

$bits\_waste = (config\_width - assigned\_width) * assigned\_depth$