# Verification of Binarized Neural Networks via Inter-Neuron Factoring

Chih-Hong Cheng, Georg Nührenberg, Chung-Hao Huang, and Harald Ruess

fortiss - Landesforschungsinstitut des Freistaats Bayern Guerickestr. 25, 80805 Munich, Germany {cheng,nuehrenberg,huang,ruess}@fortiss.org

Abstract. We study the problem of formal verification of Binarized Neural Networks (BNN), which have recently been proposed as a energy-efficient alternative to traditional learning networks. The verification of BNNs, using the reduction to hardware verification, can be even more scalable by factoring computations among neurons within the same layer. By proving the NP-hardness of finding optimal factoring as well as the hardness of PTAS approximability, we design polynomial-time search heuristics to generate factoring solutions. The overall framework allows applying verification techniques to moderately-sized BNNs for embedded devices with thousands of neurons and inputs.

**Key words:** hardware verification, artificial neural networks, formal methods, safety

## 1 Introduction

Artificial neural networks have become essential building blocks in realizing many automated and even autonomous systems. They have successfully been deployed, for example, for perception and scene understanding [17, 21, 26], for control and decision making [7, 14, 19, 29], and also for end-to-end solutions of autonomous driving scenarios [5]. Implementations of artificial neural networks, however, need to be made much more power-efficient in order to deploy them on typical embedded devices with their characteristically limited resources and power constraints. Moreover, the use of neural networks in safety-critical systems poses severe verification and certification challenges [3].

Binarized Neural Networks (BNN) have recently been proposed [9, 16] as a potentially much more power-efficient alternative to more traditional feed-forward artificial neural networks. Their main characteristics are that trained weights, inputs, intermediate signals and outputs, and also activation constraints are binary-valued. Consequently, forward propagation only relies on bit-level arithmetic. Since BNNs have also demonstrated good performance on standard datasets in image recognition such as MNIST, CIFAR-10 and SVHN [9], they are an attractive and potentially power-efficient alternative to current floating-point based implementations of neural networks for embedded applications.

In this paper we study the verification problem for BNNs. Given a trained BNN and a specification of its intended input-output behavior, we develop verification procedures for establishing that the given BNN indeed meets its intended specification for all possible inputs. Notice that naively solving verification problems for BNNs with, say, 1000 inputs requires investigation of all  $2^{1000}$  different input configurations.

For solving the verification problem of BNNs we build on well-known methods and tools from the hardware verification domain. We first transform the BNN and its specification into a *combinational miter* [6], which is then transformed into a corresponding propositional satisfiability (SAT) problem. In this process we rely heavily on logic synthesis tools such as ABC [6] from the hardware verification domain. Using such a direct neuron-to-circuit encoding, however, we were not able to verify BNNs with thousands of inputs and hidden nodes, as encountered in some of our embedded systems case studies. The main challenge therefore is to make the basic verification procedure scale to BNNs as used on current embedded devices.

It turns out that one critical ingredient for efficient BNN verification is to factor computations among neurons in the same layer, which is possible due to weights being binary. Such a technique is not applicable within recent works in verification of floating point neural networks [8, 10, 15, 20, 25]. The key theorem regarding the hardness of finding optimal factoring as well as the hardness of inapproximability leads to the design of polynomial time search heuristics for generating factorings. These factorings substantially increase the scalability of formal verification via SAT solving.

The paper is structured as follows. Section 2 defines basic notions and concepts underlying BNNs. Section 3 presents our verification workflow including the factoring of counting units (Section 3.2). We summarize experimental results with our verification procedure in Section 4, compare our results with related work from the literature in Section 5, and we close with some final remarks and an outlook in Section 6. Proofs of theorems are listed in the appendix.

#### 2 Preliminaries

Let  $\mathbb{B}$  be the set of bipolar binaries  $\pm 1$ , where +1 is interpreted as true and -1 as false. A Binarized Neural Network (BNN) [9,16] consists of a sequence of layers labeled from  $l=0,1,\ldots,L$ , where 0 is the index of the input layer, L is the output layer, and all other layers are so-called hidden layers. Superscripts  $^{(l)}$  are used to index layer l-specific variables. Elements of both inputs and outputs vectors of a BNN are of bipolar domain  $\mathbb{B}$ .

Layers l are comprised of nodes  $n_i^{(l)}$  (so-called neurons), for  $i=0,1,\ldots,d^{(l)}$ , where  $d^{(l)}$  is the dimension of the layer l. By convention,  $n_0^{(l)}$  is a bias node and has constant bipolar output +1. Nodes  $n_j^{(l-1)}$  of layer l-1 can be connected with nodes  $n_i^{(l)}$  in layer l by a directed edge of weight  $w_{ji}^{(l)} \in \mathbb{B}$ . A layer is fully connected if every node (apart from the bias node) in the layer is connected to all

| index j                                                  | 0 (bias node)                             | 1  | 2  | 3  | 4  |  |  |

|----------------------------------------------------------|-------------------------------------------|----|----|----|----|--|--|

| $x_j^{(l-1)}$                                            | +1 (constant)                             | +1 | -1 | +1 | +1 |  |  |

| $w_{ji}^{(l)}$                                           | -1 (bias)                                 | +1 | -1 | -1 | +1 |  |  |

| $x_{j}^{(l-1)}w_{ji}^{(l)}$                              | -1                                        | +1 | +1 | -1 | +1 |  |  |

| $ im_i^{(l)} $                                           | (-1) + (+1) + (+1) + (-1) + (+1) = 1      |    |    |    |    |  |  |

| $x_i^{(l)}$                                              | $+1$ , as $im_i^{(l)} > 0$                |    |    |    |    |  |  |

| index j                                                  | 0 (bias node)                             | 1  | 2  | 3  | 4  |  |  |

| $x_j^{(l-1)}$                                            | 1                                         | 1  | 0  | 1  | 1  |  |  |

| $w_{ji}^{(l)}$                                           | 0 (bias)                                  | 1  | 0  | 0  | 1  |  |  |

| $x_j^{(l-1)} \overline{\oplus} w_{ji}^{(l)}$             | 0                                         | 1  | 1  | 0  | 1  |  |  |

| # of 1's in $x_j^{(l-1)} \overline{\oplus} w_{ji}^{(l)}$ | 3                                         |    |    |    |    |  |  |

| $ x_i^{(l)} $                                            | 1, as $(3 \ge \lceil \frac{5}{2} \rceil)$ |    |    |    |    |  |  |

**Table 1.** An example of computing the output of a BNN neuron, using bipolar domain (up) and using 0/1 boolean variables (down).

neurons in the previous layer. Let  $\boldsymbol{w}_i^{(l)}$  denote the array of all weights associated with neuron  $n_i^{(l)}$ . Notice that we consider all weights in a network to have fixed bipolar values.

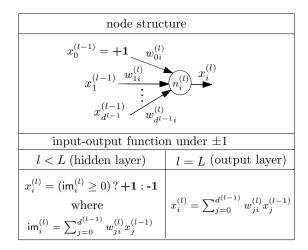

Given an input to the network, computations are applied successively from neurons in layer 1 to L for generating outputs. Fig. 1 illustrates the computations of a neuron in bipolar domain. Overall, the activation function is applied to the intermediately computed weighted sum. It outputs +1 if the weighted sum is greater or equal to 0; otherwise, output -1. For the output layer, the activation function is omitted. For  $l=1,\ldots,L$  let  $x_i^{(l)}$  denote the output value of node  $n_i^{(l)}$  and  $\boldsymbol{x}^{(l)} \in \mathbb{B}^{|d^{(l)}|+1}$  denotes the array of all outputs from layer l, including the constant bias node;  $\boldsymbol{x}^{(0)}$  refers to the input layer.

For a given BNN and a relation  $\phi_{risk}$  specifying the undesired property between the bipolar input and output domains of the given BNN, the BNN safety verification problem asks if there exists an input  $\boldsymbol{a}$  to the BNN such that the risk property  $\phi_{risk}(\boldsymbol{a}, \boldsymbol{b})$  holds, where  $\boldsymbol{b}$  is the output of the BNN for input  $\boldsymbol{a}$ .

It turns out that safety verification of BNN is no simpler than safety verification of floating point neural networks with ReLU activation function [15]. Nevertheless, compared to floating point neural networks, the simplicity of binarized weights allows an efficient translation into SAT problems, as can be seen in later sections.

**Theorem 1.** The problem of BNN safety verification is NP-complete.

## 3 Verification of BNNs via Hardware Verification

The BNN verification problem is encoded by means of a *combinational miter* [6], which is a hardware circuit with only one Boolean output and the output should

**Fig. 1.** Computation inside a neuron of a BNN, under bipolar domain  $\pm 1$ .

always be 0. The main step of this encoding is to replace the bipolar domain operation in the definition of BNNs with corresponding operations in the 0/1 Boolean domain.

We recall the encoding of the update function of an individual neuron of a BNN in bipolar domain (Eq. 1) by means of operations in the 0/1 Boolean domain [9,16]: (1) perform a bitwise XNOR ( $\oplus$ ) operation, (2) count the number of 1s, and (3) check if the sum is greater than or equal to the half of the number of inputs being connected. Table 1 illustrates the concept by providing the detailed computation for a neuron connected to five predecessor nodes. Therefore, the update function of a BNN neuron (in the fully connected layer) in the Boolean domain is as follows.

$$x_i^{(l)} = \operatorname{geq}_{\left\lceil \frac{|\boldsymbol{d}^{(l-1)}|+1}{2} \right\rceil}(\operatorname{count1}(\boldsymbol{w}_i^{(l)} \ \overline{\oplus} \ \boldsymbol{x}^{(l-1)})) \ , \tag{1}$$

where count1 simply counts the number of 1s in an array of Boolean variables, and  $\gcd_{\left\lceil \frac{|d^{(l-1)}|+1}{2}\right\rceil}(x)$  is 1 if  $x\geq \left\lceil \frac{|d^{(l-1)}|+1}{2}\right\rceil$ , and 0 otherwise. Notice that the value  $\left\lceil \frac{|d^{(l-1)}|+1}{2}\right\rceil$  is constant for a given BNN. Specifications in the bipolar domain can also be easily re-encoded in the

Specifications in the bipolar domain can also be easily re-encoded in the Boolean domain. Let  $(x_i^{(L)})_{\pm 1}$  be the valuation in the bipolar domain and  $(x_i^{(L)})_{0/1}$  be the output valuation in the Boolean domain; then the transformation from bipolar to Boolean domain is as follows.

$$(x_i^{(L)})_{+1} = 2 \cdot (x_i^{(L)})_{0/1} - d^{(L-1)}$$

(2)

An illustrative example is provided in Table 1, where  $\mathsf{im}_i^{(l)} = 1 = 2 \cdot 3 - 5$ . In the remaining of this paper we assume that properties are always provided in the Boolean domain.

#### 3.1 From BNN to hardware verification

We are now ready for stating the basic decision procedure for solving BNN verification problems. This procedure first constructs a combinational miter for a BNN verification problem, followed by an encoding of the combinational miter into a corresponding propositional SAT problem. Here we rely on standard transformation techniques as implemented in logic synthesis tools such as ABC [6] or Yosys [30] for constructing SAT problems from miters. The decision procedure takes as input a BNN network description, an input-output specification  $\phi_{risk}$  and can be summarized by the following workflow:

- 1. Transform all neurons of the given BNN into neuron-modules. All neuron-modules have identical structure, but only differ based on the associated weights and biases of the corresponding neurons.

- 2. Create a BNN-module by wiring the neuron-modules realizing the topological structure of the given BNN.

- 3. Create a property-module for the property  $\phi_{risk}$ . Connect the inputs of this module with all the inputs and all the outputs of the BNN-module. The output of this module is true if the property is satisfied and false otherwise.

- 4. The combination of the BNN-module and the property-module is the miter.

- 5. Transform the miter into a propositional SAT formula.

- 6. Solve the SAT formula. If it is unsatisfiable then the BNN is safe w.r.t.  $\phi_{risk}$ ; if it is satisfiable then the BNN exhibits the risky behavior being specified in  $\phi_{risk}$ .

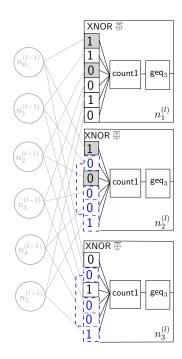

#### 3.2 Counting optimization

The goal of the counting optimization is to speed up SAT-solving times by reusing redundant counting units in the circuit and, thus, reducing redundancies in the SAT formula. This method involves the identification and factoring of redundant counting units, illustrated in Figure 2, which highlights one possible factoring. The main idea is to exploit similarities among the weight vectors of neurons in the same layer, because the counting over a portion of the weight vector has the same result for all neurons that share it. The circuit size is reduced by using the factored counting unit in multiple neuron-modules. We define a factoring as follows:

**Definition 1** (factoring and saving). Consider the l-th layer of a BNN where l > 0. A factoring f = (I, J) is a pair of two sets, where  $I \subseteq \{1, \ldots, d^{(l)}\}$ ,  $J \subseteq \{1, \ldots, d^{(l-1)}\}$ , such that |I| > 1, and for all  $i_1, i_2 \in I$ , for all  $j \in J$ , we have  $w_{ji_1}^{(l)} = w_{ji_2}^{(l)}$ . Given a factoring f = (I, J), define its saving sav(f) be  $(|I| - 1) \cdot |J|$ .

**Definition 2** (non-overlapping factorings). Two factorings  $f_1 = (I_1, J_1)$  and  $f_2 = (I_2, J_2)$  are non-overlapping when the following condition folds: if  $(i_1, j_1) \in f_1$  and  $(i_2, j_2) \in f_2$ , then either  $i_1 \neq i_2$  or  $j_1 \neq j_2$ . In other words, weights associated with  $f_1$  and  $f_2$  do not overlap.

Fig. 2. One possible factoring to avoid redundant counting.

**Definition 3** (k-factoring optimization problem). The k-factoring optimization problem searches for a set F of size k factorings  $\{f_1, \ldots, f_k\}$ , such that any two factorings are non-overlapping, and the total saving  $\mathsf{sav}(f_1) + \cdots + \mathsf{sav}(f_k)$  is maximum.

For the example in Fig. 2, there are two non-overlapping factorings  $f_1 = (\{1,2\},\{0,2\})$  and  $f_2 = (\{2,3\},\{1,3,4,5\})$ .  $\{f_1,f_2\}$  is also an optimal solution for the 2-factoring optimization problem, with the total saving being  $(2-1)\cdot 2+(2-1)\cdot 4=6$ . Even finding one factoring  $f_1$  which has the overall maximum saving  $\mathsf{sav}(f_1)$ , is computationally hard. This NP-hardness result is established by a reduction from the NP-complete problem of finding maximum edge biclique in bipartite graphs [24].

**Theorem 2** (Hardness of factoring optimization). The k-factoring optimization problem, even when k = 1, is NP-hard.

Furthermore, even having an approximation algorithm for the k-factoring optimization problem is hard - there is no polynomial time approximation scheme (PTAS), unless NP-complete problems can be solved in randomized subexponential time. The proof follows an intuition that building a PTAS for 1-factoring can be used to build a PTAS for finding maximum complete bipartite subgraph which also has known inapproximability results [1].

## **Algorithm 1:** Finding factoring possibilities for BNN.

Data: BNN network description (cf Sec. 2) **Result:** Set F of factorings, where any two factorings of F are non-overlapping. function main(): let used :=  $\emptyset$  and  $F := \emptyset$ ; 2 **foreach** neuron  $n_i^{(l)}$  do 3 let  $f_i^{opt} := \text{empty factoring};$ 4  $\begin{array}{l} \textbf{foreach} \text{ weight } w_{ji}^{(l)} \text{ where } (i,j) \not\in \textbf{used do} \\ & \left[ f_{ij} = \texttt{getFactoring}(i,j,\textbf{used}); \right. \\ & \left. \textbf{if } \texttt{sav}(f_{ij}) > \texttt{sav}(f_{i}^{opt}) \textbf{ then } f_{i}^{opt} := f_{ij}; \end{array} \right.$ 5 6 7 used := used  $\cup \{(i, j) \mid (i, j) \in f_i^{opt}\}; F := F \cup \{f_i^{opt}\};$ 8 return F; 9 10 function getFactoring(i, j, used): **build**  $\mathbb{I} := \{I_0, ..., I_{d^{(l-1)}}\}$  where  $I_{j'} :=$  $\{i' \in \{0, ..., d^{(l)}\} \mid w_{i'i'}^{(l)} = w_{i'i}^{(l)} \land (i', j') \not\in \text{used}\};$ foreach  $I_m \in \mathbb{I}$  do  $I_m := I_m \cap I_j$ ; 12 build  $\mathbb{J}:=\{J_0,\ldots,J_{j'},\ldots,J_{d^{(l-1)}}\}$  where  $J_{j'}:=$ 13  $\{j'' \in \{0, ..., d^{(l-1)}\} \mid I_{j'} \subseteq I_{j''}\};$  **return**  $(I, J) := (I_{j^*}, J_{j^*})$  where  $I_{j^*} \in \mathbb{I}, J_{j^*} \in \mathbb{J}$ , and 14  $(|I_{j^*}|-1)\cdot |J_{j^*}| = \mathsf{max}_{j'\in\{0,\dots,d^{(l-1)}\}} (|I'_j|-1)\cdot |J'_j| ;$

**Theorem 3.** Let  $\epsilon > 0$  be an arbitrarily small constant. If there is a PTAS for the k-factoring optimization problem, even when k = 1, then there is a (probabilistic) algorithm that decides whether a given SAT instance of size n is satisfiable in time  $2^{n^{\epsilon}}$ .

As finding an optimal factoring is computationally hard, we present a polynomial time heuristic algorithm (Algorithm 1) that finds factoring possibilities among neurons in layer l. The main function searches for an unused pair of neuron i and input j (line 3 and 5), considers a certain set of factorings determined by the subroutine getFactoring (line 6) where weight  $w_{ji}^{(l)}$  is guaranteed to be used (as input parameter i, j), picks the factoring with greatest sav() (line 7) and then adds the factoring greedily and updates the set used (line 8).

The subroutine getFactoring() (lines 10–14) computes a factoring (I,J) guaranteeing that weight  $w_{ji}^{(l)}$  is used. It starts by creating a set  $\mathbb{I}$ , where each element  $I_{j'} \in \mathbb{I}$  is a set containing the indices of neurons whose j'-th weight matches the j'-th weight in neuron i (the condition  $(w_{j'i'}^{(l)} = w_{j'i}^{(l)})$  in line 11). In the example in Fig. 3a, the computation generates Fig. 3b where  $I_3 = \{1,2,3\}$  as  $w_{31}^{(l)} = w_{32}^{(l)} = w_{33}^{(l)} = 0$ . The intersection performed on line 12 guarantees that the set  $I_{j'}$  is always a subset of  $I_j$  – as weight  $w_{ji}$  should be included,  $I_j$  already defines the maximum set of neurons where factoring can happen. E.g.,  $I_3$  changes from  $\{1,2,3\}$  to  $\{1,2\}$  in Fig. 3c.

|      |                        | _                          | $ lap{I}$ after    | π                      |

|------|------------------------|----------------------------|--------------------|------------------------|

| inde | ex                     | 1                          | intersecting $I_0$ | J                      |

| 0    | 1 1                    | $\boxed{0} \qquad \{1,2\}$ | $\{1, 2\}$         | $\{0, 2, 3\}$          |

| 1    | 1 0                    | 0 {1}                      | {1}                | $\{0, 1, 2, 3, 4, 5\}$ |

| 2    | 0 0                    | $1 $ $\{1,2\}$             | $\{1, 2\}$         | $\{0, 2, 3\}$          |

| 3    | 0 0                    | $0$ {1, 2, 3}              | $\{1,2\}$          | $\{0, 2, 3\}$          |

| 4    | 1 0                    | 0 {1}                      | {1}                | $\{0, 1, 2, 3, 4, 5\}$ |

| 5    | 0 1                    | 1 {1}                      | {1}                | $\{0, 1, 2, 3, 4, 5\}$ |

|      | $n_1^{(l)}  n_2^{(l)}$ | $n_3^{(l)}$                |                    |                        |

|      | (a)                    | (b)                        | (c)                | (d)                    |

|      |                        |                            |                    |                        |

**Fig. 3.** Executing getFactoring $(1,0,\emptyset)$ , meaning that we consider a factoring which includes the top-left corner of (a). The returned factoring is highlighted in thick lines.

The algorithm then builds a set  $\mathbb{J}$  of all the candidates for J. Each element  $J_{j'}$  contains all the inputs j'' that would benefit from  $I_{j'}$  being the final result I. Based on the observation mentioned above,  $J_{j'}$  can be built through superset computation between elements of  $\mathbb{I}$  (line 13, Fig. 3d). After we build  $\mathbb{I}$  and  $\mathbb{J}$ , finally line 14 finds a pair of  $(I_{j^*}, J_{j^*})$  where  $I_{j^*} \in \mathbb{I}$ ,  $J_{j^*} \in \mathbb{J}$  with the maximum saving  $(|I_j^*|-1)\cdot|J_j^*|$ . The maximum saving as produced in Fig. 3 equals  $(|\{1,2\}|-1)\cdot|\{0,2,3\}|=3$ .

There are only polynomial operations in this algorithm such as nested for loops, superset checking and intersection which makes the heuristic algorithm polynomial. When one encounters a huge number of neurons and long weight vectors, we further partition neurons and weights into smaller regions as input to Algorithm 1. By doing so, we find factoring possibilities for each weight segment of a neuron and the algorithm can be executed in parallel.

#### 4 Implementation and Evaluation

We have created a verification tool, which first reads a BNN description based on the Intel Nervana Neon framework<sup>1</sup>, generates a combinational miter in Verilog and calls Yosys [30] and ABC [6] for generating a CNF formula. No further optimization commands (e.g., refactor) are executed inside ABC to create smaller CNFs. Finally, Cryptominisat5 [27] is used for solving SAT queries. The experiments are conducted in a Ubuntu 16.04 Google Cloud VM equipped with 18 cores and 250 GB RAM, with Cryptominisat5 running with 16 threads. We use two different datasets, namely the MNIST dataset for digit recognition [18] and the German traffic sign dataset [28]. We binarize the gray scale data to ±1 before actual training. For the traffic sign dataset, every pixel is quantized to 3 Boolean variables.

Table 2 summarizes the result of verification in terms of SAT solving time, with a timeout set to 90 minutes. The properties that we use here are char-

<sup>1</sup> https://github.com/NervanaSystems/neon/tree/master/examples/binary

| ID        | # in- | # neurons    | Properties being investigated                       | SAT/  | SAT solving   | SAT solving     |

|-----------|-------|--------------|-----------------------------------------------------|-------|---------------|-----------------|

|           | puts  | hidden layer |                                                     | UNSAT |               | time (factored) |

| MNIST 1   | 784   | 3x100        | $out_1 \ge 18 \land out_2 \ge 18 \ (\ge 18\%)$      | SAT   | 2m16.336s     | 0 m 53.545 s    |

| MNIST 1   | 784   | 3x100        | $out_1 \ge 30 \land out_2 \ge 30 \ (\ge 30\%)$      | SAT   | 2m20.318s     | 0 m 56.538 s    |

| MNIST 1   | 784   | 3x100        | $out_1 \ge 60 \land out_2 \ge 60 \ (\ge 60\%)$      | SAT   | timeout       | 10m50.157s      |

| MNIST 1   | 784   | 3x100        | $out_1 \ge 90 \land out_2 \ge 90 \ (\ge 90\%)$      | UNSAT | 2m4.746s      | 1m0.419s        |

| Traffic 2 | 2352  | 3x500        | $out_1 \ge 90 \land out_2 \ge 90 \ (\ge 18\%)$      | SAT   | 10m27.960s    | 4m9.363s        |

| Traffic 2 | 2352  | 3x500        | $out_1 \ge 150 \land out_2 \ge 150 \ (\ge 30\%)$    | SAT   | 10m46.648s    | 4m51.507s       |

| Traffic 2 | 2352  | 3x500        | $out_1 \ge 200 \land out_2 \ge 200 \ (\ge 40\%)$    | SAT   | 10m48.422s    | 4m19.296s       |

| Traffic 2 | 2352  | 3x500        | $out_1 \ge 300 \land out_2 \ge 300 \ (\ge 60\%)$    |       | timeout       | timeout         |

| Traffic 2 | 2352  | 3x500        | $out_1 \ge 475 \land out_2 \ge 475 \ (\ge 95\%)$    | UNSAT | 31m24.842s    | 41m9.407s       |

| Traffic 3 | 2352  | 3x1000       | $out_1 \geq 120 \land out_2 \geq 120 \ (\geq 12\%)$ | SAT   | out-of-memory | 9m40.77s        |

| Traffic 3 | 2352  | 3x1000       | $out_1 \ge 180 \land out_2 \ge 180 \ (\ge 18\%)$    | SAT   | out-of-memory | 9m43.70s        |

| Traffic 3 | 2352  | 3x1000       | $out_1 \ge 300 \land out_2 \ge 300 \ (\ge 30\%)$    | SAT   | out-of-memory | 9m28.40s        |

| Traffic 3 | 2352  | 3x1000       | $out_1 \ge 400 \land out_2 \ge 400 \ (\ge 40\%)$    | SAT   | out-of-memory | 9m34.95s        |

**Table 2.** Verification results for each instance and comparing the execution times of the plain hardware verification approach and the optimized version using counting optimizations.

acteristics of a BNN given by numerical constraints over outputs, such as "simultaneously classify an image as a priority road sign and as a stop sign with high confidence" (which clearly demonstrates a risk behavior). It turns out that factoring techniques are essential to enable better scalability, as it halves the verification times in most cases and enables us to solve some instances where the plain approach ran out of memory or timed out. However, we also observe that solvers like Cryptominisat5 might get trapped in some very hard-to-prove properties. Regarding the instance in Table 2 where the result is unknown, we suspect that the simultaneous confidence value of 60% for the two classes out<sub>1</sub> and out<sub>2</sub>, is close to the value where the property flips from satisfiable to unsatisfiable. This makes SAT solving on such cases extremely difficult for solvers as the instances are close to the "border" between SAT and UNSAT instances.

Here we omit technical details, but the counting approach can also be replaced by techniques such as sorting networks<sup>2</sup> [2] where the technique of factoring can still be integrated<sup>3</sup>. However, our initial evaluation demonstrated that using sorting network does not bring any computational benefit.

#### 5 Related Work

There has been a flurry of recent results on formal verification of neural networks (e.g. [8, 10, 15, 20, 25]). These approaches usually target the formal verification of floating-point arithmetic neural networks (FPA-NNs). Huang et

<sup>&</sup>lt;sup>2</sup> Intuitively, the counting + activation function can be replaced by implementing a sorting network and check if for the m sorted result, the  $\frac{m}{2}$ -th element is true.

<sup>&</sup>lt;sup>3</sup> Sorting network in [2] implements merge-sort in hardware, where the algorithm tries to build a sorted string via merging multiple sorted substrings. Under the context of BNN verification, the factored result can be first sorted, then these sorted results can then be integrated as an input to the merger.

al. propose an (incomplete) search-based technique based on satisfiability modulo theories (SMT) solvers [13]. For FPA-NNs with ReLU activation functions, Katz et al. propose a modification of the Simplex algorithm which prefers fixing of binary variables [15]. This verification approach has been demonstrated on the verification of a collision avoidance system for UAVs. In our own previous work on neural network verification we establish maximum resilience bounds for FPA-NNs based on reductions to mixed-integer linear programming (MILP) problems [8]. The feasibility of this approach has work has demonstrated, for example, by verifying a motion predictor in a highway overtaking scenario. The work of Ehlers [10] is based on sound abstractions, and approximates non-linear behavior in the activation functions. Scalability is the overarching challenge for these formal approaches to the verification of FPA-NNs. Case studies and experiments reported in the literature are usually restricted to the verification of FPA-NNs with a couple of hundred neurons.

Around the time (Oct 9th, 2017) we first release of our work regarding formal verification of BNNs, Narodytska et al have also worked on the same problem [23]. Their work focuses on efficient encoding within a single neuron, while we focus on computational savings among neurons within the same layer. One can view our result and their result complementary.

Researchers from the machine learning domain (e.g. [11, 12, 22]) target the generation of adversarial examples for debugging and retraining purposes. Adverserial examples are slightly perturbed inputs (such as images) which may fool a neural network into generating undesirable results (such as "wrong" classifications). Using satisfiability assignments from the SAT solving stage in our verification procedure, we are also able to generate *counterexamples* to the BNN verification problem. Our work, however, goes well beyond current approaches to generating adverserial examples in that it does not only support debugging and retraining purposes. Instead, our verification algorithm establishes formal correctness results for neural network-like structures.

## 6 Conclusions

We are solving the problem of verifying BNNs by reduction to the problem of verifying combinatorial circuits, which itself is reduced to solving SAT problems. Altogether, our experiments indicate that this hardware verification-centric approach, in connection with our BNN-specific transformations and optimizations, scales to BNNs with thousands of inputs and nodes. This kind of scalability makes our verification approach attractive for automatically establishing correctness results at least for moderately-sized BNNs as used on current embedded devices.

Our developments for efficiently encoding BNN verification problems, however, might also prove to be useful in optimizing forward evaluation of BNNs. In addition our verification framework may also be used for debugging and retraining purposes of BNNs; for example, for automatically generating adverserial inputs from failed verification attempts. In the future we also plan to directly synthesize propositional clauses without the support of 3rd party tools such as Yosys in order to avoid extraneous transformations and repetitive work in the synthesis workflow. Similar optimizations of the current verification tool chain should result in substantial performance improvements. It might also be interesting to investigate incremental verification techniques for BNN, since weights and structure of these learning networks might adapt and change continuously.

Finally, our proposed verification workflow might be extended to synthesis problems, such as synthesizing bias terms in BNNs without sacrificing performance or for synthesizing weight assignments in a property-driven manner. These kinds of synthesis problems for BNNs are reduced to 2QBF problems, which are satisfiability problems with a top level exists-forall quantification. The main challenge for solving these kinds of synthesis problems for the typical networks encountered in practice is, again, scalability.

#### Acknowledgments

(Version 1) We thank Dr. Ljubo Mercep from Mentor Graphics for indicating to us some recent results on quantized neural networks, and Dr. Alan Mishchenko from UC Berkeley for his kind support regarding ABC.

(Version 2) We additionally thank Dr. Leonid Ryzhyk from VMWare to indicate us their work on efficient SAT encoding of individual neurons. We further thank Dr. Alan Mishchenko from UC Berkeley for sharing his knowledge regarding sorting networks.

## References

- C. Ambühl, M. Mastrolilli, and O. Svensson. Inapproximability results for maximum edge biclique, minimum linear arrangement, and sparsest cut. SIAM Journal on Computing, 40(2), pages 567–596. SIAM, 2011.

- 2. K. E. Batcher. Sorting networks and their applications. In AFIPS . ACM, 1968.

- S. Bhattacharyya, D. Cofer, D. Musliner, J. Mueller, and E. Engstrom. Certification considerations for adaptive systems: Technical report. no. NASA-CR-2015-218702, 2015.

- A. Biere. Picosat essentials. Journal on Satisfiability, Boolean Modeling and Computation, 4:75–97, 2008.

- 5. M. Bojarski, D. D. Testa, D. Dworakowski, B. Firner, B. Flepp, P. Goyal, L. D. Jackel, M. Monfort, U. Muller, J. Zhang, X. Zhang, J. Zhao, and K. Zieba. End to end learning for self-driving cars. *CoRR*, abs/1604.07316, 2016.

- R. Brayton and A. Mishchenko. ABC: An academic industrial-strength verification tool. In CAV, pages 24–40. Springer, 2010.

- 7. C. Chen, A. Seff, A. Kornhauser, and J. Xiao. Deepdriving: Learning affordance for direct perception in autonomous driving. In *ICCV*, pages 2722–2730, 2015.

- 8. C.-H. Cheng, G. Nührenberg, and H. Ruess. Maximum resilience of artificial neural networks. In ATVA, pages 251–268. Springer, 2017.

- 9. M. Courbariaux, I. Hubara, D. Soudry, R. El-Yaniv, and Y. Bengio. Binarized neural networks: Training deep neural networks with weights and activations constrained to+ 1 or-1. arXiv preprint arXiv:1602.02830, 2016.

- R. Ehlers. Formal verification of piece-wise linear feed-forward neural networks. In ATVA, pages 289–306. Springer, 2017.

- 11. I. Goodfellow, J. Pouget-Abadie, M. Mirza, B. Xu, D. Warde-Farley, S. Ozair, A. Courville, and Y. Bengio. Generative adversarial nets. In *NIPS*, pages 2672–2680, 2014.

- I. J. Goodfellow, J. Shlens, and C. Szegedy. Explaining and harnessing adversarial examples. arXiv preprint arXiv:1412.6572, 2014.

- X. Huang, M. Kwiatkowska, S. Wang, and M. Wu. Safety verification of deep neural networks. In CAV, pages 3–29. Springer, 2017.

- B. Huval, T. Wang, S. Tandon, J. Kiske, W. Song, J. Pazhayampallil, M. Andriluka,

P. Rajpurkar, T. Migimatsu, R. Cheng-Yue, et al. An empirical evaluation of deep learning on highway driving. arXiv preprint arXiv:1504.01716, 2015.

- G. Katz, C. W. Barrett, D. L. Dill, K. Julian, and M. J. Kochenderfer. Reluplex: An efficient SMT solver for verifying deep neural networks. In CAV, pages 97–117. Springer, 2017.

- 16. M. Kim and P. Smaragdis. Bitwise neural networks. arXiv preprint arXiv:1601.06071, 2016.

- A. Krizhevsky, I. Sutskever, and G. E. Hinton. Imagenet classification with deep convolutional neural networks. In NIPS, pages 1097–1105, 2012.

- Y. LeCun. The mnist database of handwritten digits. http://yann.lecun.com/exdb/mnist/, 1998.

- D. Lenz, F. Diehl, M. Troung Le, and A. Knoll. Deep neural networks for markovian interactive scene prediction in highway scenarios. In IV. IEEE, 2017.

- 20. A. Lomuscio and L. Maganti. An approach to reachability analysis for feed-forward relu neural networks. arXiv preprint arXiv:1706.07351, 2017.

- 21. J. Long, E. Shelhamer, and T. Darrell. Fully convolutional networks for semantic segmentation. In *CPVR*, pages 3431–3440, IEEE, 2015.

- 22. S.-M. Moosavi-Dezfooli, A. Fawzi, O. Fawzi, and P. Frossard. Universal adversarial perturbations. arXiv preprint arXiv:1610.08401, 2016.

- N. Narodytska, S. P. Kasiviswanathan, L. Ryzhyk, M. Sagiv, T. Walsh. Verifying Properties of Binarized Deep Neural Networks. arXiv preprint arXiv:1709.06662, 2014.

- 24. R. Peeters. The maximum edge biclique problem is np-complete. *Discrete Applied Mathematics*, 131(3):651–654, 2003.

- 25. L. Pulina and A. Tacchella. An abstraction-refinement approach to verification of artificial neural networks. In *CAV*, pages 243–257. Springer, 2010.

- 26. P. Sermanet, D. Eigen, X. Zhang, M. Mathieu, R. Fergus, and Y. LeCun. Overfeat: Integrated recognition, localization and detection using convolutional networks. arXiv preprint arXiv:1312.6229, 2013.

- 27. M. Soos. The cryptominisat 5 set of solvers at sat competition 2016. SAT COM-PETITION 2016, page 28, 2016.

- 28. J. Stallkamp, M. Schlipsing, J. Salmen, and C. Igel. The German Traffic Sign Recognition Benchmark: A multi-class classification competition. In *IEEE International Joint Conference on Neural Networks*, pages 1453–1460, 2011.

- 29. L. Sun, C. Peng, W. Zhan, and M. Tomizuka. A fast integrated planning and control framework for autonomous driving via imitation learning. arXiv preprint arXiv:1707.02515, 2017.

- 30. C. Wolf, J. Glaser, and J. Kepler. Yosys-a free verilog synthesis suite. In *Proceedings* of the 21st Austrian Workshop on Microelectronics (Austrochip), 2013.

## Appendix - Proof of Theorems

**Theorem 1.** The problem of BNN safety verification is NP-complete.

*Proof.* Recall that for a given BNN and a relation  $\phi_{risk}$  specifying the undesired property between the bipolar input and output domains of the given BNN, the BNN safety verification problem asks if there exists an input  $\boldsymbol{a}$  to the BNN such that the risk property  $\phi_{risk}(\boldsymbol{a}, \boldsymbol{b})$  holds, where  $\boldsymbol{b}$  is the output of the BNN for input  $\boldsymbol{a}$ .

(NP) Given an input, compute the output and check if  $\phi_{risk}(\boldsymbol{a}, \boldsymbol{b})$  holds can easily be done in time linear to the size of BNN and size of the property formula.

(NP-hardness) The NP-hardness proof is via a reduction from 3SAT to BNN safety verification. Consider variables  $x_1, \ldots, x_m$ , clauses  $c_1, \ldots, c_n$  where for each clause  $c_j$ , it has three literals  $l_{j_1}, l_{j_2}, l_{j_3}$ . We build a single layer BNN with inputs to be  $x_0 = +1$  (constant for bias),  $x_1, \ldots, x_m, x_{m+1}$  (from CNF variables), connected to n neurons.

For neuron  $n_j^1$ , its weights and connection to previous layers is decided by clause  $c_j$ .

- If  $l_{j_1}$  is a positive literal  $x_i$ , then in BNN create a link from  $x_i$  to neuron  $n_j^1$  with weight -1. If  $l_{j_1}$  is a negative literal  $x_i$ , then in BNN create a link from  $x_i$  to neuron  $n_j^1$  with weight +1. Proceed analogously for  $l_{j_2}$  and  $l_{j_3}$ .

- Add an edge from  $x_{m+1}$  to  $n_j^1$  with weight -1.

- Add a bias term -1.

For example, consider the CNF having variables  $x_1, \ldots, x_6$ , then the translation of the clause  $(x_3 \vee \neg x_5 \vee x_6)$  will create in BNN the weighted sum computation  $(-x_3 + x_5 - x_6) - x_7 - 1$ .

Assume that  $x_7$  is constant +1, then if there exists any assignment to make the clause  $(x_3 \vee \neg x_5 \vee x_6)$  true, then by interpreting the true assignment in CNF to be +1 in the BNN input and false assignment in CNF to be -1 in the BNN input, the weighted sum is at most -1, i.e., the output of the neuron is -1. Only when  $x_3 = \text{false}$ ,  $x_5 = \text{true}$  and  $x_6 = \text{false}$  (i.e., the assignment makes the clause unsatisfiable), then the weighted sum is +1, thereby setting output of the neuron to be +1.

Following the above exemplary observation, it is easy to derive that 3SAT formula is satisfiable *iff* in the generated BNN, there exists an input such that the risk property  $\phi_{risk} := (x_{m+1} = +1 \to (\bigwedge_{i=1}^n x_i^{(1)} = -1))$  holds. It is done by interpreting the 3SAT variable assignment  $x_i := \text{true}$  in CNF to be assignment +1 for input  $x_i$  in the BNN, while interpreting  $x_i := \text{false}$  in 3SAT to be -1 for input  $x_i$  in the BNN.

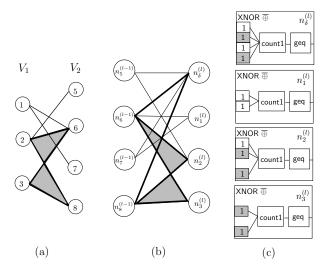

**Theorem 2** (Hardness of factoring optimization). The k-factoring optimization problem, even when k = 1, is NP-hard.

*Proof.* The proof proceeds by a polynomial reduction from the problem of finding maximum edge biclique in bipartite graphs  $[24]^4$ . Given a bipartite graph G, this reduction is defined as follows.

- 1. For  $v_{1\alpha}$ , the  $\alpha$ -th element of  $V_1$ , create a neuron  $n_{\alpha}^{(l)}$ .

- 2. Create an additional neuron  $n_{\delta}^{(l)}$

- 3. For  $v_{2\beta}$ , the  $\beta$ -th element of  $V_2$ , create a neuron  $n_{\beta}^{(l-1)}$ .

- Create weight  $w_{\beta\delta}^{(l)}=1.$

- If  $(v_1, v_2) \in E$ , then create  $w_{\beta\alpha}^{(l)} = 1$ .

This construction can clearly be performed in polynomial time. Figure 4 illustrates the construction process. It is not difficult to observe that G has a maximum edge size  $\kappa$  biclique  $\{A;B\}$  iff the neural network at layer l has a factoring (I,J) whose saving equals  $(|I|-1)\cdot |J|=\kappa$ . The gray area in Figure 4-a shows the structure of maximum edge biclique  $\{\{1,2\};\{6,8\}\}$ . For Figure 4-c, the saving is  $(|\{n_{\delta}^{(l)},n_{2}^{(l)},n_{3}^{(l)}\}|-1)\cdot 2=4$ , which is the same as the edge size of the biclique.

**Fig. 4.** From bipartite graph (a) to BNN where all weights are with value 1 (b), to optimal factoring (c).

<sup>&</sup>lt;sup>4</sup> Let  $G = (V_1, V_2, E)$  be a bipartite graph with vertex set  $V_1 \uplus V_2$  and edge set E connecting vertices in  $V_1$  to vertices in  $V_2$ . A pair of two disjoint subsets  $A \in V_1$  and  $B \in V_2$  is called a *biclique* if  $(a, b) \in E$  for all  $a \in A$  and  $b \in B$ . Thus, the edges  $\{(a, b)\}$  form a complete bipartite subgraph of G. A biclique  $\{A; B\}$  clearly has  $|A| \cdot |B|$  edges.

The following inapproximability result shows that even having an approximation algorithm for the k-factoring optimization problem is hard.

**Theorem 3.** Let  $\epsilon > 0$  be an arbitrarily small constant. If there is a PTAS for the k-factoring optimization problem, even when k = 1, then there is a (probabilistic) algorithm that decides whether a given SAT instance of size n is satisfiable in time  $2^{n^{\epsilon}}$ .

*Proof.* We will prove the Theorem by showing that a PTAS for the k-factoring optimization problem can be used to manufacture a PTAS for MEB. Then the result follows from the inapproximability of MEB assuming the exponential time hypothesis [1].

Assume that  $\mathcal{A}$  is a  $\rho$ -approximation algorithm for the k-factoring optimization problem. We formulate the following algorithm  $\mathcal{B}$ :

**Input:** MEB instance M (a bipartite graph G = (V, E)) Output: a biclique in G

- 1. perform reduction of proof of Theorem 1 to obtain k-factoring instance F :=reduce(M)

- 2. factoring  $(I, J) := \mathcal{A}(F)$

- 3. return  $(I \setminus \{n_{\delta}^{(l)}\}, J)$

Remark: step 3 is a small abuse of notation. It should return the original vertices corresponding to these neurons. Now we prove that  $\mathcal{B}$  is a  $\rho$ -approximation algorithm for MEB: Note that by our reduction two corresponding MEB and k-factoring instances M and F have the same optimal value, i.e., Opt(M) = Opt(F).

In step 3 the algorithm returns  $(I \setminus \{n_{\delta}^{(l)}\}, J)$ . This is valid since we can assume w.l.o.g. that I returned by A contains  $n_{\delta}^{(l)}$ . This neuron is connected to all neurons from the previous layer by construction, so it can be added to any factoring. The following relation holds for the number of edges in the biclique returned by  $\mathcal{B}$ :

$$||I \setminus \{n_{\delta}^{(l)}\}|| \cdot ||J|| = (||I|| - 1) \cdot ||J||$$

$$\geq \rho \cdot \text{Opt}(F)$$

(3a)

(3b)

$$> \rho \cdot \text{Opt}(F)$$

(3b)

$$= \rho \cdot \mathrm{OPT}(M) \tag{3c}$$

The inequality in step (3b) holds by the assumption that A is a  $\rho$ -approximation algorithm for k-factoring and (3c) follows from the construction of our reduction. Equations (3) and the result of [1] imply Theorem 2.