Fernando Silva Inês Dutra Vítor Santos Costa (Eds.)

LNCS 8632

# Euro-Par 2014 Parallel Processing

20th International Conference Porto, Portugal, August 25–29, 2014 Proceedings

# Lecture Notes in Computer Science

*Commenced Publication in 1973* Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

# Editorial Board

David Hutchison, UK Josef Kittler, UK Alfred Kobsa, USA John C. Mitchell, USA Oscar Nierstrasz, Switzerland Bernhard Steffen, Germany Demetri Terzopoulos, USA Gerhard Weikum, Germany Takeo Kanade, USA Jon M. Kleinberg, USA Friedemann Mattern, Switzerland Moni Naor, Israel C. Pandu Rangan, India Doug Tygar, USA

# Advanced Research in Computing and Software Science Subline of Lectures Notes in Computer Science

# Subline Series Editors

Giorgio Ausiello, University of Rome 'La Sapienza', Italy Vladimiro Sassone, University of Southampton, UK

#### Subline Advisory Board

Susanne Albers, University of Freiburg, Germany Benjamin C. Pierce, University of Pennsylvania, USA Bernhard Steffen, University of Dortmund, Germany Deng Xiaotie, City University of Hong Kong Jeannette M. Wing, Microsoft Research, Redmond, WA, USA Fernando Silva Inês Dutra Vítor Santos Costa (Eds.)

# Euro-Par 2014 Parallel Processing

20th International Conference Porto, Portugal, August 25-29, 2014 Proceedings

#### Volume Editors

Fernando Silva Inês Dutra Vítor Santos Costa Universidade do Porto CRACS/INESC-TEC and FCUP Rua do Campo Alegre, 1021 4169-007 Porto, Portugal E-mail: {fds, ines, vsc}@dcc.fc.up.pt

ISSN 0302-9743 e-ISSN 1611-3349 ISBN 978-3-319-09872-2 e-ISBN 978-3-319-09873-9 DOI 10.1007/978-3-319-09873-9 Springer Cham Heidelberg New York Dordrecht London

Library of Congress Control Number: 2014945461

#### LNCS Sublibrary: SL 1 - Theoretical Computer Science and General Issues

#### © Springer International Publishing Switzerland 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in ist current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

Euro-Par is an annual series of international conferences dedicated to the promotion and advancement of all aspects of parallel and distributed computing. It covers a wide spectrum of topics from algorithms and theory to software technology and hardware-related issues, with application areas ranging from scientific to mobile and cloud computing. Euro-Par provides a forum for the introduction, presentation, and discussion of the latest scientific and technical advances, extending the frontier of both the state of the art and the state of the practice.

The main audience of Euro-Par are the researchers in academic institutions, government laboratories, and industrial organizations. Euro-Par's objective is to be the primary choice of such professionals for the presentation of new results in their specific areas. As a wide-spectrum conference, Euro-Par fosters the synergy of different topics in parallel and distributed computing. Of special interest are applications that demonstrate the effectiveness of the main Euro-Par topics.

In addition, Euro-Par conferences provide a platform for a number of accompanying technical workshops. Thus, smaller and emerging communities can meet and develop more focused topics or as yet less established topics.

Euro-Par 2014 was the 20<sup>th</sup> conference in the Euro-Par series, and was organized in Porto, Portugal, by the University of Porto, Faculty of Sciences, Computer Science Department and the Center for Research in Advanced Computing of INESC-TEC. Previous Euro-Par conferences took place in Stockholm, Lyon, Passau, Southampton, Toulouse, Munich, Manchester, Paderborn, Klagenfurt, Pisa, Lisbon, Dresden, Rennes, Las Palmas, Delft, Ischia, Bordeaux, Rhodes, and Aachen. Next year, the conference will be held in Vienna, Austria. More information on the Euro-Par conference series and organization is available on the website at http://www.europar.org.

Euro-Par 2014 covered 15 topics. The paper review process for each topic was managed and supervised by a committee of at least four people: a global chair, a local chair, and two members. Topics with a high number of submissions were managed by larger committees. The final decisions on the acceptance or rejection of the submitted papers were made at a meeting of the conference co-chairs and local chairs of the topics.

The call for papers attracted 267 full-paper submissions, representing 45 countries. A total of 1,070 review reports were collected, giving an average of 4.0 review reports per paper. The Program Committee members hailed from 22 different countries. We selected 68 papers to be presented at the conference and included in the conference proceedings, representing 29 countries from all continents, and resulting in an acceptance rate of 25.5%.

Euro-Par 2014 was very pleased to present three invited speakers of high international reputation, who discussed important developments in very interesting areas of parallel and distributed computing:

- 1. Pawl Watson (Newcastle University, UK)

- 2. Henri Bal (Vrije Universiteit, The Netherlands)

- 3. Ricardo Bianchini (Rutgers University and Microsoft, USA)

As part of Euro-Par 2014, two tutorials and 18 workshops were held prior to the main conference. The two tutorials were:

- 1. Heterogeneous Memory Models, by Benedict R. Gaster (Qualcomm, Inc.)

- 2. High-Performance Parallel Graph Analytics, by Keshav Pingali (UT Austin) and Manoj Kumar (IBM)

The 18 workshops were:

- 1. 12th International Workshop on Algorithms, Models and Tools for Parallel Computing on Heterogeneous Platforms (HeteroPar)

- 2. 5th Workshop on High Performance Bioinformatics and Biomedicine (HiBB)

- 3. Second Workshop on Parallel and Distributed Agent-Based Simulations (PAD-ABS)

- 4. Second Workshop on Runtime and Operating Systems for the Many Core Era (ROME)

- 5. 7th Workshop on Unconventional High-Performance Computing (UCHPC)

- 6. 9th Workshop on Virtualization in High-Performance Cloud Computing (VHPC)

- 7. First Workshop on Applications of Parallel Computation in Industry and Engineering (APCIE)

- 8. Third Workshop on Big Data Management in Clouds (BigDataCloud)

- 9. Workshop on Software for Exascale Computing Project Workshop (SPPEXA)

- 10. Second Workshop on Dependability and Interoperability in Heterogeneous Clouds (DIHC)

- 11. Second Workshop on Federative and Interoperable Cloud Infrastructures (FedICI)

- 12. Third Workshop on On-Chip Memory Hierarchies and Interconnects: Organization, Management and Implementation (OMHI)

- 13. Second Workshop on Large-Scale Distributed Virtual Environments on Clouds and P2P (LSDVE)

- 14. 7th Workshop on Resiliency in High-Performance Computing with Clouds, Grids, and Clusters (Resilience)

- 15. First International Workshop on Reproducibility in Parallel Computing (REP-PAR)

- 16. First Workshop on Techniques and Applications for Sustainable Ultrascale Computing Systems (TASUS)

- 17. 7th International Workshop on Multi-/Manycore Computing Systems (MuCoCoS)

#### 18. 7th Workshop on Productivity and Performance – Tools for HPC Application Development (PROPER)

Workshop papers will be published in a separate proceedings volume.

The 20<sup>th</sup> Euro-Par conference in Porto would not have been possible without the support of many individuals and organizations. We owe special thanks to the authors of all the submitted papers, the members of the topic committees, and the reviewers in all topics for their contributions to the success of the conference. A special word of thanks should go to the global and local chairs, who were always available and did excellent work in managing the reviewing process with a tight deadline. We would also like to express our gratitude to the members of the Organizing Committee. Moreover, we are indebted to the members of the Euro-Par Steering Committee for their trust, guidance, and support. Finally, a number of institutional and industrial sponsors contributed to the organization of the conference. Their names and logos appear on the Euro-Par 2014 website http://europar2014.dcc.fc.up.pt.

It was a pleasure and an honor to organize and host Euro-Par 2014 in Porto. We hope that all participants enjoyed the technical program and the social events organized during the conference, as well as the city of Porto.

August 2014

Fernando Silva Inês Dutra Vítor Santos Costa

# Organization

# Euro-Par Steering Committee

#### Chair

Christian Lengauer University of Passau, Germany

# Vice-Chair

Luc Bougé

ENS Rennes, France

#### **European Representatives**

| Marco Danelutto     | University of Pisa, Italy                 |

|---------------------|-------------------------------------------|

| Emmanuel Jeannot    | LaBRI-Inria, Bordeaux, France             |

| Christos Kaklamanis | Computer Technology Institute, Greece     |

| Paul Kelly          | Imperial College, UK                      |

| Thomas Ludwig       | University of Hamburg, Germany            |

| Emilio Luque        | Autonomous University of Barcelona, Spain |

| Tomàs Margalef      | Autonomous University of Barcelona, Spain |

| Wolfgang Nagel      | Dresden University of Technology, Germany |

| Rizos Sakellariou   | University of Manchester, UK              |

| Henk Sips           | Delft University of Technology,           |

|                     | The Netherlands                           |

| Domenico Talia      | University of Calabria, Italy             |

| Felix Wolf          | GRS and RWTH Aachen University, Germany   |

|                     |                                           |

#### **Honorary Members**

Ron Perrott Karl Dieter Reinartz

#### Observers

Fernando Silva Jesper Larsson Träff University of Erlangen-Nuremberg, Germany

Oxford e-Research Centre, UK

University of Porto, Portugal Vienna University of Technology, Austria

# Euro-Par 2013 Organization

#### **Conference Co-chairs**

| Fernando Silva     | University of Porto, Portugal |

|--------------------|-------------------------------|

| Inês Dutra         | University of Porto, Portugal |

| Vítor Santos Costa | University of Porto, Portugal |

# Local Organizing Committee

| Joana Dumas        | University of Porto, Portugal |

|--------------------|-------------------------------|

| Alexandra Ferreira | University of Porto, Portugal |

| Luís Lopes         | University of Porto, Portugal |

| Pedro Ribeiro      | University of Porto, Portugal |

| Ricardo Rocha      | University of Porto, Portugal |

# **Program Committee**

| Topic 1: Support Tools and | Environments                                  |

|----------------------------|-----------------------------------------------|

| Chair                      |                                               |

| Thilo Kielmann             | Vrije Universiteit Amsterdam, The Netherlands |

|                            |                                               |

| Local Chair                |                                               |

| José C. Cunha              | New University of Lisbon, Portugal            |

|                            |                                               |

| Members                    |                                               |

| Anthony Danalis            | University of Tennessee at Knoxville, USA     |

| Bernd Freisleben           | University of Marburg, Germany                |

| Tomàs Margalef             | Universitat Autonoma de Barcelona, Spain      |

|                            |                                               |

| Topic 2: Performance Pred  | iction and Evaluation                         |

| Chair                      |                                               |

| Alexey Lastovetsky         | University College Dublin, Ireland            |

|                            |                                               |

| Local Chair                |                                               |

| Francisco F. Rivera        | University of Santiago de Compostela, Spain   |

# Members

| David E. Singh            | University Carlos III of Madrid, Spain    |

|---------------------------|-------------------------------------------|

| Dimitrios S. Nikolopoulos | Queen's University of Belfast, UK         |

| Leonel Sousa              | IST-University of Lisbon, Portugal        |

| Petr Tuma                 | Charles University, Czech Republic        |

| Wolfgang Nagel            | Dresden University of Technology, Germany |

# **Topic 3: Scheduling and Load Balancing**

# Chair

| Local Chair                                                                             |                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jorge Barbosa                                                                           | University of Porto, Portugal                                                                                                                                              |

| Members                                                                                 |                                                                                                                                                                            |

| Alexandru Iosup                                                                         | Delft University of Technology,<br>The Netherlands                                                                                                                         |

| Andrzej Goscinski<br>Cevdet Aykanat<br>Frédéric Suter<br>Nick Bessis<br>Ramin Yahyapour | Deakin University, Australia<br>Bilkent University, Ankara, Turkey<br>IN2P3 Computing Center, CNRS, France<br>The University of Derby, UK<br>Göttingen University, Germany |

| Topic 4: High-Performance                                                               | Architectures and Compilers                                                                                                                                                |

| Chair                                                                                   |                                                                                                                                                                            |

| Sally A. McKee                                                                          | Chalmers University of Technology, Sweden                                                                                                                                  |

| Local Chair                                                                             |                                                                                                                                                                            |

| João Paiva Cardoso                                                                      | University of Porto, Portugal                                                                                                                                              |

| Members                                                                                 |                                                                                                                                                                            |

| Changhee Jung<br>Magnus Själander                                                       | Virginia Tech, USA<br>Florida State University, USA                                                                                                                        |

| Rui Hou<br>Soner Onder                                                                  | Institute of Computing Technology, China<br>Michigan Technological University, USA                                                                                         |

| Topic 5: Parallel and Distributed Data Management                                       |                                                                                                                                                                            |

| Chair                                                                                   |                                                                                                                                                                            |

| Josep L. Larriba-Pey                                                                    | Polytechnic University of Catalonia, Spain                                                                                                                                 |

| Local Chair                                                                             |                                                                                                                                                                            |

| Paolo Romano                                                                            | IST-University of Lisbon, Portugal                                                                                                                                         |

| Members                                                                                 |                                                                                                                                                                            |

| David Dominguez-Sal                                                                     | Sparsity Technologies, Spain                                                                                                                                               |

| Kai-Uwe Sattler                                                                         | Technical University of Ilmenau, Germany                                                                                                                                   |

| Patrick Martin<br>Yang-Sae Moon                                                         | Queen's University, Kingston, Canada<br>Kangwon National University, Korea                                                                                                 |

|                                                                                         |                                                                                                                                                                            |

# Topic 6: Grid, Cluster and Cloud Computing

| Chair                               |                                    |

|-------------------------------------|------------------------------------|

| Uwe Schwiegelshohn                  | Universität Dortmund, Germany      |

| <b>Local Chair</b><br>Hervé Paulino | New University of Lisbon, Portugal |

|                                     |                                    |

# Members

Chair

| University of Calabria, Italy            |

|------------------------------------------|

| Universidad Politécnica de Madrid, Spain |

| Inria, France                            |

| University of Manchester, UK             |

| Tokyo Institute of Technology, Japan     |

| IBM, USA                                 |

|                                          |

# **Topic 7: Green High-Performance Computing**

| Martin Schulz            | Lawrence Livermoore National Laboratory,<br>USA |

|--------------------------|-------------------------------------------------|

| Local Chair              |                                                 |

| Luís Lopes               | University of Porto, Portugal                   |

| Members                  |                                                 |

| Enrique S. Quintana Orti | Universidad Jaime I, Castellon, Spain           |

| Koji Inoue               | Kyushu Institute of Technology, Japan           |

|                          |                                                 |

# **Topic 8: Distributed Systems and Algorithms**

Chair

Paul Grace

Vincent Gramoli

| Pascal Felber    | Université de Neuchâtel, Switzerland |

|------------------|--------------------------------------|

| Local Chair      |                                      |

| Luís Veiga       | IST-University of Lisbon, Portugal   |

| Members          |                                      |

| Corentin Travers | ENSEIRB-MATMECA, France              |

| Fabio Kon        | University of São Paulo, Brazil      |

University of Southampton, UK

University of Sydney, Australia

# **Topic 9: Parallel and Distributed Programming**

# Chair

| Henri Bal                                                                                | Vrije Universiteit Amsterdam, The Netherlands                                                                                                                                      |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Local Chair                                                                              |                                                                                                                                                                                    |

| João Luís Sobral                                                                         | University of Minho, Portugal                                                                                                                                                      |

| Members                                                                                  |                                                                                                                                                                                    |

| Ana Varbanescu<br>Christian Perez<br>Fabrice Huet<br>Marco Danelutto<br>Peter Kilpatrick | University of Amesterdam, The Netherlands<br>Inria, ENS-Lyon, France<br>University of Nice Sophia Antipolis, France<br>University of Pisa, Italy<br>Queen's University Belfast, UK |

| Topic 10: Parallel Numerica                                                              | l Algorithms                                                                                                                                                                       |

| Chair                                                                                    |                                                                                                                                                                                    |

| Laura Grigori                                                                            | Inria Paris, France                                                                                                                                                                |

| Local Chair                                                                              |                                                                                                                                                                                    |

| Rui Ralha                                                                                | University of Minho, Portugal                                                                                                                                                      |

| Members                                                                                  |                                                                                                                                                                                    |

| Daniel Kressner                                                                          | EPFL, Switzerland                                                                                                                                                                  |

| Rob Bisseling                                                                            | Utrecht University, The Netherlands                                                                                                                                                |

| Topic 11: Multicore and Ma                                                               | anycore Programming                                                                                                                                                                |

| Chair                                                                                    |                                                                                                                                                                                    |

| Raymond Namyst                                                                           | University of Bordeaux 1, France                                                                                                                                                   |

| Local Chair                                                                              |                                                                                                                                                                                    |

| Ricardo Rocha                                                                            | University of Porto, Portugal                                                                                                                                                      |

| Members                                                                                  |                                                                                                                                                                                    |

| Christoph Kessler                                                                        | University of Linköping, Sweden                                                                                                                                                    |

| Elisabeth Larsson                                                                        | Uppsala University, Sweden                                                                                                                                                         |

| Frank Mueller                                                                            | North Carolina State University, USA                                                                                                                                               |

| Jean-François Méhaut<br>Jesper Träff                                                     | Grenoble University, France                                                                                                                                                        |

| Marco Aldinucci                                                                          | Vienna University of Technology, Austria<br>University of Turin, Italy                                                                                                             |

| Mitsuhisa Sato                                                                           | University of Tsukuba, Japan                                                                                                                                                       |

|                                                                                          |                                                                                                                                                                                    |

| Topic 12: Theory and Algorithms for Parallel Computation |                                                              |

|----------------------------------------------------------|--------------------------------------------------------------|

| Chair                                                    |                                                              |

| Andrea Pietracaprina                                     | University of Padova, Italy                                  |

| Local Chair                                              |                                                              |

| Pedro Ribeiro                                            | University of Porto, Portugal                                |

| Members                                                  |                                                              |

| Kieran Herley<br>Sergei Vassilvitskii                    | University College Cork, Ireland<br>Google, USA              |

|                                                          |                                                              |

| Topic 13: High-Performan                                 | ce Networks and Communication                                |

| Chair                                                    |                                                              |

| José Flich                                               | Universidad Politécnica de Valencia, Spain                   |

| Local Chair                                              |                                                              |

| Filipe Araújo                                            | University of Coimbra, Portugal                              |

| Members                                                  |                                                              |

| Cyriel Minkenberg<br>Maurizio Palesi                     | IBM Research - Zurich, Switzerland<br>Kore University, Italy |

| Tor Skeie                                                | University of Oslo and Simula Research<br>Laboratory, Norway |

| Topic 14: High-Performan                                 | ce and Scientific Applications                               |

| Chair                                                    |                                                              |

| Francisco Brasileiro                                     | Universidade Federal de Campina Grande,<br>Brazil            |

| Local Chair                                              |                                                              |

| Pedro Medeiros                                           | New University of Lisbon, Portugal                           |

| Members                                                  |                                                              |

| Adélia Sequeira                                          | IST-University of Lisbon, Portugal                           |

| Gilles Fedak<br>Walfredo Cirne                           | University of Lyon, France<br>Google, USA                    |

|                                                          | ~ /                                                          |

## **Topic 15: GPU and Accelerator Computing**

## Chair

| Paul Kelly                                                                                                                  | Imperial College London, UK                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Local Chair                                                                                                                 |                                                                                                                                                                                                                              |

| João Lourenço                                                                                                               | New University of Lisbon, Portugal                                                                                                                                                                                           |

| Members                                                                                                                     |                                                                                                                                                                                                                              |

| Alexander Heinecke<br>Anton Lokhmotov<br>Christian Plessl<br>Didem Unat<br>Dora Blanco Heras<br>Lee Howes<br>Naoya Maruyama | Technische Universität München, Germany<br>ARM, UK<br>University of Paderborn, Germany<br>Lawrence Berkeley Lab, USA<br>University of Santiago de Compostela, Spain<br>Qualcomm, USA<br>Tokyo Institute of Technology, Japan |

| Pedro Gonnet                                                                                                                | Durham University, UK                                                                                                                                                                                                        |

# Euro-Par 2014 Reviewers

Euro-Par is very grateful to all reviewers for their kind cooperation and effort to achieve an average of four reviews per paper, producing a total of 1,070 reviews.

Abdou Guermouche Abdullah Gharaibeh Adélia Sequeira Afshin Zafari Agostino Forestiero Aidan Chalk Akihiro Nomura Albert-Jan Yzelman Alberto Lluch Lafuente Alberto Sanchez Alejandro Rico Aleksandar Ilic Alex Ramirez Alexander Fölling Alexander Heinecke Alexandra Carpen-Amarie Alexandre Denis Alexandru Costan Alexandru Iosup Alexey Lastovetsky Aline Paes

Altino Sampaio Alvaro Aguilera Alvsson Bessani Amina Guermouche Ana Lucia Varbanescu Ana-Maria Oprescu Anastassios Nanos Andra Hugo Andrea Pietracaprina Andreas Agne Andrew Stephen McGough Andrzej Goscinski Angelo Furfaro Angelos Papatriantafyllou Anita Sobe Anna Sikora Anthony Danalis Anton Lokhmotov Antonin Steinhauser Antonio Espinosa Antonio García-Loureiro

Arash Rezaei Arlindo Conceição Armanda Rodrigues Arnau Prat Ata Turk Aval Zaks B. Barla Cambazoglu Barry Rountree Basilio B. Fraguela Benjamin Herta Bernd Freisleben Bing Tang Bo Li Bo Wu Bogdan Nicolae Bogdan Prisacari Bora Ucar Brice Goglin Brice Videau Bruno Ciciani Bruno Medeiros Bunjamin Memishi Carlee Joe-Wong Carlo Mastrojanni Carmela Comito Cecília Gomes Ceriel Jacobs Cevdet Aykanat Changhee Jung Chao Li Christian Perez Christian Plessl Christiane Pousa Christoph Kessler Christos Kartsaklis Claudia Misale Clemens Grelck Corentin Travers Cosmin Dumitru Cyriel Minkenberg César De Rose Daniel Cordeiro Daniel Franco Daniel Kressner Darko Petrovic

David Dominguez-Sal David E. Singh David Fiala Davide Frev Denis Barthou Didem Unat Diego Didona Diego Rodríguez Martínez Diego Rughetti Diego Souza Dimitar Lukarski Dimitrios S. Nikolopoulos Diogo Telmo Neves Domenico Talia Dominik Goeddeke Donald E. Porter Dong Li Dora Blanco Heras Eduardo Cesar Edwin Yaqub Elisabeth Brunet Elisabeth Larsson Elizeu Santos-Neto Emilio Francesquini Emilio Padrón Emilio Tuosto Emmanuel Jeannot Enrique S. Quintana-Orti Eoghan O'Neill Eric Aubanel Erwan Le Merrer Eugenio Cesario Fabio Kon Fabio Luporini Fabio Tordini Fabrice Dupros Fabrice Huet Fabricio Silva Fabrizio Marozzo Farhad Mehdipour Farhana Zulkernine Felix Garcia Carballeira Ferdinando Fioretto Fernando Birra Fernando Ramos

Feroz Zahid Filipe Araújo Flavien Quesnel Florian Rathgeber Flávio Cruz Francesco Versaci Francis Russell Francisco Argüello Francisco Brasileiro Francisco D. Igual Francisco F. Rivera Francisco Gaspar Frank Mueller Francois Broquedis Francois Gindraud Francois Trahav Francoise Baude Frédéric Suter Gabriel Marin Gavin Vaz Ge Song George Rokos George Terzopoulos George Tzenakis German Rodriguez Gheorghe-Teodor Bercea Gilles Fedak Giorgis Georgakoudis Giuliano Mega Gokcen Kestor Gorkem Asilioglu Guangyu Sun Guilherme Peretti Pezzi Haipeng Jia Haiwu He Hans Vandierendonck Hartwig Anzt Heike McCraw Heinrich Riebler Heithem Abbes Helen Karatza Henri Bal Henrique Domingos Hervé Paulino Hinde Bouziane

Hitoshi Sato Holger Brunst Holger Mickler Hubertus Franke Håkan Sundell Idafen Santana-Pérez Ilia Pietri Ioannis A. Moschakis Ismail El Helw Ivan Tanasic Ivanilton Polato Ivor Spence Jairo Panetta Jan Westerholm Javier Celava Javier Garcia Blas Jean-Francois Méhaut Jean-Marc Pierson Jens Doleschal Jens Domke Jens Gustedt Jesper Träff Jesús Montes Jiavuan Meng Jie Shen Jing Liu Jizeng Wei Joan Sorribes Joana Côrte-Real John Earnest John Shalf Jonathan Rouzaud-Cornabas Jorge Barbosa Jose E. Roman Josep Jorba Josep L. Larriba-Pev Joseph Hellerstein Joseph Schuchart José C. Cunha José Carlos Cabaleiro José Flich José Germano José Luis Gonzalez Garcia José Salavert Torres José Simão

João A. Silva João Barreto João Leitão João Lourenco João Luís Sobral João P. Vilela João Paiva João Paiva Cardoso João Santos João Silva Juan Angel Lorenzo del Castillo Juan C. Pichel Juan Carlos Moure Julien Bigot Julien Forget Julio Anjos Julita Corbalan Jun Wang Justine Rochas Jörg Keller Kadir Akbudak Kai-Uwe Sattler Kamer Kava Karthikevan P. Saravanan Kaveh Razavi Kees Verstoep Keiichiro Fukazawa Kenneth O'Brien Kento Sato Kien Le Kieran Herlev Kiril Dichev Kirk Cameron Kivokuni Kawachiva Koichi Shirahata Koji Inoue Konstantina Mitropoulou Kuan Lu Landry Chetsa Lars Schaefers Laura Grigori Laure Gonnord Lauro Beltrão Costa Leandro Fontoura-Cupertino Leandro Marinho

Lee Howes Leonel Sousa Lidia Kuan Lilia Ziane Khodja Lionel Evraud-Dubois Lubomír Bulej Luigi Nardi Lukáš Marek Luís Assuncão Luís Lopes Luís Veiga Madhukar Korupolu Magnus Grandin Magnus Själander Maik Srba Manuel F. Dolz Marcelo Pasin Marco Aldinucci Marco Danelutto Marco Lackovic Marcus Carvalho Marcus Hilbrich Maria Barreda Maria Clicia Castro Maria Couceiro Martin Děcký Martin Kreichgauer Martin Schulz Martin Tillenius María S. Pérez-Hernández Massimo Torquati Mastoureh Hassannezhad Mats Brorsson Matthias Hofmann Matthieu Dorier Mauricio Hanzich Maurizio Drocco Maurizio Palesi Merijn Verstraaten Michael Haidl Michael Kluge Michael Wagner Miguel Areias Mihai Capota Mike Rainey

Miquel Àngel Senar Mircea Moca Mitsuhisa Sato Mohammed Tohid Muhammad Aboelfotoh Murray Cole Márcio Castro Naghmeh Ivaki Naova Maruvama Naravan Desai Neha Gholkar Nick Bessis Nicolai Stawinoga Nicolas Loriant Nicolás Guil Mata Nikola Rajovic Nishanth Balasubramanian Nuno Diegues Nuno Neves Nuno Oliveira Nuno Preguica Nuno Sebastião Oleg Lodygensky Oleksandra Kulankhina Oliver Schmitt Olivier Aumage Olivier Beaumont Onkar Patil Ozcan Ozturk Pablo Quesada Barriuso Pak Markthub Paolo Romano Paolo Trunfio Pascal Felber Patrick Carribault Patrick Martin Paul Grace Paul Kelly Paul Renaud-Goud Paul Watson Paulo Ferreira Paulo Lopes Paulo Sérgio Pavol Bauer Pedro Alonso

Pedro Gonnet Pedro Medeiros Pedro Miguens Pedro Ribeiro Peter Chronz Peter Kilpatrick Peter Libič Petr Tuma Philip Church Pierre Fortin Pierre Sutra Pieter Hiima Porfidio Hernández Radu Prodan Rafael Mayo Gual Rahul Gavatri Ramin Yahvapour Ramon Bertran Ramon Nou Raphael De Camargo Raphael Poss Raquel Lopes Raul Barbosa Raymond Namyst Renan Fischer e Silva Renato Ferreira Ricardo Bianchini Ricardo Dias Ricardo Rocha **Richard Grunzke** Rio Yokota **Rizos Sakellariou** Rob Bisseling Robert Dew **Robert Schoene** Roberto Gioiosa Roberto Palmieri Rov Bakker Rui Camacho Rui Goncalves Rui Hou Rui Ralha Rui Ramalho Rui Silva Rutger Hofman

Saadeldin Moustafa Sai Narasimhamurthy Sally A. McKee Salvatore Venticinque Samuel Thibault Sandro Fiore Sascha Hunold Satoshi Matsuoka Scott Beamer Sebastiano Peluso Seher Acer Sergei Gorlatch Sergei Vassilvitskii Sergio Bernales Shadi Ibrahim Shady Khalifa Shava Smallen Shinichi Miura Shriniyas Anand Panchamukhi Siamak Azodolmolky Sima Soltani Soner Onder Souley Madougou Srinath Krishna Ananthakrishnan Stefan Vijzelaar Stefania Costache Stephan Baumann Stephan Schlagkamp Stephen Olivier Stoyan Garbatov Stylianos Zikos Subramanian Ramachandran Sunpyo Hong Sven van Haastregt Svetislav Momcilovic Sérgio Duarte Sérgio Esteves Takavuki Aoki Tamito Kajiyama Theofrastos Mantadelis

Thilo Kielmann Thomas Hérault Thomas Ropars **Tobias Beisel Tobias** Graf Tobias Hilbrich Tobias Kenter Tomàs Margalef Tomás F. Pena Toni Cortes Tor Skeie Tugrul Davar Uwe Schwiegelshohn Valerio Schiavoni Vania Marangozova-Martin Victor Garcia Victor Goulart Victor Muntés-Mulero Vijav Saraswat Vincent Gramoli Vincent Weaver Vitor Duarte Vladimir Rychkov Vojtěch Horký Wagner Meira Jr. Walfredo Cirne Wang Yu Wei Wu Weslev Bland Wolfgang Nagel Xavier Emerv Xiaojun Ruan Xing Pan Yang-Sae Moon Yao Zhang Yasutaka Wada Yehia Elshater Yong Guo Zafeirios Papazachos Ziming Zhong

# Euro-Par 2014 Invited Talks

#### **Cloud Computing for Healthcare**

Paul Watson, Newcastle University, UK

Cloud Computing has the potential to revolutionise healthcare. The expansion of wireless internet, coupled with a massive growth in cheap, mobile sensors offers opportunities to deliver personalised, high-quality healthcare cheaply to people in their own homes. Clouds have an important role to play in realising this potential, as it requires the ability to store and analyse the vast amounts of data that these sensors collect. This presents both problems and opportunities: new scalable, parallel algorithms and platforms are needed to analyse the sensor data, while there are important advantages to be gained by combining the data from a population of users in order to better understand medical conditions and how best to treat them.

The talk will be illustrated with examples from our projects in this area, including the use of sensors to understand older people's activity in order to provide personalised treatment; and also on the analysis of gaming data to help people recover from strokes.

# Going Dutch: How to Share a Dedicated Distributed Infrastructure for Computer Science Research

#### Henri E. Bal, Vrije Universiteit, The Netherlands

The Distributed ASCI Supercomputer (DAS) is a dedicated distributed infrastructure for Dutch Computer Science research. During its 17 year history, DAS witnessed and supported many waves in distributed computing, including widearea computing (DAS-1), grids and peer-to-peer (DAS-2), e-Science and optical grids (DAS-3), and heterogeneous computing (DAS-4). Unlike many other test beds, the different clusters of DAS are set up by a single organization (the ASCI research school) with one clear vision for each system generation. DAS is designed specifically for Computer Science research, especially for interactive distributed experiments in areas like programming systems, resource management, and networks. With the advent of the fifth generation system, DAS-5, in 2015, DAS has literary become mature and indispensable for Dutch Computer Science.

This presentation first looks back at the impact DAS has had. Despite its relatively modest size and cost, DAS has been used for over 100 PhD theses and for numerous award winning experiments. It enabled large amounts of research funding and it played a key role in huge projects like VL-e and (currently) COMMIT. It also served as a stepping stone for applications like astronomy, multimedia analysis, web-scale reasoning, and climate modelling, each of which won competitions with DAS. Next, the presentation will discuss several ongoing projects in more detail, including programming environments for heterogeneous accelerator-based systems and for big data applications. Here, DAS allows unique and controlled experiments on a variety of hardware. Finally, the presentation tries to draw general conclusions for Computer Science.

# Greening Datacenters: Past, Present, and Future

#### Ricardo Bianchini, Rutgers University and Microsoft, USA

Datacenters host the server infrastructure that powers organizations of many sizes, from universities and enterprises to large Internet services. Collectively, datacenters consume a massive amount of power, representing a financial burden for datacenter operators, an infrastructure burden on power utilities, and an environmental burden on society. However, this problem could be worse if it were not for several advances made over the last decade, especially in the design of large-scale datacenters. In this talk, I will overview the architecture of these datacenters, discuss the main advances made to date, and suggest research directions for the future. Interestingly, some of these directions can benefit directly from the expertise in the parallel computing community.

# Euro-Par 2014 Topics Overview

## **Topic 1: Support Tools and Environments**

T. Kielmann, J.C. Cunha, A. Danalis, B. Freisleben, T. Margalef

This topic aims to bring together designers, developers, and users to share their concerns, ideas, and solutions towards more effective tools and environments for parallel and distributed computing. Current challenges are concerned with improved solutions for ease of use, programmability, correctness, reliability, scalability, portability, performance and energy efficiency for current and emerging parallel and distributed computing systems.

This year, a diversity of papers was submitted to this topic, proposing interesting and valuable research contributions. As a result of the reviewing process, 4 papers were accepted for publication. Globally, the accepted papers discuss foundations, design and implementation issues concerning tool development, and present reports of their practical evaluation via concrete applications and benchmarks.

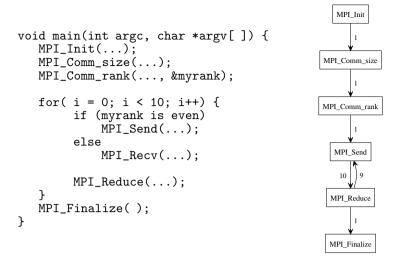

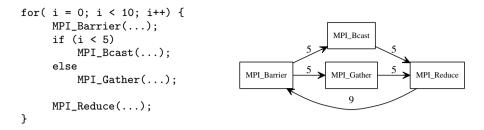

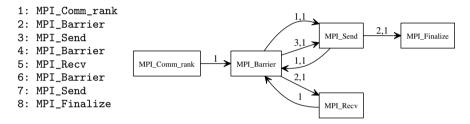

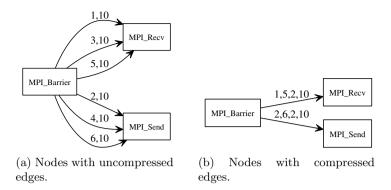

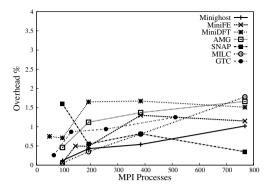

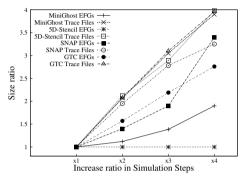

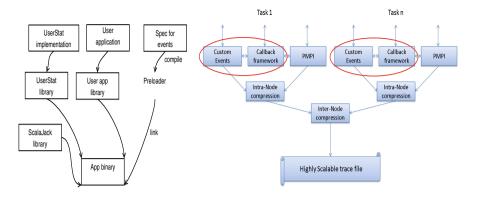

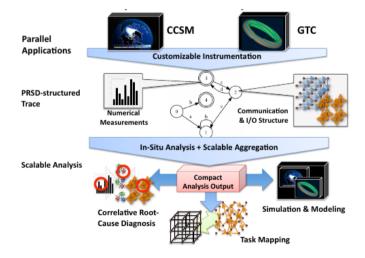

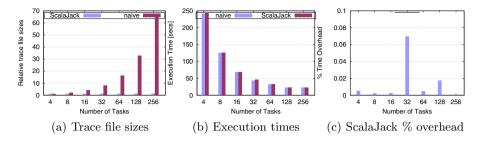

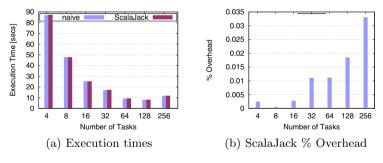

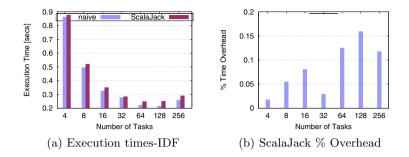

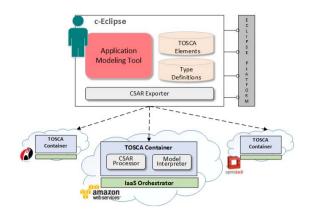

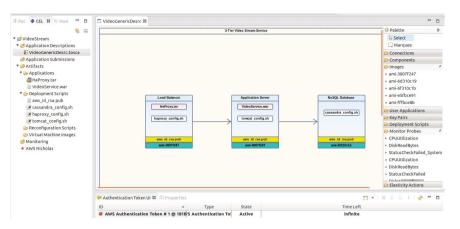

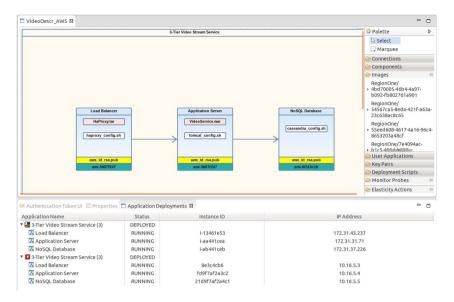

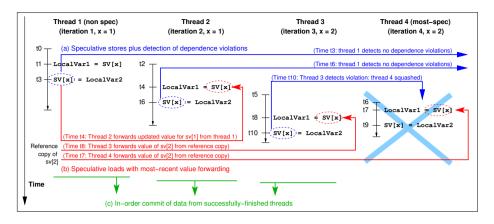

The paper by Aguilar, Furlinger, and Laure, proposes the use of event flow graphs for monitoring MPI applications, as a compromise to balance the lower overhead of profiling tools with the more complete information available from tracers. The paper by Ananthakrishnan and Mueller, presents the ScalaJack tool, by combining customized instrumentation and in-situ data analysis, relying on aspect-orientation techniques for easing code instrumentation, analysis, and code refactoring. The paper by Jiang, Philippen, Knobloch and Mohr, describes extensions to a toolset for instrumenting, measuring and analyzing the performance of parallel programs based on Transactional Memory and Speculative Execution (TM/SE) directives for the IBM BlueGene/Q. The paper by Sofokleous, Loulloudes, Trihinas, Pallis, and Dikaiakos, presents a tool for integrated development of cloud applications, by addressing critical issues of open cloud standard specification, application migration across different cloud providers, and application elasticity.

We would like to thank all the authors who submitted papers to this topic, and the external reviewers, for their contribution to the success of the conference. We also thank the overall coordination and valuable support that was provided by the conference chairs.

#### **Topic 2: Performance Prediction and Evaluation**

A. Lastovetsky, F.F. Rivera, D.E. Singh, D.S. Nikolopoulos, L. Sousa, P. Tuma, W. Nagel

In recent years many novel methodologies and tools have been developed for evaluation, design, and model reduction of both existing and emerging parallel and distributed systems. At the same time, the scope of performance evaluation has constantly broadened to include the evaluation of reliability, robustness, energy consumption, and scalability in addition to traditional system functionalities. The aim of this topic, Performance Prediction and Evaluation, is to bring together system designers and researchers involved with the qualitative and quantitative evaluation and modelling of large-scale parallel and distributed applications and systems (e.g., Grids, Cloud computing environments, multi-core and hybrid architectures, and extreme-scale platforms). Authors were invited to submit novel research in all areas of performance prediction and evaluation, and to help bring together current theory and practice.

Heterogeneity, complexity and scale of the new generation of parallel systems, such as hybrid multicore/multi-accelerator nodes, large-scale heterogeneous clusters, Clouds, etc., coupled with the complexity and scale of applications make this topic particularly timely and challenging. This year, twenty three papers were submitted to the topic. Each paper was reviewed by four reviewers and seven papers were selected for presentation. In general, the quality of the submitted papers was high, and many new ideas, methods, and evaluations were presented. The accepted papers cover a wide range of hot topics and altogether give a good view on the challenges currently addressed by the research community.

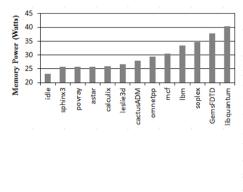

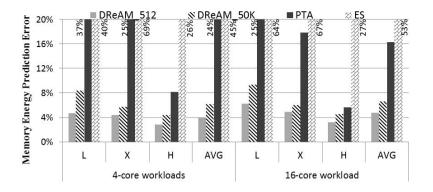

The paper "DReAM: Per-Task DRAM Energy Metering in Multicore Systems" by Qixiao et al., introduces a new model to capture memory energyconsumption per task in a scenario where multiple tasks, possibly for different applications/users, are running on the multicore platform. They present a novel approach for measuring memory energy consumption on a per-task basis.

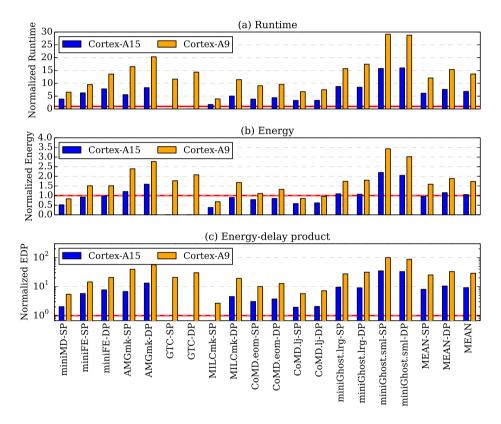

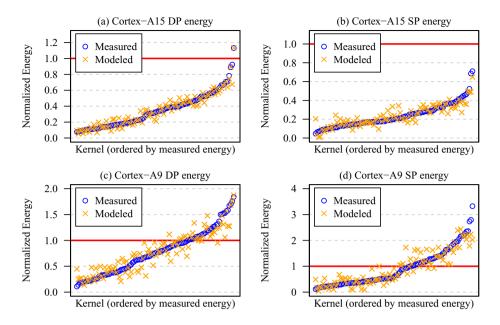

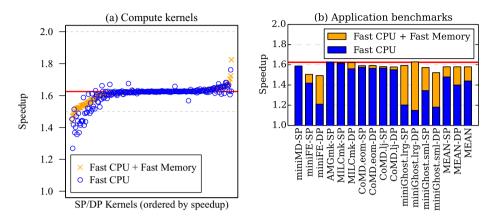

In the paper "Characterizing the Performance-Energy Tradeoff of Small ARM Cores in HPC Computation" by Michael A. Laurenzano et. al., an evaluation of energy and performance for HPC codes running on ARM vs. Intel cores is presented. They present an energy estimation model based on the instruction mix and memory operations obtained through static binary analysis. The paper is a measurement report on the performance and power consumption, in which different workloads from different computational kernels compared ARM processors (Cortex A9 and A15) to an Intel Sandy Bridge CPU.

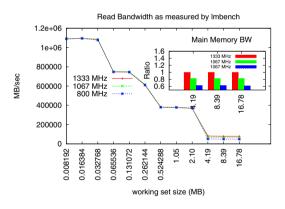

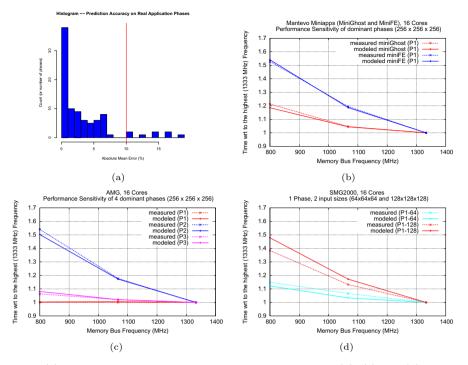

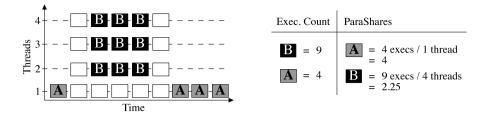

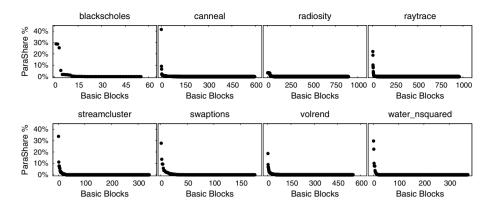

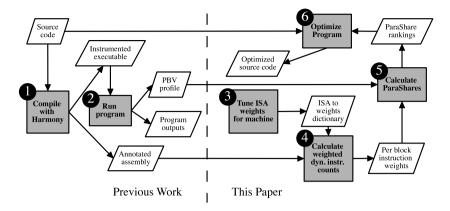

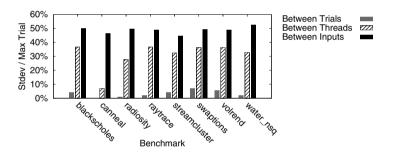

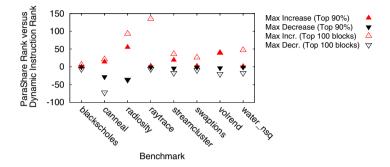

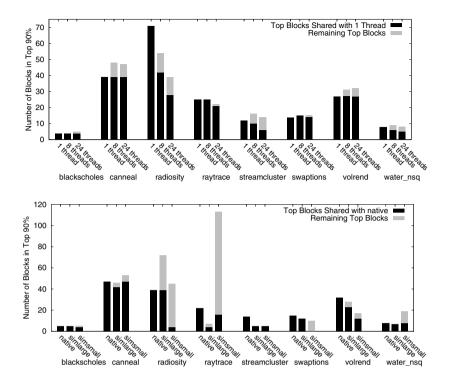

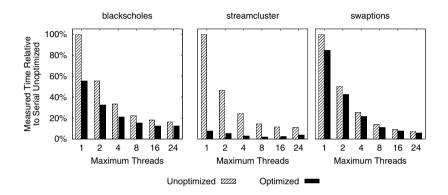

The paper "ParaShares: Finding the Important Basic Blocks in Multithreaded Programs" by Melanie Kambadur and others presents ParaShare, a tool that identifies the basic blocks representing the most time-consuming part of the parallel program. A new metric to score and rank all basic blocks in the program based on their share of parallel execution is introduced. This work also illustrates how the tool can help to identify code whose optimization can bring significant execution time improvement. The paper "Modeling the Impact of Reduced Memory Bandwidth on HPC Applications" by Ananta Tiwari and others presents a methodology for predicting the performance degradation of the code when the main memory bandwidth is reduced. Machine learning strategies are used to obtain the models. An instrumentation tool developed by the authors is used to obtain data. The accuracy of the method was measured on a number of large scale HPC applications.

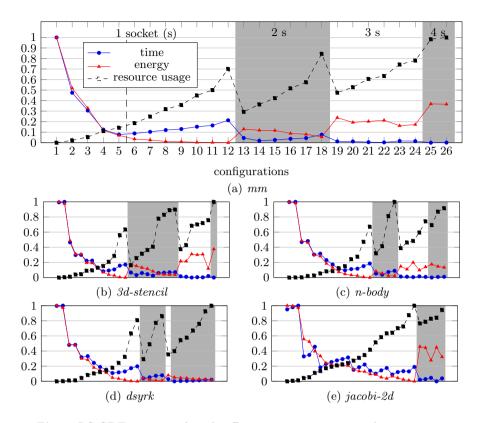

Philipp Gschwandtner and others in their paper "Multi-Objective Auto-Tuning with Insieme: Optimization and Trade-O Analysis for Time, Energy and Resource Usage" present a multi-objective autotuner, which tries to optimize three conflicting criteria - execution time, resources, and energy consumption. Detailed analysis and several hints to improve the design of multi-objective autotuners and code optimization are provided.

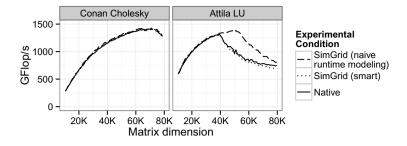

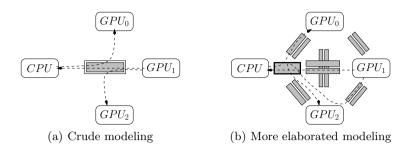

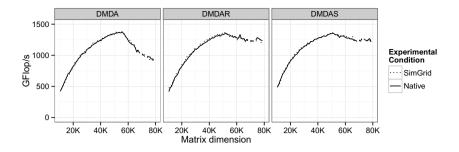

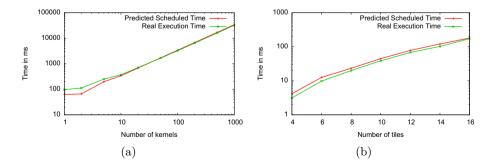

The paper "Modeling and Simulation of a Dynamic Task-Based Runtime System for Heterogeneous Multi-Core Architectures" by Luka Stanisic et al., presents a simulator of a dynamic runtime system (StarPU) for heterogeneous multi-core architectures on top of a simulation toolkit such as SimGrid. It is used to simulate different linear-algebra applications on hybrid computing systems. This proposal is an example of how to predict the performance of applications on hybrid CPU+GPU systems in a short simulation time.

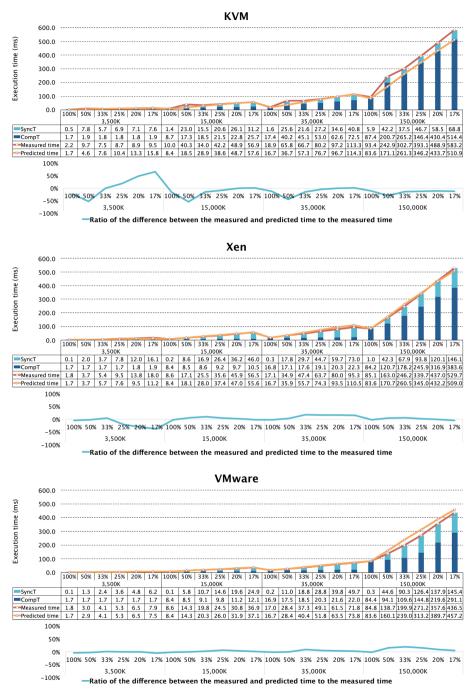

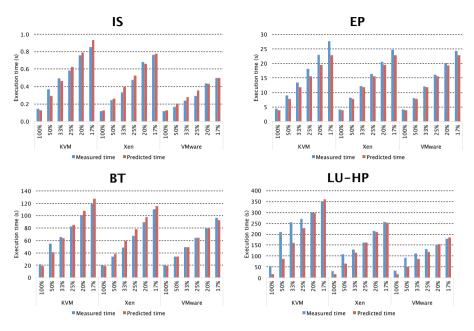

Finally, the paper "Performance Prediction and Evaluation of Parallel Applications in KVM, Xen, and Vmware" by Choel-Ho Hong and others, presents and evaluates a performance model of parallel applications on three virtualized platforms: VMware, Xen, and KVM. This model predicts the duration of the compute and synchronization phases considering the specific scheduling policies of each hypervisor. Using this, it predicts the application overall execution time. The model is based on the assumption that the parallel application consists of computation and synchronization phases.

We would like to take this opportunity to thank all the authors that submitted their work to this topic and the reviewers for their detailed and constructive reports. We are also grateful to the Euro-Par Organizing Committee for their guidance and help.

#### **Topic 3: Scheduling and Load Balancing**

H. Karatza, J. Barbosa, R. Yahyapour, N. Bessis, F. Suter, A. Goscinski, A. Iosup, C. Aykanat

The scheduling and load balancing topic targets in general the optimization of computing resources in several aspect of computation. From the mapping problem of assigning tasks to resources in order to minimize execution time, new approaches concerning energy efficiency become more predominant in today's scheduling research. With the wide range of platforms from high-end infrastructures, with multi-core machines and accelerators, to the highly dynamic cloud infrastructures, new challenges are imposed on resources management.

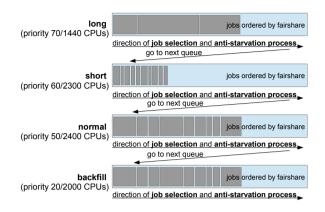

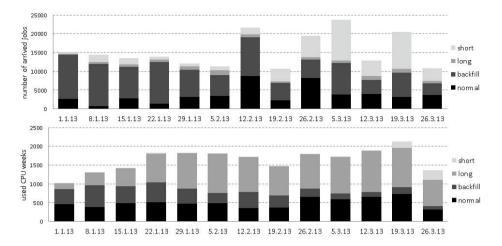

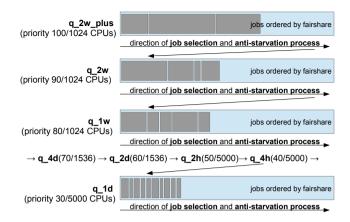

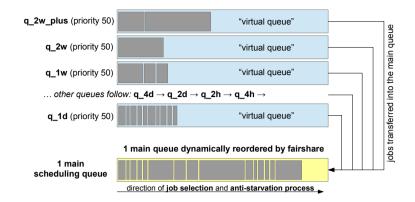

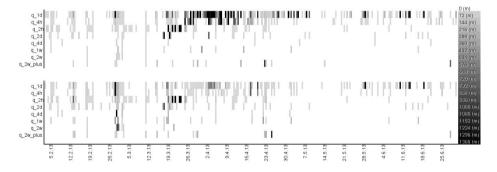

In "On Interactions Among Scheduling Policies: Finding Efficient Queue Setup Using High-Resolution Simulations", the authors address the issue of effectively designing and implementing a scheduling system in a real production supercomputer center, and they show that choosing the right scheduling algorithm is a key aspect when designing and implementing a scheduling system.

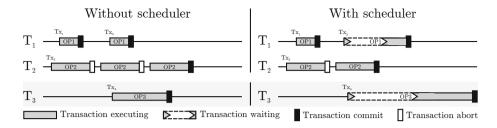

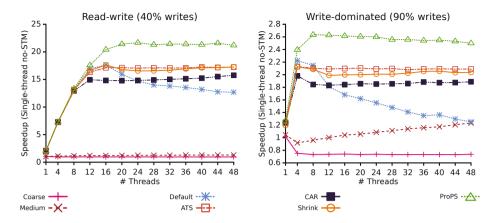

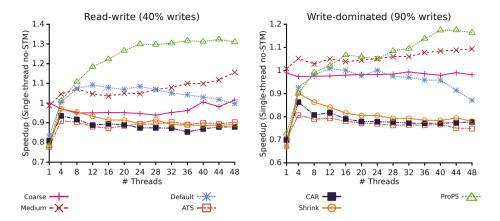

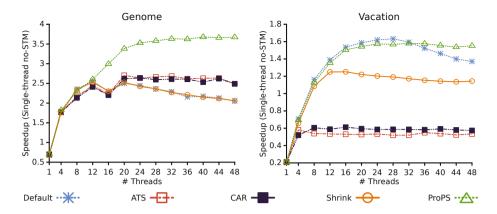

In "ProPS: A Progressively Pessimistic Scheduler for Software Transactional Memory", the authors propose a fine-grain scheduler that monitors concurrency levels between pairs of atomic operations and that dynamically reduces the number of transactions that may start concurrently.

In "A Queueing Theory Approach to Pareto Optimal Bags-of-Tasks Scheduling on Clouds" the authors present a method that minimizes the execution cost while meeting the makespan for data-intensive applications when data is stored outside the cloud so that task's running time is not known a priori.

In "Energy-Aware Multi-Organization Scheduling Problem", the authors model the multi-organization problem as an energy-aware scheduling approach and provide efficient heuristics for a static scenario where all jobs are ready at time zero.

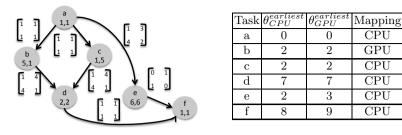

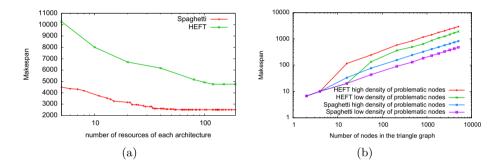

In "Energy Efficient Scheduling of MapReduce Jobs", the authors present a linear programming relaxation technique that guarantees a polynomial time constant-factor approximation to the problem of power-aware map-reduce scheduling in the context of CPU speed scaling. In "SPAGHETtI: Scheduling/Placement Approach for task-Graphs on HETerogeneous architecture", the authors propose a static scheduling algorithm for heterogeneous HPC systems whose complexity is a function of the type of architectures rather than the number of processors.

Finally, we would like to thank all the contributing authors for their work, as well as the reviewers that helped in the selection process.

# **Topic 4: High Performance Architectures and Compilers**

#### S.A. McKee, J.M.P. Cardoso, C. Jung, M. Själander, R. Hou, S. Onder

The topic High Performance Architectures and Compilers deals with architecture design and compilation for high performance systems. The areas of interest range from microprocessors to large-scale parallel machines (including multi-/many-core, possibly heterogeneous, architectures); from general-purpose to specialized hardware platforms (e.g., graphic coprocessors, low-power embedded systems); and from hardware design to compiler technology. On the compilation side, topics of interest include programmer productivity issues, concurrent and/or sequential language aspects, program analysis, program transformation, automatic discovery and/or management of parallelism at all levels, and the interaction between the compiler and the rest of the system. On the architecture side, the scope spans system architectures, processor micro-architecture, memory hierarchy, and multi-threading, and the impact of emerging trends.

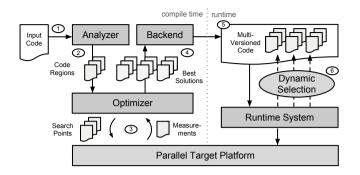

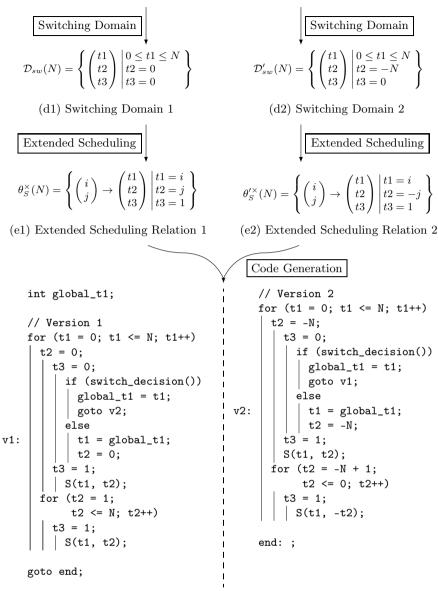

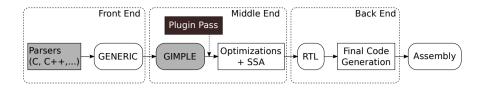

In the 2014 Euro-Par edition of this topic, the selected papers are mainly focused on optimizations to dynamically adapt to computational contexts, techniques to transform GPU specific OpenCL programs to Many Core CPUs, and OpenMP extensions to specify thread-level speculation and their integration in GCC.

#### Topic 5. Parallel and distributed Data Management

J.L. Larriba-Pey, P. Romano, D. Dominguez-Sal, K.U. Sattler, P. Martin, Y.S. Moon

Parallel and distributed management of data are fuelled by the need to develop complex services based on the analysis of ever growing volumes of data. In those cases, there are many situations where a complex hierarchy of requirements imply new approaches and techniques to perform locally parallel or geographically distributed operations to explore those data efficiently.

The scientific committee of Topic 5 has selected 5 papers for their high quality and interesting proposals they made. The proposals they make are varied and deal from the management of distributed relational and key-value stores, to reducing the I/O activity by either balancing the load or dinamically compressing the files of the storage system, to mining the top-k most frequent data items. In all, the papers accepted are varied and provide very good insights of the important issues in present management of data.

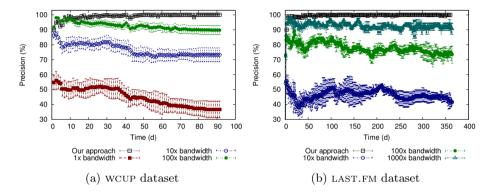

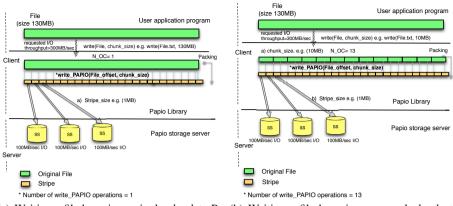

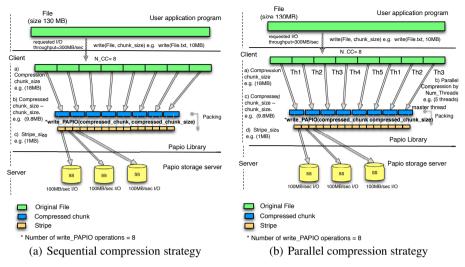

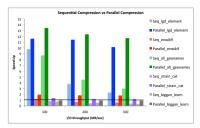

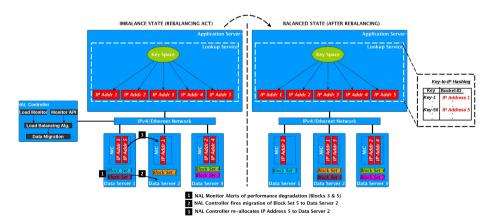

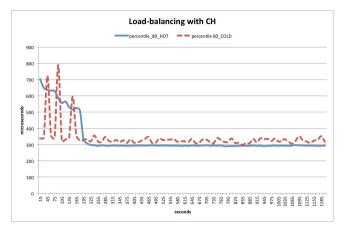

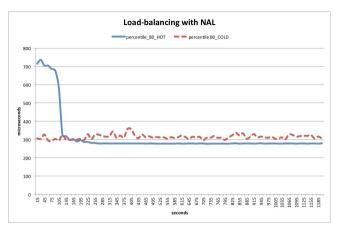

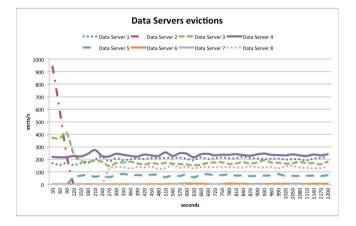

In particular, paper "Robust and Efficient Large-Large Table Outer Joins on Distributed Infrastructures" proposes a new algorithm to compute the outer join of datasets with large skew in a distributed relational environment. Paper "Ultra-fast Load Balancing of Distributed Key-Value Stores through Networkassisted Lookups" presents a load balancing technique based on hashing for keyvalue stores that exploits the flexible IP infrastructures of nowadays computers. Paper "Improving Read Performance with Online Access Pattern Analysis and Prefetching" proposes a novel on-line and real-time analyser that allows to reduce the patterns of the read I/O activity, reducing the overhead and storage capacity needs. Paper "Applying selectively parallel I/O compression to parallel storage systems" presents a new dynamic mechanism to decide whether to compress the size of the files in a storage system, reducing their I/O time. Finally, paper "Top-k Item Identification on Dynamic and Distributed Datasets" proposes a gossip protocol to select the top-k most frequent items in a distributed system with single copy of the data.

The chairs of Topic 5 want to thank the members of the committee for their valuable contributions to the review process and the work they did in managing the whole process in a timely fashion and ensuring very high quality.

#### Topic 6: Grid, Cluster and Cloud Computing

U. Schwiegelshohn, H. Paulino, O. Beaumont, S. Matsuoka, R. Sakellariou, D. Talia, M.S. Pérez-Hernández, and V. Saraswat

Since the operating costs of computing systems are steadily increasing and large computer systems have the potential to increase efficiency in comparison to smaller local installations users are increasingly interested in remotely executing their parallel applications on such systems. In particularly, the use of virtualization has led to a substantial increase of flexibility for these systems. But there are still many open questions that must be addressed by research. For instance, the separation of users and systems due to virtualization produces a new form of market economy requiring business models and service guarantees. Therefore, we need new tools that support monitoring of these guarantees and provide accounting. Also user friendly environments are expected to support users in porting existing applications on these systems and help them to develop applications that efficiently exploit the vast amount of parallelism offered by these systems.

Due to the increasing importance of energy expenses, users and systems administrators are interested in methods to improve system and application management without significantly affecting the quality of service. With respect to this management challenge, it is important to develop methods that allow bridging the above mentioned separation of user and system. Therefore, Topic 6 is devoted to the use and the management of large computer systems. It is the objective of our topic to propose and evaluate new approaches that allow the efficient execution of parallel computing tasks on these systems and therefore to help developers of parallel programs to exploit the vast computing power of these resources without compromising efficiency. In EuroPar 2014, Topic 6 particularly covers workflow management for complex applications, resource management issues, communication in large computer systems, and cooperation between different installations to increase efficiency.

All submitted papers were reviewed by at least 4 reviewers, with 4 papers being selected for inclusion in the program. We are convinced that the contributions of these papers will help us further advance the use of these computer systems for a wide variety of applications.

We would especially like to thank our colleagues, who being experts in the field helped in the reviewing process.

# **Topic 7: Green High Performance Computing**

M. Schulz, L. Lopes, E.S. Quintana Orti, K. Inou

Optimizing power and energy consumption has been identified as one of the most critical issues on our way to exascale. Computations will have to be orders of magnitude more energy efficient than in today's architectures; applications will have to work with fixed total system power caps put in place to not exceed the limited power available; and systems will have to mitigate the impact of power swings during changing workloads. To achieve efficient execution of applications under these constraints, we require new approaches in all aspects of power-aware computing.

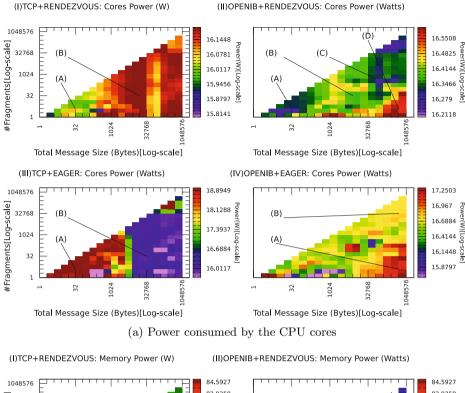

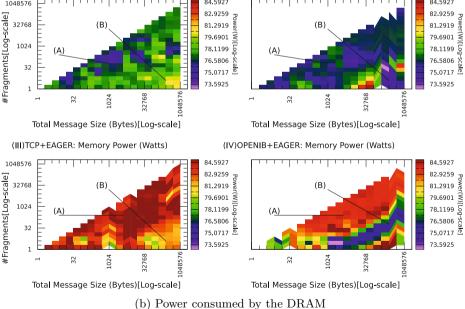

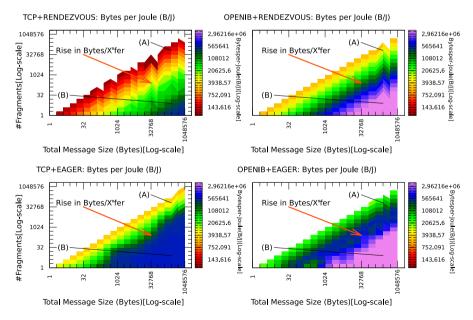

Given the importance of the topic, it was introduced for the first time in the program of the conference with the goal of providing a forum to bring together researchers in this developing field. The contributions received focused on subjects such as: the analysis of the energy efficiency of specific CPU/GPU, cache and memory architectures; the impact of power-saving strategies on performance, and; tools to profile energy usage in HPC systems. The two papers selected for publication describe relevant research on energy efficient cache hierarchy configurations for general purpose GPU computing, and on the impact of data movement between nodes in the power consumption of a system, as a function of the way the inter-process communication layer is designed.

## **Topic 8: Distributed Systems and Algorithms**

#### P. Felber, L. Veiga, P. Grace, V. Gramoli, F. Kon, C. Travers

Parallel computing is increasingly exposed to the development and challenges of distributed systems, such as the lack of load balancing, asynchrony, long latencies, network partitions, failures, malicious and selfish behavior, disconnected operations, well-suited computing models and data structures, heterogeneity. Furthermore, distributed systems are becoming larger, more diverse and more dynamic (changing topology, highly dynamic number of participants).

This topic provides a forum for research and practice, of interest to both academia and industry, about distributed systems, distributed computing, distributed algorithms, and parallel processing on distributed systems.

All submitted papers received at least four reviews, resulting in three papers being accepted for the conference.

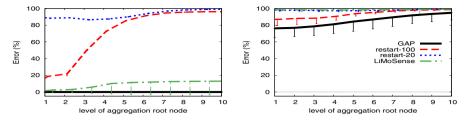

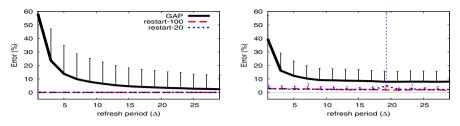

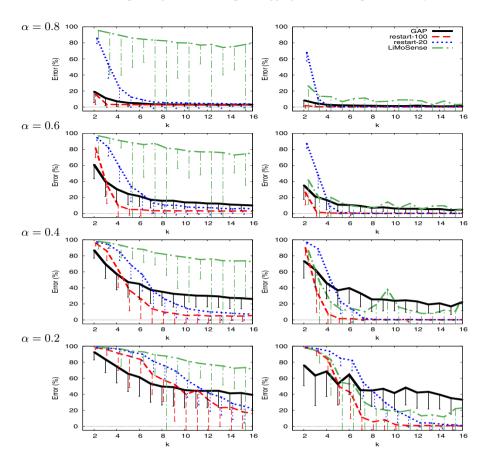

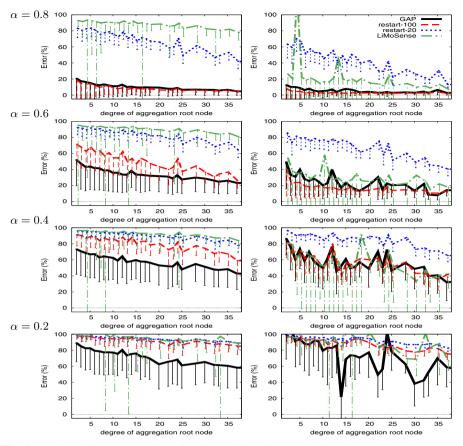

The paper Spanning Tree or Gossip for Aggregation: a Comparative Study by Lehel Nyers and Mark Jelasity proposes a study assessing the two competing paradigms typically used for distributed aggregation queries: tree-based and gossip-based algorithms. It addresses common stereotypes, e.g. about the fragility of trees and slowness of gossip, and encourages researchers to consider more carefully the best topologies for each particular problem or situation.

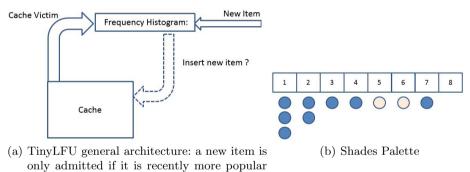

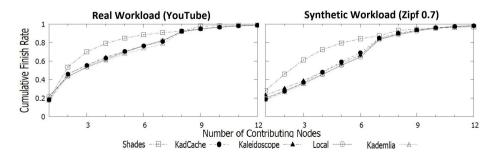

The paper *Shades: Expediting Kademlia's Lookup Process* by Gil Einziger and Roy Friedman addresses how to further the Kademlia DHT. It proposes a new caching and augmented routing mechanism, designed to improve lookup performance and better load balance. This is achieved by combining a local cache keeping the most frequently requested items and an additional routing mechanism based on partitioning nodes and items into colors.

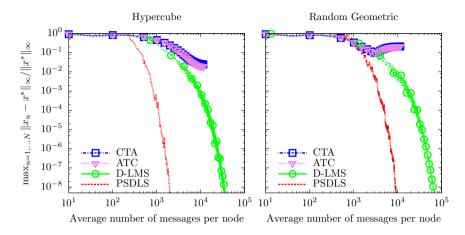

Finally, the paper Analysis and Comparison of Truly Distributed Solvers for Linear Least Squares Problems on Wireless Sensor Networks by Karl E. Prikopa, Hana Straková and Wilfried N. Gansterer proposes a new such solver, adapted from a matrix factorization method, that requires fewer messages per node to reach high accuracy, with an analytical and experimental comparison of the communication cost of various solvers

We would like to take the opportunity of thanking the authors who submitted a contribution, as well as the Euro-Par Organizing Committee and the external referees who provided highly useful comments. Their efforts have made this conference and this topic possible.

# **Topic 9: Parallel and Distributed Programming**

H. Bal, J.L. Sobral, A. Varbanescu, C. Perez, F. Huet, M. Danelutto, P. Kilpatrick

Developing parallel or distributed applications is a difficult task and it requires adequate programming abstractions and models, efficient design tools, high performance languages and libraries, and experimental validation. This topic provides a forum for presentation of new results and practical experience in this domain. It emphasizes research that facilitates the design and development of high-performance, correct, portable, and scalable parallel programs.

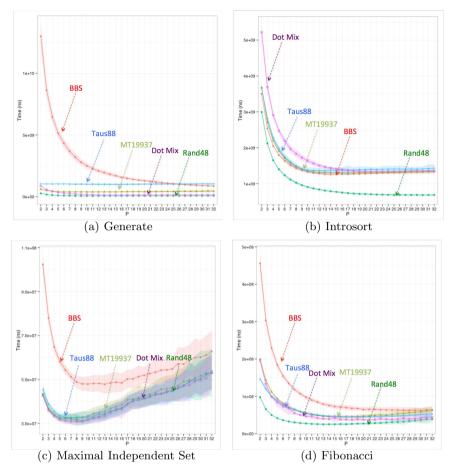

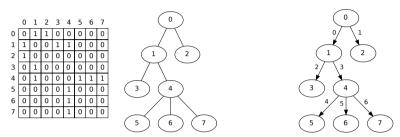

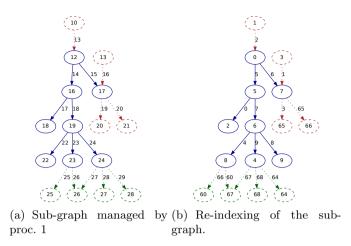

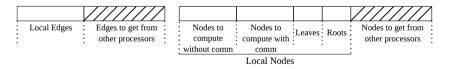

All papers of this topic received 4 reviews that were further discussed among all 7 PC members in a tele-conference meeting. As a result, six strong papers were accepted for the conference, covering important topics such us software and hardware transactional memory, graph analytics, mesh-based simulations, algebraic computations, and random number generation.

# **Topic 10: Parallel Numerical Algorithms**

#### R.H. Bisseling, L. Grigori, D. Kressner, R.M.S. Ralha

Getting progress in many society-relevant issues relies on the usage of numerical simulations. These numerical simulations very often use sophisticated numerical algorithms and massively parallel computers. Thus the design of robust and scalable parallel algorithms is an important research topic, and this track is composed of four papers that consider several such important numerical algorithms. They include solving linear systems of equations, computing the echelon form of a matrix as used for example in algebraic cryptanalysis, time-domain BEM for the wave equation, or exploiting structure to design efficient computational kernels. Both academic and industrial applications can benefit from the algorithms described in these papers.

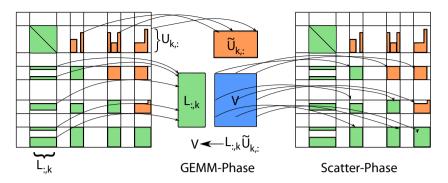

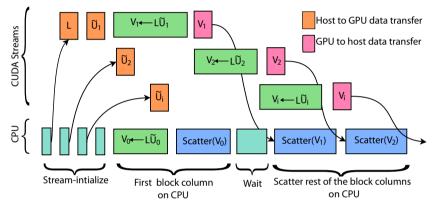

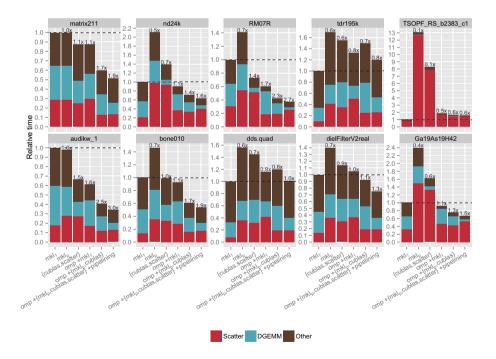

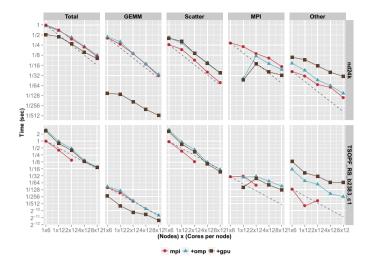

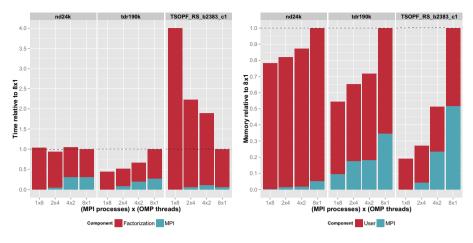

The paper A distributed CPU-GPU sparse direct solver by Piyush Sao, Richard Vuduc, and Xiaoye Sherry Li, presents a hybrid implementation of the sparse LU factorization which can be used to solve very large sparse linear systems of equations. The hybrid implementation is based on MPI, OpenMP, and Cuda, and it is performed in the context of SuperLU\_DIST, a widely used solver implementing the sparse LU factorization for distributed memory computers. SuperLU\_DIST is based on static pivoting and right looking sparse LU factorization. In this context, the paper shows that aggregation of data and pipeline execution to overlap computation with communication are important ingredients for obtaining an overall efficient hybrid implementation of the sparse LU factorization.

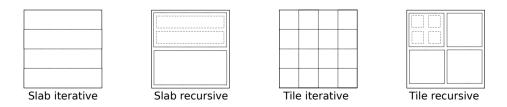

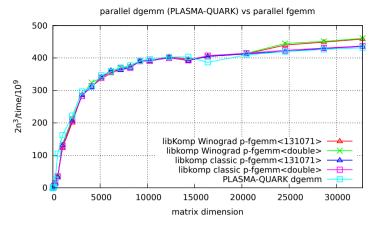

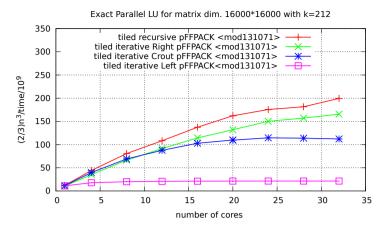

The paper *Parallel Computation of Echelon Forms* by Jean-Guillaume Dumas, Thierry Gautier, Clement Pernet, and Ziad Sultan, presents parallel algorithms for computing echelon forms over a finite field on shared memory architectures. This problem is relevant in a variety of applications, including algebraic cryptanalysisy. Several algorithms are discussed in this paper, which exploit

different partitionings of the matrix, one-dimensional or two-dimensional, block algorithms or recursive algorithms, as well as the usage of fast matrix multiplication Strassen-Winograd algorithm. Several strategies are also developed to balance tiling with delaying modular reductions. Well designed performance experiments compare these different algorithms and outline the role of the different optimizations for obtaining a very efficient parallel implementation.

In the paper Structured Orthogonal Inversion of Block p-cyclic Matrices on Multicores with GPU Accelerators, Sergiy Gogolenko, Zhaojun Bai, and Richard Scalettar consider the problem of computing the inverse of block p-cyclic matrices on multicores and GPUs. Such an operation arises in quantum Monte Carlo algorithms. Given that in this case Gaussian elimination with partial pivoting encounters numerical instability, the authors present an algorithm based on a block structured orthogonal factorization, with a judicious distribution of the work between CPUs and GPGPUs using a quantitative performance model. Performance results show that the method is very efficient on hybrid architectures.

In the paper *Time-domain BEM for Wave Equation: Optimization and Hy*brid Parallelization, Berenger Bramas, Olivier Coulaud, and Guillaume Sylvand focus on efficient implementation of an existing time-domain boundary element method to simulate wave propagation. The code developed is part of an industrial computational work-flow at the Airbus Group Innovation and intends to replace an older code. The most intensive computational kernel of the algorithm is, for each time step, the sum of a number of sparse matrix-vector products. Unlike previous works, that consider the parallelization of individual sparse-matrix products, the central idea here is to exploit the particular sparsity pattern of the matrices to compute several of such products simultaneously. The experimental results are promising.

# **Topic 11: Multicore and Manycore Programming**

R. Namyst, R. Rocha, C. Kessler, E. Larsson, F. Mueller, J.F. Méhaut, J. Träff, M. Aldinucci, M. Sato

Modern homogeneous and heterogeneous multicore and manycore architectures are now part of the high-end and mainstream computing scene. The complexity of these new architectures created several programming challenges and achieving performance on these systems is a difficult task. This topic seeks to explore productive programming of multicore, many integrated cores, and hybrid systems with accelerators. It focuses on novel research and solutions in the form of programming models, languages, compilers, libraries, runtime systems and analysis tools to increase the programmability of multicore, manycore, and hybrid systems, in the context of general-purpose parallel computing and HPC.

The quality of submissions was very high. Papers have been selected based on the recommendations of at least four reviewers. The six accepted papers address a representative set of issues related to the multicore and manycore programming. The paper High-Throughput Maps on Message-Passing Manycore Architectures: Partitioning versus Replication' by Omid Shahmirzadi, Thomas Ropars and Andre Schiper discusses the challenges in implementing scalable data structures for message-passing manycores.

The paper A Fast Sparse Block Circulant Matrix Vector Product by Eloy Romero, Andrés Tomás, Antonio Soriano and Ignacio Blanquer exploits the problem of calculating a sparse matrix vector product where the sparse matrix is block circulant.

The paper Scheduling data flow program in XKaapi: A new affinity-based algorithm for heterogeneous architectures by Raphaël Bleuse, Thierry Gautier, João V. F. Lima, Gregory Mounie and Denis Trystram proposes a generic mechanism to automatically optimize the scheduling between CPUs and GPUs on modern multicore GPU-based architectures.

The paper Delegation Locking Libraries for Improved Performance of Multithreaded Programs by David Klaftenegger, Konstantinos Sagonas and Kjell Winblad proposes libraries for C and C++ that provide an interface for delegation locks as an alternative to traditional locking.

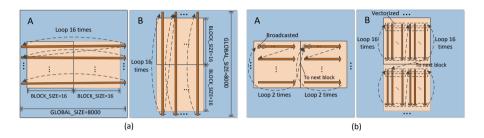

The paper A Generic Strategi for Multi-Stage Stencil Applications by Mauro Bianco and Benjamin Cumming introduces a buffering technique which takes into account intermediate results in the multi-stage procedure to improve memory hierarchy utilization in stencil applications.

The paper Evaluation of OpenMP Task Scheduling Algorithms for Large NUMA Architectures by Jerome Clet-Ortega, Patrick Carribault and Marc Perache presents a configurable OpenMP task scheduler for studying and analyzing work-stealing scheduling algorithms for large NUMA architectures.

We are grateful to the authors of all submitted papers for their contribution and interest in this topic and to the program committee members and subreviewers for their dedicated time and knowledge in evaluating and ranking so many submissions.

#### Topic 12: Theory and Algorithms for Parallel Computation

A. Pietracaprina, P. Ribeiro, K. Herley, S. Vassilvitskii

Parallelism permeates all types of current computing systems, from single CPU machines, to large server farms, supercomputers, clouds, and even Internet-based volunteer computing infrastructures. The effective use of parallelism depends crucially on the availability of faithful, yet tractable, computational models for algorithm design and analysis, and of efficient algorithmic strategies for solving key computational problems on prominent classes of platforms. This topic presents novel contributions that explore foundational issues, models, and algorithms relevant for both traditional and emerging parallel computing scenarios.

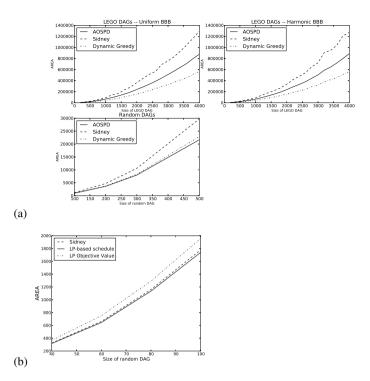

All submitted papers were reviewed by the four members of the topic's committee, and two excellent papers were accepted for presentation at the conference. One paper, "Power-Aware Replica Placement in Tree Networks with Multiple Servers per Client" by Guillaume Aupy, Anne Benoit, Matthieu Journault and Yves Robert, studies some variants of the replica placement problem on trees, whose objective is to minimize power consumption. The other paper, "On Constructing DAG-Schedules with Large AREAs" by Scott T. Roche, Arnold L. Rosenberg and Rajmohan Rajaraman, explores the construction of schedules for computational DAGs which maximize the AREA metric, that is, the rate at which the schedules make nodes eligible for execution. In both papers, the authors prove the NP-completeness of the decision versions of the problems under consideration, and provide polynomial-time heuristics, whose efficiency is tested experimentally.

# **Topic 13: High Performance Networks and Communication**

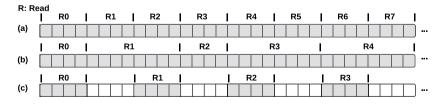

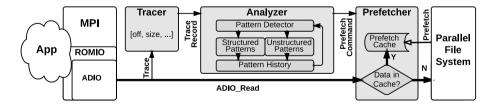

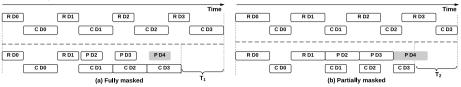

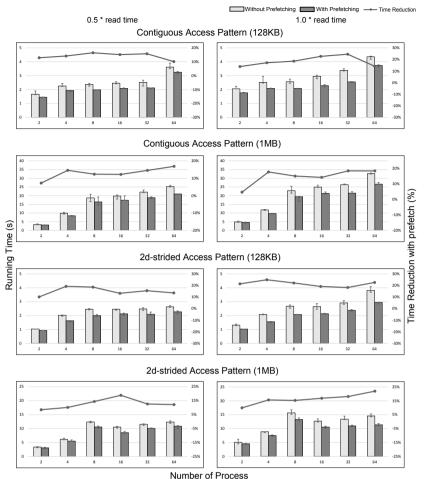

J. Flich, F. Araujo, C. Minkenberg, M. Palesi, T. Skeie