# MULTI-WRITER CONSISTENCY CONDITIONS FOR SHARED MEMORY ${\bf OBJECTS}$

A Thesis

by

CHENG SHAO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

December 2007

Major Subject: Computer Science

# MULTI-WRITER CONSISTENCY CONDITIONS FOR SHARED MEMORY OBJECTS

A Thesis

by

# CHENG SHAO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

Approved by:

Chair of Committee, Jennifer L. Welch

Committee Members, Jianer Chen

Alexander Parlos Vivek Sarin

Head of Department, Valerie E. Taylor

December 2007

Major Subject: Computer Science

# ABSTRACT

Multi-Writer Consistency Conditions for Shared Memory Objects. (December 2007)

Cheng Shao, B.E., Tianjin University;

M.E., Institute of Computing Technology, China Academia of Science Chair of Advisory Committee: Dr. Jennifer L. Welch

Regularity is a shared memory consistency condition that has received considerable attention, notably in connection with quorum-based shared memory. Lamport's original definition of regularity assumed a single-writer model, however, and is not well defined when each shared variable may have multiple writers. In this thesis, we address this need by formally extending the notion of regularity to a multi-writer model. We have shown that the extension is not trivial. While there exist various ways to extend the single-writer definition, the resulting definitions will have different strengths. Specifically, we give several possible definitions of regularity in the presence of multiple writers. We then present a quorum-based algorithm to implement each of the proposed definitions and prove them correct. We study the relationships between these definitions and a number of other well-known consistency conditions, and give a partial order describing the relative strengths of these consistency conditions. Finally, we provide a practical context for our results by studying the correctness of two well-known algorithms for mutual exclusion under each of our proposed consistency conditions.

To My Family

#### ACKNOWLEDGMENTS

First, I would like to thank my advisor Dr. Jennifer L. Welch. You are a wonderful person and a great mentor. I will never forget that it is you who taught me the methodology of theoretical research, who showed me how to follow a rigorous research approach, who gave me the guidance and support in my difficult time and who, with great patience, accompanies me on this long path of my graduate study.

Dr. Evelyn Pierce made significant contribution during the early stage of the research work. It would be impossible to achieve this without her help. Wish her all the good luck in her future career.

I would also like to express my gratitude to the members of my advisory committee, Dr. Jianer Chen, Dr. Alexander Parlos, and Dr. Vivek Sarin, for all the help you extended to me during my study and research.

Finally, I would like to thank my parents and my family. I love you all.

This work was supported in part by NSF grant 0098305, NSF grant 0500265, Texas Higher Education Coordinating Board grant ARP-00512-0091-2001, Texas Higher Education Coordinating Board grant ARP-00512-0007-2006, and Texas Engineering Experiment Station funds.

# TABLE OF CONTENTS

| CHAPTER |                                                             | Page |

|---------|-------------------------------------------------------------|------|

| I       | INTRODUCTION                                                | . 1  |

|         | A. Overview                                                 | . 1  |

|         | B. Contributions                                            |      |

|         | C. Related Work                                             |      |

|         | D. Roadmap of Thesis                                        |      |

| II      | PRELIMINARIES                                               | 6    |

|         | A. Shared Read/Write Registers and Consistency Conditions . | 6    |

|         | B. Quorum Systems                                           | . 10 |

|         | C. System Model                                             | . 10 |

|         | D. Generic Algorithm                                        | 12   |

| III     | MULTI-WRITER REGULAR VARIABLES: SPECIFICA-                  |      |

|         | TIONS AND IMPLEMENTATIONS                                   | 16   |

|         | A. Building Blocks in the Generic Algorithm                 | . 17 |

|         | B. MWWeakReg                                                | 20   |

|         | 1. Specifying MWWeakReg                                     | 20   |

|         | 2. Implementing MWWeakReg                                   | 21   |

|         | C. MWReg                                                    |      |

|         | 1. Specifying MWReg                                         |      |

|         | 2. Implementing MWReg                                       | 26   |

|         | D. MWWeakReg+                                               | 28   |

|         | 1. Specifying MWWeakReg+                                    | 28   |

|         | 2. Implementing MWWeakReg+                                  | 32   |

|         | E. CohReg                                                   | 33   |

|         | 1. Specifying CohReg                                        | . 33 |

|         | 2. Implementing CohReg                                      | 36   |

|         | F. MWReg+                                                   | 39   |

|         | 1. Specifying MWReg+                                        | 39   |

|         | 2. Implementing MWReg+                                      | 42   |

|         | G. PCGLin                                                   | 44   |

|         | 1. Specifying PCGLin                                        | 44   |

|         | 2. Implementing PCGLin                                      | 45   |

| CHAPTER  |                                                              | Page |

|----------|--------------------------------------------------------------|------|

|          | H. Atomicity                                                 |      |

| IV       | PROPERTIES OF THE DEFINITIONS                                | 53   |

|          | A. Locality                                                  | 54   |

|          | 3. Locality of MWWeakReg+                                    |      |

|          | 4. Locality of CohReg                                        |      |

|          | 5. Locality of MWReg+                                        |      |

|          | 6. Locality of PCGLin                                        | 62   |

|          | B. Comparison                                                | 63   |

|          | 1. Comparison Between Proposed Definitions                   |      |

|          | 2. Conjunctions                                              |      |

|          | 3. Comparison with Existing Consistency Conditions           | 69   |

| V        | MUTUAL EXCLUSION USING MULTI-WRITER REGULAR SHARED VARIABLES | 73   |

| VI       | CONCLUSION                                                   | 79   |

| REFERENC | CES                                                          | 82   |

| APPENDIX | A                                                            | 86   |

| VITA     |                                                              | 88   |

# LIST OF FIGURES

| FIGURI | $oldsymbol{\mathrm{E}}$                                                                               | Page |

|--------|-------------------------------------------------------------------------------------------------------|------|

| 1      | A generic quorum-based algorithm to implement a shared read/write register                            | 15   |

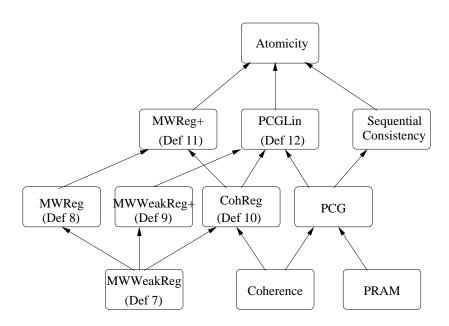

| 2      | Lattice of algorithms and consistency conditions                                                      | 19   |

| 3      | Schedule that satisfies MWWeakReg                                                                     | 20   |

| 4      | An execution of Alg_None that generates the schedule in Figure 3.  Time increases going down the page | 24   |

| 5      | Schedule that satisfies MWReg                                                                         | 25   |

| 6      | An execution of Alg_ID that generates the schedule in Figure 5. $$ . $$                               | 29   |

| 7      | Schedule that satisfies MWWeakReg+                                                                    | 31   |

| 8      | An execution of Alg_WB that generates the schedule in Figure 7. $$                                    | 34   |

| 9      | Schedule that satisfies CohReg                                                                        | 36   |

| 10     | An execution of Alg_LC that generates the schedule in Figure 9                                        | 40   |

| 11     | Schedule that satisfies MWReg+                                                                        | 41   |

| 12     | An execution of Alg_ID_LC that generates the schedule in Figure 11                                    | 43   |

| 13     | Schedule that satisfies PCGLin                                                                        | 45   |

| 14     | An execution of Alg_WB_LC that generates the schedule in Figure 13                                    | 48   |

| 15     | Single-writer schedule that satisfies SWReg but neither MWReg+nor CohReg                              | 50   |

| 16     | Single-writer schedule that satisfies MWReg+ and CohReg but not atomicity                             | 51   |

| FIGURE | S Company of the Comp | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

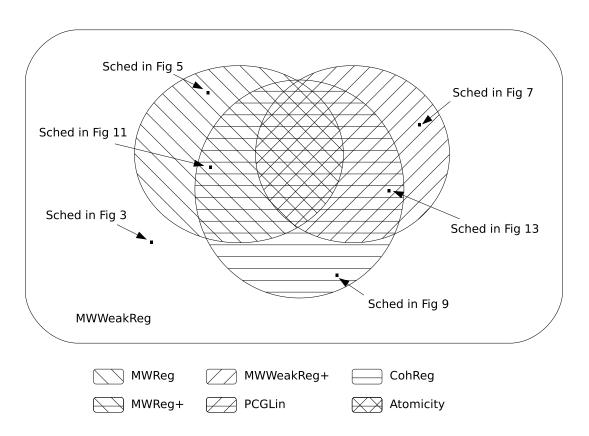

| 17     | Venn diagram of the proposed definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69   |

| 18     | Schedule that is sequentially consistent but not MWWeakReg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71   |

| 19     | Schedule that satisfies MWReg+ but not PRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72   |

| 20     | Partial order among existing consistency conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72   |

| 21     | Algorithms for mutual exclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74   |

# CHAPTER I

## INTRODUCTION

#### A. Overview

Distributed computer systems are ubiquitous today, ranging from multiprocessors to local area networks to wide-area networks such as the Internet. Shared memory, the exchange of information between processes by the reading and writing of shared objects, is an important mechanism for interprocess communications in distributed systems. A consistency condition in a shared memory system is a set of constraints on values returned by data accesses when those accesses may be interleaved or overlapping. A shared memory system with a strong consistency condition may be easy to design protocols for, but may require a high-cost implementation. Conversely, a shared memory system with a weak consistency condition may be easy to implement, but difficult for the user to program or reason about. Finding a consistency condition that can be implemented efficiently and that is nonetheless strong enough to solve practical problems is one of the aims of shared memory research.

A desirable consistency condition for shared memory objects is atomicity (or linearizability) ([16]), in which read and write operations behave as though they were executed sequentially, i.e, with no interleaving or overlap, in a sequence that is consistent with the relative order of non-overlapping operations. In many cases, however, this semantics is difficult to implement, particularly in distributed systems where variables are replicated and where the number of processes with access to the variable is not known in advance. For such systems, the related but weaker condition of regularity ([16]) may be easier to implement while retaining some usefulness. For this

The journal model is IEEE Transactions on Automatic Control.

reason, it has received considerable attention in its own right, notably in connection with quorum-based shared memory ([2], [20], [19] and [18]).

Informally speaking, regularity requires that every read operation return either the value written by the latest preceding write (in real time) or that of some write that overlaps the read. This description is sufficiently clear for the single-writer model<sup>1</sup>, in which the order of the writes performed on a given variable in any execution is well-defined; in fact, it was for this model that Lamport gave his formal definition of regularity. In a multi-writer model, however, multiple processes may perform overlapping write operations to the same variable so that the "latest preceding write" for a given read may have no obvious definition.

A common way to circumvent this problem is to rely on a plausible generalization of the informal definition above, e.g. the following, which appears in [20]:

- A read operation that is concurrent with no write operations returns a value written by the last preceding write operation in some serialization of all preceding write operations, and

- A read operation that is concurrent with one or more write operations returns either the value written by the last preceding write operation in some serialization of all preceding write operations, or any of the values being written in the concurrent write operations.

Such a definition, however, leaves a good deal of room for interpretation. What is meant by "some serialization" in this context? Is there a single serialization of the writes for which the above is true for all read operations, or does it suffice for there to be some (possibly different) such serialization for *each* operation? Or should all

<sup>&</sup>lt;sup>1</sup>In the *single-writer* model, only one process can write to a shared object; other processes can only read from it.

read operations of the same *process* perceive writes as occurring in the same order? Such ambiguities can be avoided with a formal definition of multi-writer regularity, but to our knowledge none has yet been proposed.

## B. Contributions

In this thesis, we formally extend the notion of regularity to a multi-writer model. Specifically, we give several possible formal definitions of regularity in the presence of multiple writers. We then present a quorum-based algorithm to implement each of these definitions and prove the algorithms correct.

The definitions form a lattice as respect to their strength, and the implementations have varying costs with respect to number of messages, size of messages, time delay, and local memory requirements. Taken together, the set of definitions point out the ambiguity of the informal notion of regularity and the algorithms suggest that different costs may be associated with different choices for disambiguating.

If a consistency condition is said to be local, it means that the whole shared memory system satisfies the consistency condition if and only if the consistency condition is satisfied on per-variable basis. Locality is a desired property of consistency conditions: as mentioned in [12], locality enhances modularity and concurrency. In our study, we show that all the proposed definitions satisfy locality.

We also study the relationships between our definitions of multi-writer regularity and several existing consistency conditions: linearizability ([12]), sequential consistency ([15]), coherence ([10]), PRAM ([17]) and PCG ([1]). As part of this analysis, we give a partial order describing the relative strengths of these consistency conditions.

Finally, we provide a practical context for our results by studying the correctness of two well-known algorithms for mutual exclusion when the variables are implemented under our proposed consistency conditions. The algorithms we examine are Peterson's algorithm for 2 processes ([23]) and Dijkstra's algorithm ([24]). We find that Peterson's algorithm is fully correct under all the conditions. Dijkstra's algorithm satisfies only some of the constraints of the mutual exclusion problem under any of the conditions.

# C. Related Work

There is copious literature on consistency conditions for shared memory, both implementations and applications (e.g., [15], [17], [10], [12], [1], [4] and [25]). Our work builds on the the notion of regularity as introduced in [16]. A consistency condition called *Normality* was introduced in [11], which, when all the operations are unary<sup>2</sup>, is equivalent to atomicity. As it turns out, all of our proposed definitions are weaker than Normality.

We use a similar approach as in [27] by identifying building blocks and using various combinations of the building blocks to explore potential consistency conditions. The benefit of this approach is that consistency conditions can be easily organized into a lattice. The difference between our work and [27] is that in [27] the building blocks are identified in the definition level while in our work, the building blocks are identified in the implementation level.

We use a similar framework and system model as introduced in [26] to define our proposed definitions as well as those well-established consistency conditions. The only difference is the partial order used in the frameworks. In [26], the partial order is a combination of per-process order and the 'read from' relation. In our work, the partial order is the real time order among operations.

<sup>&</sup>lt;sup>2</sup>An operation is unary if it only involves a single shared object.

We follow the example of [3], [1] and [13] in using the mutual exclusion problem as an application for our consistency conditions. In [3], Attiya and Friedman revised Peterson's 2-process algorithm ([23]) to solve the mutual exclusion problem under their hybrid consistency model. In [1], Ahamad et al. examined the correctness of Peterson's algorithm and Lamport's bakery algorithm under the PCG consistency model, showing that Peterson's algorithm solves the mutual exclusion problem under PCG, while Lamport's algorithm fails to do so. In a later study, Higham et al. ([13]) investigated other mutual exclusion algorithms, including Dekker's and Dijkstra's, none of which guarantees mutual exclusion under PCG.

# D. Roadmap of Thesis

The rest of the thesis is organized as follows. Chapter II defines our system model and gives a generic algorithm that uses quorum systems to implement a shared read/write object. Chapter III presents our proposed definitions of multi-writer regularity and their implementation algorithms. Chapter IV discusses the locality property of our proposed definitions and compares their relative strength. Chapter V studies the correctness of two mutual exclusion algorithms, Peterson's algorithm for two processes and Dijkstra's algorithm, when variables are implemented under our proposed definitions Chapter VI concludes this thesis and discusses future work.

A preliminary version of this thesis was published in [28].

# CHAPTER II

#### PRELIMINARIES

# A. Shared Read/Write Registers and Consistency Conditions

We assume a concurrent system composed of n application processes,  $p_0, \ldots, p_{n-1}$ , and some number of shared objects. In this thesis, we focus on read/write registers. Such a register, x, supports two operations, read and write, which can be executed by the processes. Each operation has a set of invocations and a set of responses. For a read operation, the invocation by process  $p_i$  is denoted  $read_i(x)$  and the responses have the form  $return_i(x, v)$ , where v is the return value. For a write operation, the invocations by process  $p_i$  have the form  $write_i(x, v)$ , where v is the value to be written, and the response is denoted  $ack_i(x)$ .

The behavior of the shared register in the presence of concurrent accesses by different processes is defined with respect to the desired behavior of the register in the absence of concurrency, so we first define the latter.

When there are no concurrent accesses, the invocation of each operation is directly followed by its matching response, and this pair forms an indivisible operation. The *sequential specification* of a read/write register is the set of all sequences of read and write operations such that each read operation returns the value of the latest preceding write operation; if there is no preceding write, then the read returns the initial value of the register.

**Definition 1** A sequence of operations on a shared object is legal if it belongs to the sequential specification of the shared object.

We now return to considering behavior of the register in the presence of concurrent accesses. In this situation, invocations and responses can be interleaved, although we assume that each process has at most one operation pending at a time. To capture such "well-formedness" constraints, we define the notion of a schedule next. If  $\sigma$  is a sequence of operation invocations and responses, we denote by  $\sigma|i$  the subsequence of  $\sigma$  containing all the invocations and responses performed by process  $p_i$ .

**Definition 2** A sequence  $\sigma$  of invocations and responses is a schedule if, for each i,  $0 \le i < n$ , the following hold:

- $\sigma|i$  consists of alternating invocations and matching responses, beginning with an invocation; and

- if the number of steps taken by  $p_i$  is finite, then the last step by  $p_i$  is a response, i.e., every invocation has a matching response.

Note that this definition of a schedule allows arbitrary asynchrony of process steps, i.e., no constraints are placed on the relative speed with which operations complete or on the time between operation invocations. However, for convenience of analysis, we follow the example of [16] and [9] in employing the useful abstraction of an imaginary global clock. All our references to "real time" in the sequel are with respect to this imaginary clock, which is not available to the processes themselves. This is equivalent to the global-time model introduced in [8] and [5].

The key remaining point is what values should be returned by the reads? This is defined by a consistency condition. Most consistency conditions define a connection between the behavior of the register in the presence of concurrency and the register's sequential specification. Formally, a consistency condition is specified by a particular set of schedules. Thus, the relative "strength" of two consistency conditions can be compared by considering the sets of schedules defining each condition, as follows. Given two consistency conditions  $C_1$  and  $C_2$ ,  $C_1$  is at least as strong as  $C_2$  if  $C_1 \subseteq C_2$ .

Furthermore,  $C_1$  is stronger than  $C_2$  if  $C_1 \subset C_2$ . It is also easy to define a consistency condition as the union or intersection of two other consistency conditions<sup>1</sup>.

The following pieces of notation are useful for defining particular consistency conditions.

Given a schedule  $\sigma$ , we use the expression  $ops(\sigma)$  to denote the set of all operations whose invocations and responses appear in  $\sigma^2$ . By the definition of a schedule, each invocation has a matching response, namely the response by the same process that follows it most closely; an invocation and its matching response form an operation. Furthermore,  $ops(\sigma|i)$  denotes the set of all operations that are performed in  $\sigma$  by process  $p_i$ .

For a shared variable x,  $ops(\sigma|x)$  denotes the set of all operations that are performed on x.

Finally, we let  $writes(\sigma)$  denote the set of all write operations in schedule  $\sigma$ .

Informally speaking, a permutation on a subset of  $ops(\sigma)$  is  $\sigma$ -consistent if it preserves the partial order of the operations in  $\sigma$ .<sup>3</sup> Before giving a more formal defintion, we first define a partial order  $<_{\sigma}$  on  $ops(\sigma)$ : For two operations  $o_1$  and  $o_2$  in  $\sigma$ ,  $o_1 <_{\sigma} o_2$  iff the response for  $o_1$  precedes the invocation for  $o_2$  in  $\sigma$ .

**Definition 3** Given a schedule  $\sigma$ , a permutation  $\pi$  of a subset of  $ops(\sigma)$  is  $\sigma$ -consistent if, for any operations  $o_1$  and  $o_2$  in  $\pi$ ,  $o_1$  precedes  $o_2$  in  $\pi$  whenever  $o_1 <_{\sigma} o_2$ .

<sup>&</sup>lt;sup>1</sup>For example, as we elaborate on later in the thesis, PCG can be represented by Coherence ∩ PRAM, where PCG, Coherence, and PRAM are known consistency conditions.

<sup>&</sup>lt;sup>2</sup>Assume for convenience that each operation in sigma has a unique id, for instance, the j-th operation invoked by process i; this mechanism allows us to distinguish between two reads of the same value by the same process that occur at different points in the schedule.

<sup>&</sup>lt;sup>3</sup>In most situations of interest,  $\sigma$  represents the order of operation invocations and responses in real time.

Furthermore, we use  $op_1 \not>_{\sigma} op_2$  to denote that operation  $op_1$  starts before  $op_2$  ends in schedule  $\sigma$ . According to [16], the following relation holds:

If

$$op_1 <_{\sigma} op_2 \not>_{\sigma} op_3 <_{\sigma} op_4$$

, then  $op_1 <_{\sigma} op_4$

Several of the definitions we present in this thesis rely on the notion of a read operation "reading from" a write operation. Formally:

**Definition 4** Given a schedule  $\sigma$ , consider a function  $\rho$  from the set of read operations in  $\sigma$  to the set of write operations in  $\sigma$ .  $\rho$  is called a reads-from function if for every read operation r, r and  $\rho(r)$  operate on the same shared variable, the value returned by r is the same as the value written by  $\rho(r)$  and  $\rho(r) \not>_{\sigma} r$ . We say that r reads from  $\rho(r)$ .

We conclude this section by giving an important example of a consistency condition in our framework. The original definition of regularity by Lamport ([16]) assumed that only one process performs writes on a given shared register and stated that every read returns either the value of the latest preceding write or the value of some overlapping write. Since there is only one writer and it performs operations sequentially, the notion of "latest preceding write" is well-defined. A rephrasing of this definition that links the concurrent behavior to the sequential specification is given next, where a *single-writer* schedule is a schedule in which every write operation is performed by the same process.

Definition 5 (Single-Writer Regularity or SWReg) A single-writer schedule  $\sigma$  satisfies SWReg iff for every read r in  $ops(\sigma)$ , there exists a permutation  $\pi_r$  of writes $(\sigma) \cup \{r\}$  such that

•  $\pi_r$  is legal, and

•  $\pi_r$  is  $\sigma$ -consistent.

# B. Quorum Systems

Although having processes communicate through shared variables is generally viewed as desirable from a software development perspective, most distributed systems do not directly provide such functionality. However, the illusion of shared variables can be provided through a shared variable simulation layer that runs in a message-passing communication environment. This software layer simulates shared registers on top of the message-passing layer.

The algorithms in this thesis for simulating a shared register use the notion of a quorum system, which is a technique for handling replicated data. Some processes in the system play the role of "servers", which maintain replicas, while others play the role of "clients", which handle invocations of operations on the replicated data. There is one client process corresponding to each application process introduced in the previous section. Let  $P_S$  be the set of server processes and  $P_C$  be the set of client processes. (It is possible for a single physical node to host both a client and a server process.)

A quorum system Q (over  $P_S$ ) is a collection of subsets of  $P_S$ , each of which is called a *quorum*, satisfying the property that for every two distinct quorums Q and Q',  $Q \cap Q' \neq \emptyset$ .

# C. System Model

In this section, we provide definitions for modeling our execution environment. There is a collection  $P = P_{\mathcal{S}} \cup P_{\mathcal{C}}$  of processes that communicate with each other through message-passing.

Each *process* is modeled as a (possibly infinite) state machine, with an initial state and a transition function. The state machine represents the code for the simulation layer that is running at the process.

A configuration of the system is a vector of local states, one per process. An initial configuration contains an initial state for each process.

There are two kinds of *events* that can occur in the system, input and output events. Each event occurs at a single process. The input events are the receipt of a message and the invocation of a shared register operation. The output events are the sending of a message and the response of a shared register operation.

Each input event triggers its corresponding process to take a step: the transition function is applied to the current state of the process and the particular event, and produces a new state of the process and a set of output events. The output events consist of a set of messages sent by the process and at most one shared-object operation response to occur at the process.

An *event list* is a sequence of events, all taking place at the same process, that begins with an input, followed by any number of message sends, and ends with at most one operation response.

An execution is a sequence  $d_0\ell_1d_1\ell_2d_2...$  of alternating configurations  $d_k$  and event lists  $\ell_k$ , starting with an initial configuration  $d_0$ , that satisfies the following conditions.

• Consider any  $d_{k-1}\ell_k d_k$  in the sequence, where  $\ell_k$  takes place at process  $q_i$ . Then applying  $q_i$ 's transition function to  $q_i$ 's state in  $d_{k-1}$  and the first event in  $\ell_k$  produces the remaining events in  $\ell_k$  and  $q_i$ 's state in  $d_k$ . All other components of  $d_k$  are the same as in  $d_{k-1}$ . That is, the process states and events occurring in the sequence are consistent with the processes' transition functions (i.e., the

shared variable simulation algorithm).

- Every message sent is received exactly once and subsequent to its send; only messages sent are received. That is, the communication is reliable.

- If an operation invocation occurs in some event list  $\ell_k$  occurring at process  $q_i$ , then the most recent preceding invocation or response at  $q_i$  (if any) is a response. That is, the application process that is generating the invocations to the client process waits for one operation to finish before invoking the next one.

We can now state our main correctness condition for simulating a register with a particular consistency condition.

**Definition 6** The system implements a read/write register with consistency condition C if, for every execution of the system, the projection onto the set of invocations and responses of the register is a schedule that is in (i.e., satisfies) C.

## D. Generic Algorithm

A generic algorithm that uses quorums to implement a shared read/write register with initial value  $v_0$  is given in Figure 1. Upon receiving a read or write request on the shared object, a client process chooses a quorum using some quorum selection strategy and then queries each member of this quorum about its current "view" of the shared object, which consists of the value of the object and the timestamp associated with the value. After gathering all the responses, the process chooses a set of views to work with, using the function ChooseViews(), and then decides which timestamp among the chosen views is the latest, using function MaxTS(). The operations then continue as follows:

- write: The process increments the timestamp returned by MaxTS(), using the function IncTS(), and writes the new value and the incremented timestamp back to every member of some quorum.

- read: The process uses a function GetValue() to obtain a value associated with the timestamp selected by MaxTS(), and returns that value as the result of the read. The reading process then uses the function OptionalWriteBack() to notify a subset of the processes (which can be either no processes or a quorum of processes) of the value it plans to return before it actually returns.

By plugging in different implementations for the functions MaxTS(), IncTS(), GetValue(), and ChooseViews(), and choosing whether to call OptionalWriteBack(), we obtain registers satisfying different consistency conditions.

This algorithm is a generalization of several existing quorum-based protocols. For example, the appropriate instantiations of the functions yield the algorithms in [20], [7] and [21].

The following lemma states a property of the generic algorithm that we will use later.

**Lemma 1** The sequence of timestamp values taken on by the replica on any server is non-decreasing during any execution of the generic algorithm.

We define the timestamp of a write operation as the timestamp the write operation uses to write to a quorum in Line 7 of the write procedure in Figure 1. The timestamp of a read operation is the timestamp value associated with the variable value returned by the read in Line 5 of the read procedure in Figure 1. For both cases, we use the expression ts(op) to denote the timestamp of operation op.

We now define the reads-from function for the generic algorithm. Given a schedule  $\sigma$ , let  $\rho$  be any function from the read operations in  $\sigma$  to the write operations in

$\sigma$  such that for every read r, r does not end before  $\rho(r)$  starts, and  $ts(r) = ts(\rho(r))$ . There always exists such a function  $\rho$  since a read r will not observe a timestamp t unless it has already been written by some write that started before r ends.

```

Code for client process c_i \in P_{\mathcal{C}}:

local variables:

val /* local copy of shared variable, initially v_0 */

ts \ /* local copy of timestamp, initially smallest timestamp value */

write_i(x, v):

for some quorum Q \in \mathcal{Q}, send \langle \text{READ} \rangle to each s_j \in Q;

wait to receive \langle VIEW, v, t \rangle from each s_j \in Q;

V := ChooseViews();

4

ts := MaxTS(V);

ts := IncTS(ts);

for some quorum Q' \in \mathcal{Q}, send \langle WRITE, val, ts \rangle to each s_j \in Q';

wait to receive \langle ACK \rangle from each s_j \in Q';

ack_i(x);

read_i(x):

for some quorum Q \in \mathcal{Q}, send \langle \text{READ} \rangle to each s_j \in Q;

wait to receive \langle VIEW, v, t \rangle from each p_i \in Q;

3

V := ChooseViews();

ts := MaxTS(V);

val := GetValue(V, ts);

OptionalWriteBack();

return_i(x, val);

Code for server process s_j \in P_{\mathcal{S}}:

local variables:

val /* local copy of shared variable, initially v_0 */

ts /* local copy of timestamp, initially smallest timestamp value */

When s_i receives \langle READ \rangle from c_i:

send \langle VIEW, val, ts \rangle to c_i;

When s_i receives \langle WRITE, v, t \rangle from c_i:

if (ts < t) then

2

val = v; ts = t;

send \langle ACK \rangle to c_i;

```

Fig. 1. A generic quorum-based algorithm to implement a shared read/write register

# CHAPTER III

# MULTI-WRITER REGULAR VARIABLES: SPECIFICATIONS AND IMPLEMENTATIONS

Suppose we instantiate the generic algorithm as follows:

- The timestamp is chosen from the set of natural numbers  $\mathcal{N}$ ;

- Function MaxTS() returns the largest timestamp in numerical order and function IncTS() increments the timestamp by 1;

- Function GetValue() returns the value that is associated with the timestamp returned by MaxTS();

- ChooseViews() combines all the query results from a certain quorum to form a view;

- Function OptionalWriteBack() does nothing;

If only one designated process invokes the write procedure, the resulting algorithm implements a read/write register that satisfies single-writer regularity (Definition 5).

What if more than one process is allowed to perform the write operation? Would the resulting behavior qualify as a possible specification for multi-writer regularity? In the rest of the thesis, we explore this question. But first, let us take a look at various ways the generic algorithm can be instantiated, which, as it turns out, gives us consistency conditions with different strength, and provides us possible definitions of multi-writer regularity.

# A. Building Blocks in the Generic Algorithm

We identify three building blocks that we use to create a specific instantiation from the generic algorithm. Different combinations of the building blocks will give us different algorithms, which in turn yield shared variables with different consistency conditions. The three building blocks are:

• Including unique id in timestamp: If we do not use this building block, then the timestamp is simply chosen from the set of natural numbers  $\mathcal{N}$ . Function MaxTS() returns the largest timestamp in numerical order, while IncTS(ts) increments its argument by 1. Since timestamps are not necessarily unique when using this building block, several different values may share the same largest timestamp value. In this case, GetValue() simply chooses one arbitrarily and returns the corresponding value.

When we use this building block, we define the timestamp as a pair  $\langle ts, id \rangle$ , where ts is a natural number, and id is a unique process id. For timestamps of this format, we define MaxTS() as the function that returns the largest timestamp in lexicographic order among the pairs. Because this timestamp is unique, GetValue() simply returns the unique value associated with it. Finally, IncTS() increments the ts field by 1 and places the calling process identifier in the id field. The cost of using this building block is an additional  $O(\log n)$  bits to store a timestamp. However, this gives a total order on the timestamps which can yield stronger consistency conditions.

• Write-back phase in the read procedure: When we do not use this building block, function OptionalWriteBack() in the read procedure of the generic algorithm will simply do nothing and return.

If the building block is used, function OptionalWriteBack() will select a quorum and write the value and timestamp returned from GetValue() and MaxTS() to each of the servers in the quorum. Then it waits until it receives all the acknowledgements from each server. The cost of using this building block is an extra O(c) messages, where c is the size of the biggest quorum in the system. Furthermore, the time for a read is increased by a round-trip message delay. However, we can obtain stronger consistency conditions by using this building block.

• Local cache on clients: If we do not keep a local cache at each client, function ChooseViews() in the generic algorithm will collect the query result from each server in a certain quorum and form a view.

If we do use this building block, then each client will keep a local cache that stores the latest value-timestamp pair that it knows about. In other words, if the latest operation this client has performed is a write operation, then the local cache holds the value-timestamp pair that has been sent to update a quorum of servers; if it is a read operation, then the local cache holds what the read has returned. Function ChooseView() will form a view by combining the query result from a certain quorum and the current content in the local cache. The cost of using this building block is that clients now have to keep this information for each shared variable and thus it introduces space and robustness issues. As with the other two techniques, however, this will also yield a stronger consistency condition.

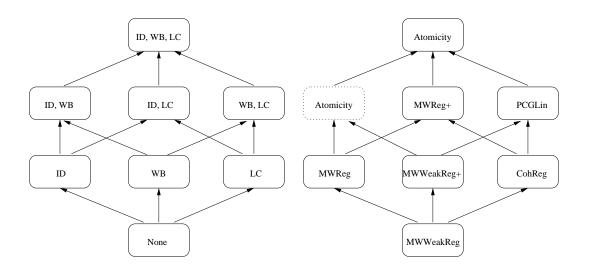

The overall result of our study is shown in Figure 2. The left lattice in Figure 2 shows all the algorithms instantiated from the generic algorithm by applying different combinations of the building blocks. We use "ID" to denote the fact that the first

building block gets used when instantiating the algorithm, and "WB" for the second, and "LC" the third. So for example, the algorithm represented by "ID, WB" is the one that uses process id in the timestamp and a write-back phase in the read. The right lattice in Figure 2 shows the corresponding consistency conditions that are yielded from the algorithms. An arrow from consistency condition A to consistency condition B indicates B is stronger than A. As we will present later in Section I, all the consistency conditions in the right lattice of Figure 2, except atomicity and MWReg+, are possible definitions of multi-writer regularity in the sense that when there is only a single writer in the system, all the definitions are equivalent to SWReg (MWReg+ is stronger than SWReg, but it is still weaker than atomicity.).

In the remainder of this chapter, we will walk up the lattice and introduce each of the possible definitions of multi-writer regularity and their implementation algorithms. It is worth noting that right now we only focus on a single-variable shared memory. Later in Chapter IV, we will show how to extend our results to a multi-variable shared memory system.

Fig. 2. Lattice of algorithms and consistency conditions

# B. MWWeakReg

# Specifying MWWeakReg

Our first proposed definition for multi-writer regularity is simply to use Definition 5, which we restate here with a new name.

**Definition 7 (MWWeakReg)** A schedule  $\sigma$  satisfies MWWeakReg if, for all read operations r in  $ops(\sigma)$ , there exists a permutation  $\pi_r$  of  $writes(\sigma) \cup \{r\}$  such that:

- $\pi_r$  is legal, and

- $\pi_r$  is  $\sigma$ -consistent.

A shared memory object satisfies MWWeakReg if all schedules on that object satisfy MWWeakReg.

Informally, a schedule  $\sigma$  satisfies MWWeakReg if each read  $r \in ops(\sigma)$  returns the value of some write w that either overlaps or precedes r in  $\sigma$ , as long as no other write falls completely between w and r. Note that this definition allows different reads to behave as though the set of writes occurred in different orders, as long as all such orderings are consistent with the partial order of the writes in  $\sigma$ .

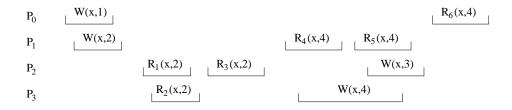

Fig. 3. Schedule that satisfies MWWeakReg

Figure 3 shows a schedule that satisfies MWWeakReg. (In our figures, W(x, v) denotes a write operation that writes value v to variable x, and R(x, v) denotes a

read operation on variable x that returns value v. We will use similar schedules to illustrate other proposed definitions. The schedules differ in the return values of some of the read operations.) The permutation for each read operation is given below. It is easy to verify that all the permutations are legal and  $\sigma$ -consistent.

```

\begin{array}{lll} R_1 \colon & W(x,2), W(x,1), R_1(x,1), W(x,4), W(x,3) \\ R_2 \colon & W(x,1), W(x,2), R_2(x,2), W(x,3), W(x,4) \\ R_3 \colon & W(x,1), W(x,2), R_3(x,2), W(x,4), W(x,3) \\ R_4 \colon & W(x,1), W(x,2), W(x,4), R_4(x,4), W(x,3) \\ R_5 \colon & W(x,1), W(x,2), R_5(x,2), W(x,3), W(x,4) \\ R_6 \colon & W(x,1), W(x,2), W(x,3), W(x,4), R_6(x,4) \end{array}

```

# 2. Implementing MWWeakReg

We name the implementation algorithm for MWWeakReg *Alg\_None*, which does not use any of the building blocks introduced in Section A.

The following lemma states that the *timestamp order* (numerical order by timestamp) of certain operations extends the partial order  $<_{\sigma}$ .

**Lemma 2** For any schedule  $\sigma$  on a shared register implemented by Alg\_None, there exist the following relationships between the operations and their timestamps:

- (a) For any read operation r and any write operation w: if  $w <_{\sigma} r$ , then  $ts(w) \le ts(r)$ .

- (b) For any two write operations  $w_1$  and  $w_2$ : if  $w_1 <_{\sigma} w_2$ , then  $ts(w_1) < ts(w_2)$ .

**Proof.** (a) Suppose write w ends before read r begins in  $\sigma$ . Let s be a server process that is in the intersection of the quorum that w uses for its update (Lines 7-8) and the quorum that r uses for its query (Lines 1-2). According to Lemma 1, the sequence of timestamp values taken on at s is non-decreasing. Since w finishes before r starts, s returns to r a timestamp that is at least ts(w). Since r chooses the value associated with the largest timestamp returned from its query, r's timestamp is no less than w's.

(b) Using a similar argument to that in (a), we can show that some server process s returns to  $w_2$  a timestamp that is at least as large as  $ts(w_1)$ . Since  $ts(w_2)$  is larger than the largest timestamp obtained in the query,  $w_2$ 's timestamp is larger than  $w_1$ 's.

**Theorem 1** Algorithm Alg\_None implements MWWeakReg.

**Proof.** Consider any execution of Alg\_None and let  $\sigma$  be its schedule. For each read operation r in  $\sigma$ , we construct  $\pi_r$  as follows. We partition the set of writes into two subsets:

- The set of writes that begin before r ends and whose timestamps are at most that of r,

- the set of all remaining writes

Each of these two sets is arranged in increasing order of timestamp; writes with identical timestamps are ordered arbitrarily with the exception that for the first set, the write operation that r reads from will be arranged as the last operation in the first sequence. We append r at the end of the first sequence and then append the second sequence to the first sequence.

The reader can easily verify that the resulting sequence satisfies the two conditions of MWWeakReg.

Now let us take a look on how Alg\_None can generate the schedule in Figure 3. We assume that we have a quorum system on three server processes A, B and C, with every set of two server processes forming a quorum. We also assume that the initial value and timestamp of the shared object is (0,0) in each server's local copy. Figure 4 shows an execution of Alg\_None on four processes, whose projection onto the set of

invocations and responses of the shared register x is the schedule shown in Figure 3. The following items will help understand the figure:

- Steps in boldface are invocations or responses on the share register.

- query(A) = (v, t) means querying server A gets a value-timestamp pair of (v, t).

- update(A, (v, t)) means updating the local copy of server A with value-timestamp pair of (v, t).

- ts := 1 means we choose timestamp value 1 for the succeeding updates.

We will use the same model and the same denotation afterwards when illustrating how an implementation algorithm could generate a certain schedule.

We now explain the purpose of demonstrating these executions. Suppose we have two consistency conditions  $C_1$  and  $C_2$  with  $C_1 \subset C_2$ , and algorithm A. If we prove that algorithm A implements consistency condition  $C_2$  (i.e., every execution of A satisfies  $C_2$ ), we have not shown every schedule in  $C_2$  can be generated by A. In fact, it is possible that A actually generates the more stringent condition  $C_1$ . By showing that A generates at least one schedule not in  $C_1$ , we obtain some knowledge that A is not "too strong".

## C. MWReg

MWWeakReg is actually a very weak consistency condition, as the read operations do not have a common view on the order of preceding write operations even for the read operations performed by the same process. For instance, in Figure 3,  $p_1$ 's first read  $R_4$  reflects the write of 4, but  $p_1$ 's next read  $R_5$  does not: the later read returns 2 even though the write of 2 precedes the write of 3. It might, therefore, be desirable to construct a stronger definition of regularity for the multi-writer case.

```

p_3

start W(x,1)

query(A) = (0,0)

start W(x,2)

query(A) = (0,0)

query(B) = (0,0)

ts := 1

query(C) = (0,0)

update(C,(1,1)) \\

ts := 1

update(A,(1,1))

update(B,(2,1))

ack

update(C,(2,1))

ack

start R_1(x)

query(A) = (1,1)

start R_2(x)

query(B) = (2,1)

query(B) = (2,1)

return 1

query(C) = (2,1)

return 2

start R_3(x)

query(A) = (1,1)

query(C) = (2,1)

return 2

start R_4(x)

start W(x,4)

query(B) = (2,1)

query(A) = (1,1)

query(B) = (2,1)

ts := 2

update(A, (4, 2))

query(A) = (4, 2)

return 4

start R_5(x)

start W(x,3)

query(B) = (2,1)

query(B) = (2,1)

update(B, (4, 2))

query(C) = (2,1)

ack

return 2

query(C)=(2,1)

ts := 2

update(A,(3,2)) \\

update(C,(3,2))

ack

start R_6(x)

query(B) = (4, 2)

query(C) = (3, 2)

return 4

```

Fig. 4. An execution of Alg\_None that generates the schedule in Figure 3. Time increases going down the page.

# 1. Specifying MWReg

Consider the schedule shown in Figure 5. We say a write is relevant to a read if the invocation of the write is before the response of the read. In this example, W(x, 1) and W(x, 2) are relevant to all the read operations, and W(x, 3) is relevant to  $R_5$  and  $R_6$  only. For any two read operations in this schedule, the write operations that are relevant to both reads will be observed in the same order and that order extends  $<_{\sigma}$ . For example, consider read operation  $R_1$  and  $R_2$ . The write operations by  $p_0$  and  $p_1$  are relevant to both reads and they are observed by the two reads in the same order as W(x, 1), W(x, 2). This is not true in the schedule shown in Figure 3, as the same two reads cannot agree on the same order of the two writes.

Fig. 5. Schedule that satisfies MWReg

The restriction on the common order of all the "relevant" writes is stronger than what MWWeakReg requires. In order to accommodate behavior of this kind, we propose a more sophisticated definition for our second and stronger version of multi-writer regularity, by requiring any pair of reads to agree only on the ordering of writes that are "relevant" to both of them. Toward this end, we use the following additional notation:  $writes_{\leftarrow r}(\sigma) = \{w | w \in writes(\sigma) \text{ and } w \text{ begins before } r \text{ ends in } \sigma\}.$

**Definition 8 (MWReg)** A schedule  $\sigma$  satisfies MWReg if there exists a permutation  $\pi$  of  $ops(\sigma)$  such that, for all read operations r in  $ops(\sigma)$ , the projection  $\pi_r$  of  $\pi$  onto  $writes_{\leftarrow r}(\sigma) \cup \{r\}$  satisfies:

- $\pi_r$  is legal, and

- $\pi_r$  is  $\sigma$ -consistent.<sup>1</sup>

A shared memory object satisfies MWReg if all schedules on that object satisfy MWReg.

This definition is similar to that of MWWeakReg, except that for any two reads  $r_1$  and  $r_2$ , the set of writes that do not strictly follow either  $r_1$  or  $r_2$  must be perceived by both reads as occurring in the same order. As before, each read returns the value of an overlapping write or of the last preceding write in the order.

The schedule in Figure 5 satisfies MWReg as shown by the following argument. Let  $\pi = W(x,1), W(x,2), R_1(x,2), R_2(x,2), R_3(x,2), R_5(x,2), W(x,3), W(x,4),$  $R_4(x,4), R_6(x,4)$ . Then the projections for the read operations are:

$R_1: \quad W(x,1), W(x,2), R_1(x,2)$   $R_2: \quad W(x,1), W(x,2), R_2(x,2)$   $R_3: \quad W(x,1), W(x,2), R_3(x,2)$   $R_4: \quad W(x,1), W(x,2), W(x,4), R_4(x,4)$   $R_5: \quad W(x,1), W(x,2), R_5(x,2), W(x,3), W(x,4)$   $R_6: \quad W(x,1), W(x,2), W(x,3), W(x,4), R_6(x,4),$

Notice that the projection for  $R_4$  does not include W(x,3) since it is not relevant to the read. It is easy to verify that all the projections are legal and  $\sigma$ -consistent.

## 2. Implementing MWReg

We implement a shared variable satisfying MWReg by using the first building block in the generic algorithm, that is, adding the process id (as in [20]) to the timestamps used by the generic algorithm. Since no individual process chooses the same ts value for two different writes, each write operation is guaranteed a unique timestamp value.

<sup>&</sup>lt;sup>1</sup>Note that if there are only a finite number of reads in a given execution, the writes after the last read are not constrained by MWReg to appear in any particular order. We consider this to be acceptable, as such writes are never observed.

This ensures that no matter how many write operations overlap, all read operations that begin after all these write operations finish are able to agree on which is the "last" write. Note that this is a commonly used approach in the implementation of shared variables using quorum systems. We name the resulting algorithm  $Alg\_ID$ . The proof of correctness of  $Alg\_ID$  is based on the following supporting lemma:

**Lemma 3** The write operations performed using Algorithm Alg\_ID are totally ordered by timestamp, and this total order extends  $<_{\sigma}$ .

**Proof.** Because the timestamp includes the process id to break ties, the timestamp order is a total order. Since we still use the timestamp of  $Alg\_None$  as the first field in the lexicographic order, Lemma 2 implies that  $<_{\sigma}$  is preserved among the writes.

**Theorem 2** Algorithm Alg\_ID implements MWReg.

**Proof.** Consider any execution of Alg\_ID and let  $\sigma$  be its schedule. We construct the permutation  $\pi$  of  $ops(\sigma)$  as follows. We begin by ordering the write operations into a sequence according to their timestamp order. We then insert each read operation r after the write operation that r reads from and before the next write operation in the total order. Read operations with identical timestamps are ordered arbitrarily. Now we prove that for any r, the projection  $\pi_r$  of  $\pi$  satisfies the conditions in Definition 8.

The sequence  $\pi_r$  is legal by construction, as r appears immediately after the write that it reads from.

Now, consider any two operations  $op_1$  and  $op_2$  in  $\pi_r$  such that  $op_1$  finishes before  $op_2$  starts in  $\sigma$ . There are two possible cases:

•  $op_1$  and  $op_2$  are both write operations. Then according to Lemma 3 and our construction method, their order in  $\pi_r$  is  $\sigma$ -consistent.

•  $op_1$  is a write operation and  $op_2 = r$ . If r reads from  $op_1$ , then  $op_1$  appears immediately before r according to our construction. Otherwise, according to algorithm Alg\_ID, r reads from a write w whose timestamp is larger than that of  $op_1$ . Therefore, the operations appear in  $\pi_r$  in the order  $op_1$ , w, and r, and thus the order of  $op_1$  and r is again  $\sigma$ -consistent.

There are no other cases, as writes that begin after r completes are not included in  $writes_{\leftarrow r}(\sigma)$ , and thus do not appear in  $\pi_r$ .

Figure 6 shows an execution of Algorithm Alg\_ID that can generate the schedule shown in Figure 5. Comparing with Figure 4, the timestamp includes the process id in addition to the integer counter.

#### D. MWWeakReg+

MWReg strengthens MWWeakReg by requiring any two read operations to agree on a total order of the write operations that are relevant to both of them and that total order extends  $<_{\sigma}$ . An alternative way to strengthen MWWeakReg is to require any two read operations to agree on a partial order of all the write operations and that extends  $<_{\sigma}$ . This section explores this alternative.

### 1. Specifying MWWeakReg+

Before we introduce MWWeakReg+, let us define a causal order relationship among read and write operations on a shared variable. For a given schedule  $\sigma$  and a readsfrom function on  $\sigma$ , the causal order  $<_{co}$  on  $ops(\sigma)$  is defined as follows:

- if two operations  $op_1 <_{\sigma} op_2$ , then  $op_1 <_{co} op_2$ ,

- if  $op_2$  reads from  $op_1$ , then  $op_1 <_{co} op_2$ ,

```

p_0

p_1

p_2

p_3

start W(x,1)

query(A) = (0, [0, 0])

start W(x,2)

\operatorname{query}(B) = (0,[0,0])

query(A) = (0, [0, 0])

query(C) = (0, [0, 0])

ts := [1, 0]

update(C,(1,[1,0]))

ts := [1, 1]

update(A,(1,[1,0]))

update(B,(2,[1,1]))

ack

update(C,(2,[1,1])) \\

ack

start R_1(x)

query(A) = (1, [1, 0])

start R_2(x)

\operatorname{query}(B) = (2,[1,1])

\operatorname{query}(B) = (2,[1,1])

return 2

query(C) = (2, [1, 1])

return 2

start R_3(x)

query(A) = (1, [1, 0])

query(C) = (2, [1, 1])

return 2

start R_4(x)

start W(x,4)

query(A) = (1, [1, 0])

query(B) = (2, [1, 1])

query(B) = (2, [1, 1])

ts := [2, 3]

update(A, (4, [2, 3]))

query(A) = (4, [2, 3])

return 4

start R_5(x)

start W(x,3)

query(B) = (2, [1, 1])

query(B) = (2, [1, 1])

update(B,(4,[2,3]))

query(C) = (2, [1, 1])

ack

query(C) = (2, [1, 1])

return 2

ts := [2, 2]

update(A, (3, [2, 2]))

update(C, (3, [2, 2])) \\

start R_6(x)

query(B) = (4, [2, 3])

query(C) = (3, [2, 2])

return 4

```

Fig. 6. An execution of Alg\_ID that generates the schedule in Figure 5.

• if  $op_1 <_{co} op_3$  and  $op_3 <_{co} op_2$ , then  $op_1 <_{co} op_2$ .

Given a schedule  $\sigma$ , and a reads-from function on  $\sigma$ , a permutation  $\pi$  of a subset of  $ops(\sigma)$  is co-consistent if, for any operations  $o_1$  and  $o_2$  in  $\pi$ ,  $o_1$  precedes  $o_2$  in  $\pi$  whenever  $o_1 <_{co} o_2$ . As we can see, co-consistency is stronger than  $\sigma$ -consistency since  $<_{co}$  extends  $<_{\sigma}$  by taking into consideration the "read from" relations between reads and writes<sup>2</sup>.

**Lemma 4**  $<_{co}$  is a partial order.

**Proof.** Suppose in contradiction  $<_{co}$  is not a partial order. Let C be a shortest cycle in  $<_{co}$ . Then C is of the form  $op_0, op_1, \ldots, op_{m-1}$  for some even  $m \geq 2$ , where, for all  $i, 1 \leq i \leq m/2$ ,

- $op_{2i-1}$ , a read on variable  $x_i$ , reads from  $op_{2i-2}$ , a write on  $x_i$ , and

- $op_{2i-1} <_{\sigma} op_{(2i) \mod m}$ .

I.e., the cycle consists of alternating reads and writes, with each read reading from the preceding write, and each write strictly following the preceding read. Note that read operations have odd index and write operations have even index.

For each  $i, 1 \le i \le m/2$ ,  $op_{2i-2}$  begins before  $op_{2i-1}$  ends (by definition of readsfrom), and  $op_{2i-1}$  ends before  $op_{(2i) \mod m}$  begins (by definition of  $<_{\sigma}$ ). Thus  $op_0$  ends before  $op_0$  begins, which is a contradiction.

MWWeakReg+ strengthens MWWeakReg by requiring that the permutation for each read is co-consistent.

<sup>&</sup>lt;sup>2</sup>Our definition of co-consistency is not the same as causal consistency ([4]), which is weaker than real-time ordering, as operations at different processes that are not causally related do not have to be ordered the same as they appear in real time.

**Definition 9 (MWWeakReg+)** A schedule  $\sigma$  satisfies MWWeakReg+ if there is a reads-from function on  $\sigma$  such that for all read operations r in  $ops(\sigma)$ , there exists a permutation  $\pi_r$  of  $writes(\sigma) \cup \{r\}$  such that:

- $\pi_r$  is legal, and

- $\pi_r$  is co-consistent.

A shared memory object satisfies MWWeakReg+ if all schedules on that object satisfy MWWeakReg+.

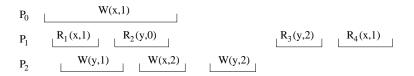

Fig. 7. Schedule that satisfies MWWeakReg+.

The schedules shown in Figure 3 and Figure 5 do not satisfy MWWeakReg+. In both schedules,  $W(x,4) <_{co} W(x,3)$ , since  $W(x,4) <_{co} R_4(x,4)$  and  $R_4(x,4) <_{co} W(x,3)$ . Thus the value returned by  $R_6$  violates the causal order. Now consider the example shown in Figure 7. The permutation for each read is given below, each of which is legal and co-consistent.

```

\begin{array}{lll} R_1 \colon & W(x,2), W(x,1), R_1(x,1), W(x,4), W(x,3) \\ R_2 \colon & W(x,1), W(x,2), R_2(x,2), W(x,4), W(x,3) \\ R_3 \colon & W(x,1), W(x,2), R_3(x,2), W(x,4), W(x,3) \\ R_4 \colon & W(x,1), W(x,2), W(x,4), R_4(x,4), W(x,3) \\ R_5 \colon & W(x,1), W(x,2), W(x,4), R_5(x,4), W(x,3) \\ R_6 \colon & W(x,1), W(x,2), W(x,4), W(x,3), R_6(x,3) \end{array}

```

# 2. Implementing MWWeakReg+

The algorithm we use to implement MWWeakReg+, which we name  $Alg_{-}WB$ , uses the second building block introduced in Section A, that is, to add a write-back phase in the read operation.

The following lemma shows how the write-back building block changes the relationship between the operations and their timestamps.

**Lemma 5** For any schedule  $\sigma$  on a shared register implemented by  $Alg_{-}WB$ , there exists the following relationship between the operations and their timestamps:

- (a) For any read operation r and any write operation w, if  $w <_{\sigma} r$ , then  $ts(w) \le ts(r)$ .

- (b) For any two write operations  $w_1$  and  $w_2$ , if  $w_1 <_{\sigma} w_2$  in  $\sigma$ , then  $ts(w_1) < ts(w_2)$ .

- (c) For any read operation r and any write operation w, if  $r <_{\sigma} w$  in  $\sigma$ , then ts(r) < ts(w).

- (d) For any two read operation  $r_1$  and  $r_2$ , if  $r_1 <_{\sigma} r_2$  in  $\sigma$ , then  $ts(r_1) \leq ts(r_2)$ .

**Proof.** The key is the non-empty intersection of quorums used in queries by read and write operations and quorums used in updates by write operations. The proof of Lemma 2 applies here to prove (a) and (b). Essentially the same argument as in (b) is used to prove (c), and essentially the same argument as in (a) is used to prove (d).

**Theorem 3** Algorithm Alg\_WB implements MWWeakReg+.

**Proof.** For any schedule  $\sigma$  resulting from an execution of Alg\_WB, we construct  $\pi_r$  for a given read operation r by the following method. We divide all the operations in

$writes(\sigma) \cup \{r\}$  into two groups:  $G_1 = \{w|ts(w) \le ts(r)\} \cup \{r\}$ , and  $G_2 = \{w|ts(w) > ts(r)\}$ .

All the operations of  $G_1$  are followed by all the operations of  $G_2$  in  $\pi_r$ . Within each group, we have the following rules:

- All the write operations in  $G_1$  are arranged by their timestamp order. The write operation that r reads from is put at the end, followed immediately by r.

- All the operations in  $G_2$  are ordered by their timestamp value. If two operations have the same timestamp value, arrange them with arbitrary order.

$\pi_r$  is legal by our construction. Now we show that  $\pi_r$  is co-consistent. For the first bullet of our causal order definition, if  $op_1 <_{\sigma} op_2$ , then from Lemma 5 and our construction,  $op_1$  appears before  $op_2$  in  $\pi_r$ . The second bullet is also satisfied by our construction. For the third bullet, if  $op_1$  appears before  $op_3$ , which appears before  $op_2$ , then  $op_1$  appears before  $op_2$ .

Thus Alg\_WB implements a MWWeakReg+ shared variable.

Figure 8 gives an execution of algorithm Alg\_WB, which will generate the schedule shown in Figure 7.

#### E. CohReg

### 1. Specifying CohReg

As discussed earlier, MWWeakReg is very weak in the sense that even from a single process's view, the write operations can be observed in different orders by different reads. As yet another alternative to strengthen MWWeakReg, CohReg adds an additional restriction that any two read operations by the same process must observe

```

p_2

p_3

start W(x,1)

query(A) = (0,0)

start W(x,2)

query(A) = (0,0)

\operatorname{query}(B) = (0,0)

ts := 1

query(C) = (0,0)

update(C,(1,1))

ts := 1

update(A,(1,1))

update(B,(2,1))

ack

update(C,(2,1))

ack

start R_1(x)

query(A) = (1,1)

start R_2(x)

query(B) = (2,1)

query(B) = (2,1)

query(C) = (2,1)

update(B,(1,1))

update(C,(1,1))

update(A, (2, 1))

return 1

update(B,(2,1))

return 2

start R_3(x)

query(A) = (2,1)

query(C) = (1,1)

update(A,(2,1))

update(B,(2,1))

return 2

start R_4(x)

start W(x,4)

query(B) = (2,1)

query(A) = (2,1)

query(B) = (2,1)

ts := 2

update(A, (4, 2))

query(A) = (4, 2)

update(C, (4, 2))

update(A, (4, 2))

return 4

start R_5(x)

query(B) = (2,1)

start W(x,3)

query(B) = (2,1)

update(B, (4, 2))

query(C) = (4,2)

ack

update(A, (4, 2))

query(C) = (4, 2)

update(C,(4,2))

ts := 3

return 4

update(A, (3, 3))

update(C, (3, 3))

start R_6(x)

query(B) = (4, 2)

query(C) = (3,3)

update(A,(3,3))

update(B,(3,3))

return 3

```

Fig. 8. An execution of Alg\_WB that generates the schedule in Figure 7.

the write operations in the same order. Since this condition implies the previously proposed condition known as Coherence ([10]), we name it CohReg.

**Definition 10 (CohReg)** A schedule  $\sigma$  satisfies CohReg if there exists a readsfrom function on  $\sigma$  such that for each process i, there exists a permutation  $\pi_i$  of  $writes(\sigma) \cup ops(\sigma|i)$  such that:

- $\pi_i$  is legal,

- $\pi_i | i \text{ is } \sigma\text{-consistent},$

- for any read operation r by i,  $\pi_i|(writes_{\leftarrow r}(\sigma) \cup \{r\})$  is  $\sigma$ -consistent,

- for any read operation r and any write operation w by process i, if  $w <_{\sigma} r$  and r reads from another write w', then w appears before w' in  $\pi_j$  for all j; if  $r <_{\sigma} w$ , then w appears after w' in  $\pi_j$  for all j, and

- for any two read operations  $r_1$  and  $r_2$  by process i, if  $r_1 <_{\sigma} r_2$  and they read from different writes,  $w_1$  and  $w_2$  respectively, then  $w_1$  appears before  $w_2$  in  $\pi_j$  for all j.