# Handling Communications in Process Algebraic Architectural Description Languages: Modeling, Verification, and Implementation

Marco Bernardo Edoardo Bontà Alessandro Aldini

Università di Urbino "Carlo Bo" – Italy

Istituto di Scienze e Tecnologie dell'Informazione

#### Abstract

Architectural description languages are a useful tool for modeling complex software systems at a high level of abstraction. If based on formal methods, they can also serve for enabling the early verification of various properties such as component coordination and for guiding the synthesis of code correct by construction. This is the case with process algebraic architectural description languages, which are process calculi enhanced with the main architectural concepts. However, the techniques with which those languages have been equipped are mainly conceived to work with synchronous communications only. The objective of this paper is threefold. On the modeling side, we show how to enhance the expressiveness of a typical process algebraic architectural description language by including the capability of representing nonsynchronous communications in such a way that the usability of the original language is preserved. On the verification side, we show how to modify techniques for analyzing the absence of coordination mismatches like the compatibility check for acyclic topologies and the interoperability check for cyclic topologies in such a way that those checks are valid also for nonsynchronous communications. On the implementation side, we show how to generate multithreaded object-oriented software in the presence of synchronous and nonsynchronous communications in such a way that the properties proved at the architectural level are preserved at the code level.

Key words: software architecture, architectural description languages, process algebra, synchronous and nonsynchronous communications, system modeling and verification, code generation.

#### 1. Introduction

The growing complexity and the increasing size of modern software systems can be managed by adopting notations for formal or semi-formal system modeling (model-driven approach). In this way, design documents with a precise syntax can be produced and shared by all the people contributing to system development. In order to avoid delays and cost increases due to the late discovery of errors in the development process, another task that such notations should carry out is to enable the rigorous and hopefully automated analysis of system properties and to guide the synthesis of code correct by construction. For instance, it is widely recognized that property verification finds its own rightful place in the architectural design phase [38, 12]. The reason is that this phase precedes system implementation and provides support for declarative/behavioral/topological system models that are complete at a high level of abstraction.

Many architectural description languages have been proposed. Some of them – like, e.g., Wright [4, 3], Darwin/FSP [31, 32], LEDA [14], PADL [1], and  $\pi$ -ADL [35] – are based on process algebra [34, 29, 6] due to its support to compositional modeling. It is worth noting that process algebra is compositional, but not component-oriented. Thus, from the point of view of process algebra, its architectural versions are a significant step forward in terms of usability. In fact, they give special prominence to the main architectural concepts – components, connectors, and styles – while hiding the process algebraic technicalities to the software developer.

On the modeling side, this architectural upgrade has three important consequences. First, it permits to describe the behavior of the components separately from the representation of the system topology, thus overcoming the modeling difficulties deriving from the direct use of certain process algebraic operators like, e.g., parallel composition. Second, it highlights the interactions among components and the classification of their communications, thus allowing for static checks establishing system model well-formedness. Third, it fosters the reuse of the specification of single components as well as of complete systems, thus supporting the compositional and hierarchical modeling of entire system families.

On the verification side, process algebraic architectural description languages inherit all the techniques applicable to process algebra, like model checking [18] and equivalence checking [19]. In addition, such languages are equipped with ad-hoc analysis techniques (see, e.g., [4, 30, 15, 1]) mostly

based on behavioral equivalences [27], which are useful for detecting coordination mismatches that may arise when assembling together components that are correct if taken in isolation. Moreover, they can generate diagnostic information for pinpointing components responsible for mismatches.

The ad-hoc analysis techniques proposed in the literature deal only with synchronous communications. In that setting, all ports of software components are blocking. A component waiting on a synchronous input port cannot proceed until an output is sent by another component. Similarly, a component issuing an output via a synchronous output port cannot proceed until another component is willing to receive. The limitation to synchronous communications is not so restrictive for usual properties like deadlock freedom, which should hold when no communication is blocking. In contrast, the validity of other properties related to activity sequencing or message ordering may not be guaranteed in the presence of nonsynchronous communications.

In order to address the usual properties in a more general setting as well as the other properties mentioned above, the first contribution of this paper is to show how to enhance the expressiveness of a typical process algebraic architectural description language by including the capability of representing nonsynchronous communications in such a way that the usability of the original language is preserved. More specifically, we focus on PADL [1] and we extend it by means of additional qualifiers useful to distinguish among synchronous, semi-synchronous, and asynchronous ports.

Semi-synchronous ports are not blocking. A semi-synchronous port of a component succeeds if there is another component ready to communicate with it, otherwise it raises an exception so as not to block the component to which it belongs. For example, a semi-synchronous input port can be used to model accesses to a tuple space via input or read probes [25]. A semi-synchronous output port can instead be used to model the interplay between a graphical user interface and an underlying application, as the former must not block whenever the latter cannot do certain tasks requested by the user.

Analogously, asynchronous ports are not blocking. Here the reason is that the beginning and the end of the communications in which these ports are involved are completely decoupled. For instance, an asynchronous output port can be used to model output operations on a tuple space. An asynchronous input port can instead be used to model the periodical check for the presence of information received from an event notification service [16].

In the extended language, semi-synchronous ports can be easily handled with suitable semantic rules generating exceptions whenever necessary,

whereas asynchronous ports require the addition of implicit repository-like components. In any case, the semantic treatment of nonsynchronous communications is completely transparent to PADL users, as they only have to specify suitable synchronicity-related qualifiers in their architectural descriptions. Therefore, the degree of usability of the original language is unaffected.

The second contribution of this paper is to show how to modify techniques for analyzing the absence of coordination mismatches – like the compatibility check for acyclic topologies and the interoperability check for cyclic topologies introduced in [1] – in such a way that those checks can still be applied in the presence of nonsynchronous communications.

This is accomplished by viewing certain activities carried out through semi-synchronous and asynchronous ports as internal activities when performing the above mentioned checks. The reason is that each such activity has a specific outcome and takes place at a specific time instant when considered from the point of view of the individual component executing that activity. However, in the overall architecture the same activity can raise an exception (if the port is semi-synchronous and the other ports are not ready to communicate with it) or can be delayed (if the port is asynchronous and the communication is buffered). Thus, if we do not regard exceptions and all the activities carried out through asynchronous ports as internal activities at verification time, the compatibility or interoperability check may fail even in the absence of a real coordination mismatch.

The third contribution of this paper is to show how to generate multithreaded object-oriented software from process algebraic architectural descriptions including various kinds of communications in such a way that the properties proved at the architectural level are preserved at the code level. This last contribution is related to one of the big issues in the software engineering field, i.e., guaranteeing that the implementation of a software system complies with its architectural description [23]. Indeed, the purpose of automatic code generation should be not only to speed up system implementation, but also to ensure conformance by construction.

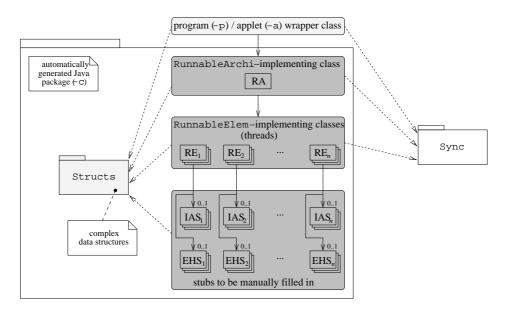

In order to bridge the gap between system modeling/verification and system implementation, we propose an approach that automatically synthesizes multithreaded Java programs from PADL descriptions containing an arbitrary combination of synchronous, semi-synchronous, and asynchronous ports. The choice of Java as target language is due to the fact that Java offers a set of mechanisms for the well-structured management of threads and their shared data, which should simplify the code generation task. Moreover, its

object-oriented nature – and specifically its encapsulation capability – makes Java an appropriate candidate for coping with the high level of abstraction of process algebraic architectural descriptions during code generation.

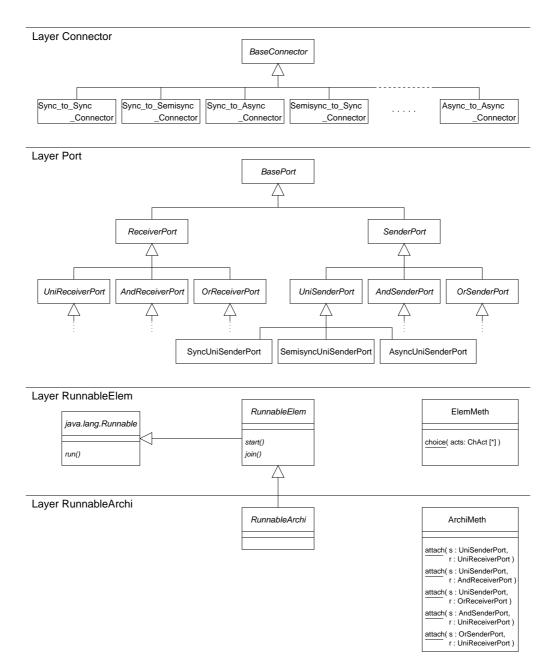

The proposed approach is divided into two phases. In the first phase, we develop an architecture-driven technique for thread coordination management. Similar to previous work (see, e.g., [37]), we advocate the provision of a suitable software package that takes care of the details of thread coordination by means of architecture-inspired units in a way that is completely transparent to the software developer. The distinguishing feature of the first phase of our proposal is that also the employment of the package should follow the same architecture-centric spirit. In other words, the use of the package units should be guided by the architectural description of the system to be developed, as this description is a well suited tool for achieving correct thread coordination in the case of concurrent object-oriented programs.

In the second phase, we handle the translation of the process algebraically specified behavior of individual software components into threads. The separation of thread behavior generation from thread coordination management turns out to be particularly appropriate in order to limit human intervention. In fact, while a completely automated and architecture-driven technique can guarantee correct thread coordination, only a partial translation based on stubs is possible for the generation of threads. In addition to the considerations of [32], in which it is shown how a disciplined process algebraic modeling is beneficial at subsequent stages, we also provide a set of guidelines for filling in stubs, which guarantee the preservation at the code level of properties proved on the architectural description of the system under construction.

This paper, which is a full and revised version of [10, 8, 9], is organized as follows. After recalling PADL in Sect. 2, in Sect. 3 we extend its syntax with semi-synchronous and asynchronous ports and we consequently revise its semantics. A running example based on a client-server system is used throughout both sections. In Sect. 4, we modify the architectural compatibility and interoperability checks in order to deal with nonsynchronous communications as well. The modified checks are illustrated on the architectural description of an applet-based simulator for a cruise control system. In Sect. 5, we present the two-phase approach for synthesizing multithreaded Java software from PADL descriptions including synchronous and nonsynchronous communications. The approach is exemplified by means of the same cruise control system simulator as the previous section. Finally, in Sect. 6 we provide some concluding remarks and directions for future work.

### 2. The Architectural Description Language PADL

PADL is a process algebraic architectural description language. In this section, after recalling some basic notions of process algebra (Sect. 2.1), we present PADL syntax (Sect. 2.2) and semantics (Sect. 2.3) by illustrating them through a client-server running example. For a complete presentation and comparisons with related work, the interested reader is referred to [1].

# 2.1. Process Algebra

Process calculi [34, 29, 6] provide a set of operators by means of which the behavior of a system can be described in an action-based, compositional way. Given a set  $Name = Name_v \cup \{\tau\}$  of action names including  $\tau$  for denoting an invisible action, together with a set  $Relab = \{\varphi : Name \rightarrow Name \mid \varphi^{-1}(\tau) = \{\tau\}\}$  of relabeling functions preserving action visibility, we consider a process calculus PA with the following process term syntax:

| $P ::= \underline{0}$ | inactive process        |                                   |

|-----------------------|-------------------------|-----------------------------------|

| B                     | process constant        | $(B \stackrel{\Delta}{=} P)$      |

| a.P                   | action prefix           | $(a \in \mathit{Name})$           |

| P+P                   | alternative composition |                                   |

| $ P _S P$             | parallel composition    | $(S \subseteq Name_{\mathbf{v}})$ |

| P/H                   | hiding                  | $(H \subseteq Name_{\mathbf{v}})$ |

| $P[\varphi]$          | relabeling              | $(\varphi \in Relab)$             |

Operational semantic rules map every process term P of PA to a state-transition graph  $[\![P]\!]$  called labeled transition system. In this graph, each state corresponds to a process term derivable from P, the initial state corresponds to P, and each transition is labeled with the corresponding action.

Observed that no rule is necessary for the inactive process  $\underline{0}$  – as  $\underline{[0]}$  must be a single-state graph with no transitions – the operational semantic rules for dynamic operators (action prefix and alternative composition) and process constants are the following:

ants are the following:

$$\begin{array}{c}

a \cdot P \xrightarrow{a} P & \xrightarrow{B \stackrel{\triangle}{=}} P & P \xrightarrow{a} P' \\

\hline

B \xrightarrow{a} P' & B \xrightarrow{a} P' \\

\hline

P_1 \xrightarrow{a} P' & P_2 \xrightarrow{a} P' \\

\hline

P_1 + P_2 \xrightarrow{a} P' & P_1 + P_2 \xrightarrow{a} P'

\end{array}$$

Process a cdot P can execute an action with name a and then behaves as P. Process  $P_1 + P_2$  behaves as either  $P_1$  or  $P_2$  depending on which of them executes an action first (nondeterministic choice). Constant B behaves as the process term occurring in its possibly recursive defining equation.

The operational semantic rules for static operators (parallel composition, hiding, and relabeling) are the following:

$$\begin{array}{c|c}

P_1 \xrightarrow{a} P_1' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2 & P_2 \xrightarrow{a} P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2 & P_2 & a \in S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \in S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \notin S \\

\hline

P_1 \parallel_S P_2 \xrightarrow{a} P_1' \parallel_S P_2' & a \iff S \\

\hline

P_1 \parallel_S P_1 \xrightarrow{a} P_1' \parallel_S P_2' & a \iff S \\

\hline

P_1 \parallel_S P_1 \xrightarrow{a} P_1' \parallel_S P_2' & a \iff S \\

\hline

P_1 \parallel_S P_1$$

Process  $P_1 \parallel_S P_2$  behaves as  $P_1$  in parallel with  $P_2$  as long as actions are executed whose name does not belong to S. In contrast, synchronizations are forced between any action executed by  $P_1$  and any action executed by  $P_2$  that have the same name belonging to S. Process P/H behaves as P with all executed actions occurring in P made invisible. Process  $P[\varphi]$  behaves as P with all executed actions relabeled via  $\varphi$ .

Process terms are compared and manipulated by means of behavioral equivalences [27]. Among the various approaches, for PA we consider weak bisimilarity, according to which two process terms are equivalent if they are able to mimic each other's visible behavior stepwise [34].

Denoted by  $\Longrightarrow$  the extension of  $\longrightarrow$  to action sequences, we say that a symmetric relation  $\mathcal{R}$  is a weak bisimulation iff for all  $(P_1, P_2) \in \mathcal{R}$ : (i) whenever  $P_1 \stackrel{a}{\longrightarrow} P'_1$  for  $a \in Name_v$ , then  $P_2 \stackrel{\tau^*a\tau^*}{\longrightarrow} P'_2$  and  $(P'_1, P'_2) \in \mathcal{R}$ ; (ii) whenever  $P_1 \stackrel{\tau}{\longrightarrow} P'_1$ , then  $P_2 \stackrel{\tau^*}{\Longrightarrow} P'_2$  and  $(P'_1, P'_2) \in \mathcal{R}$ . Weak bisimilarity  $\approx_B$ , defined as the union of all the weak bisimulations, is a congruence with respect to all the operators except for alternative composition and has a modal characterization based on a weak variant of Hennessy-Milner logic.

#### 2.2. PADL Textual and Graphical Notations

A PADL description represents an architectural type, which is a family of software systems sharing certain constraints on the observable behavior of their components as well as on their topology.

The textual description of an architectural type starts with the name and the formal parameters (initialized with default values) of the architectural type. The textual description then comprises two sections, as shown below:

| ARCHI_TYPE           | $\triangleleft name\ and\ initialized\ formal\ parameters \gt$                                   |

|----------------------|--------------------------------------------------------------------------------------------------|

| ARCHI_BEHAVIOR       |                                                                                                  |

| :                    | :                                                                                                |

| ARCHI_ELEM_TYPE      | $\triangleleft AET \ name \ and \ formal \ parameters \triangleright$                            |

| BEHAVIOR             | <i>⊲sequence of PA defining equations built from</i> stop, action prefix, choice, and recursion⊳ |

| INPUT_INTERACTIONS   | $\triangleleft input\ uni/and/or-interactions \triangleright$                                    |

| OUTPUT_INTERACTIONS  | $\triangleleft output\ uni/and/or\text{-}interactions \triangleright$                            |

| :                    | :                                                                                                |

| ARCHI_TOPOLOGY       |                                                                                                  |

| ARCHI_ELEM_INSTANCES | $\triangleleft AEI \ names \ and \ actual \ parameters \triangleright$                           |

| ARCHI_INTERACTIONS   | $\triangleleft architecture\text{-}level\ AEI\ interactions \triangleright$                      |

| ARCHI_ATTACHMENTS    | $\triangleleft attachments\ between\ AEI\ local\ interactions \triangleright$                    |

| END                  |                                                                                                  |

The first section defines the behavior of the system family by means of types of software components and connectors, which are collectively called architectural element types. The definition of an AET starts with its name and its formal parameters and consists of the specification of its behavior and its interactions.

The behavior of an AET has to be provided in the form of a sequence of defining equations written in a verbose variant of PA allowing only for the inactive process (rendered as stop), the value-passing action prefix operator with a possible boolean guard condition, the alternative composition operator (rendered as choice), and recursion (behavioral invocations).

The interactions are those actions occurring in the process algebraic specification of the behavior that act as interfaces for the AET, while all the other actions are assumed to represent internal activities. Each interaction has to be equipped with two qualifiers. The first one establishes whether the inter-

action is an input or output interaction, whereas the second one describes the multiplicity of the communications in which the interaction can be involved.

We distinguish among uni-interactions mainly involved in one-to-one communications (qualifier UNI), and-interactions guiding inclusive one-to-many communications like multicasts (qualifier AND), or-interactions guiding selective one-to-many communications like those between a server and its clients (qualifier OR). It can also be established that an output or-interaction depends on an input or-interaction, in order to guarantee that a selective one-to-many output is sent to the same element from which the last selective many-to-one input was received (keyword DEP).

The second section of the PADL description defines the topology of the system family. It is composed of three subsections. First, we have the declaration of the instances of the AETs – called AEIs – which represent the actual system components and connectors, together with their actual parameters. Then, we have the declaration of the architectural (as opposed to local) interactions, which are some of the interactions of the AEIs that act as interfaces for the whole systems of the family. Finally, we have the declaration of the architectural attachments among the local interactions of the AEIs, which make the AEIs communicate with each other.

An attachment is admissible only if it goes from a local output interaction of an AEI to a local input interaction of another AEI. Moreover, a local uni-interaction can be attached to only one local interaction, whereas a local and-/or-interaction can be attached to (several) local uni-interactions only.

Besides the textual notation, PADL comes equipped with a graphical notation that is an extension of the flow graph notation [34]. In an enriched flow graph, AEIs are depicted as boxes, local (resp. architectural) interactions are depicted as small black circles (resp. white squares) on the box border, and attachments are depicted as directed edges between pairs each composed of a local output interaction and a local input interaction. The small circle/square of an interaction is extended with a triangle (resp. bisected triangle) outside the AEI box if the interaction is an and-interaction (resp. or-interaction). Or-dependences are depicted as dotted edges.

**Example 2.1.** Suppose we need to model a scenario in which there is a server that can be contacted at any time by two identically behaving clients. Assume that the server has no buffer for holding incoming requests and that, after sending a request, a client cannot proceed until it receives a response from the server. The server AET can be defined as follows:

```

ARCHI_ELEM_TYPE Server_Type(void)

BEHAVIOR

Server(void; void) =

receive_request . compute_response . send_response . Server()

INPUT_INTERACTIONS OR receive_request

OUTPUT_INTERACTIONS OR send_response DEP receive_request

```

where compute\_response is an internal action, while send\_response is declared to depend on receive\_request in order to make sure that each response is sent back to the client that issued the corresponding request. Since the behavior of the two clients is identical, a single client AET suffices:

```

ARCHI_ELEM_TYPE Client_Type(void)

BEHAVIOR

Client(void; void) =

process . send_request . receive_response . Client()

INPUT_INTERACTIONS UNI receive_response

OUTPUT_INTERACTIONS UNI send_request

```

where **process** is an internal action. Finally, we declare the topology of the system as follows by using the dot notation for the local interactions:

```

ARCHI_TOPOLOGY

ARCHI_ELEM_INSTANCES

S : Server_Type();

C_1 : Client_Type();

C_2 : Client_Type()

ARCHI_INTERACTIONS

void

ARCHI_ATTACHMENTS

FROM C_1.send_request TO S.receive_request;

FROM C_2.send_request TO S.receive_request;

```

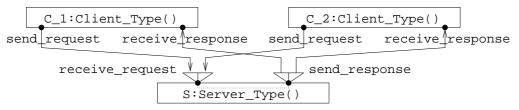

The topology is better illustrated by the following enriched flow graph:

FROM S.send\_response TO C\_1.receive\_response; FROM S.send\_response TO C\_2.receive\_response

where the dotted edge linking the bisected triangles is the or-dependence.

#### 2.3. The Semantics for PADL

The semantics for PADL is given by translation into PA. The first step of the translation focuses on the semantics of each AEI. This is defined as the behavior of the corresponding AET with all the action occurrences being preceded by the name of the AEI and the AET formal data parameters being substituted for by the corresponding AEI actual data parameters.

Let  $\mathcal C$  be an AET with  $m\in\mathbb N_{\geq 0}$  formal parameters  $fp_1,\ldots,fp_m$  and behavior given by a sequence  $\mathcal E$  of defining equations. Then the semantics of an AEI C of type  $\mathcal C$  with actual parameters  $ap_1,\ldots,ap_m$  is defined as follows, where C. introduces the dot notation on actions and  $\{\_\hookrightarrow\_,\ldots,\_\hookrightarrow\_\}$  denotes a syntactical substitution:

$$\boxed{ \llbracket C \rrbracket = C.\mathcal{E} \{ ap_1 \hookrightarrow fp_1, \dots, ap_m \hookrightarrow fp_m \} }$$

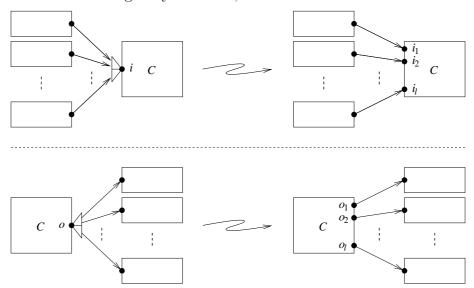

If the AEI contains local or-interactions, each of them – consistent with the fact that it guides a selective one-to-many communication – must be replaced by as many fresh local uni-interactions as there are attachments involving the considered or-interaction. The fresh local uni-interactions are then attached to the local uni-interactions of other AEIs to which the local or-interaction was originally attached, as shown below:

In that case, the semantics of C is defined as follows:

$$\llbracket C \rrbracket = or\text{-}rewrite_{\emptyset}(C.\mathcal{E}\{ap_1 \hookrightarrow fp_1, \dots, ap_m \hookrightarrow fp_m\})$$

In order to reflect the fact that an or-interaction can result in several alternative communications, function or-rewrite inductively rewrites the body of any resulting defining equation by replacing with fresh uni-interactions each occurrence of any local or-interaction whose number attach- $no(\_)$  of attachments is greater than 1. Or-dependences are dealt with by keeping track of the set FI of fresh input uni-interactions currently in force that arise from input or-interactions on which some output or-interaction depends. Here are the three basic clauses of the inductive definition of or-rewrite:

• If a is either a local input or-interaction of C on which no local output or-interaction depends, or a local output or-interaction that does not depend on any local input or-interaction, and  $attach-no(C.a) = l \ge 2$ :

$$or\text{-}rewrite_{FI}(a.P) = choice\{a_1.or\text{-}rewrite_{FI}(P), \vdots a_l.or\text{-}rewrite_{FI}(P)\}$$

• If i is a local input or-interaction of C on which a local output or-interaction depends and  $attach-no(C.i) = l \ge 2$ :

• If o is a local output or-interaction of C that depends on the local input or-interaction i and  $attach-no(C.i) = attach-no(C.o) \ge 2$  and  $i_j \in FI$ :

$$or\text{-}rewrite_{FI}(o.P) = o_j.or\text{-}rewrite_{FI}(P)$$

**Example 2.2.** Consider the client-server system described in Ex. 2.1. Then  $\llbracket C_{-1} \rrbracket$  and  $\llbracket C_{-2} \rrbracket$  coincide with the defining equation for Client, where action names are preceded by  $C_{-1}$  and  $C_{-2}$ , respectively. In contrast,  $\llbracket S \rrbracket$  is given by the following defining equation obtained from the one for Server after rewriting the occurring or-interactions:

```

RewSer(void; void) =

choice

{

S.receive_request_1 . S.compute_response . S.send_response_1 . RewSer(),

S.receive_request_2 . S.compute_response . S.send_response_2 . RewSer()

}

```

The second step of the translation defines the meaning of any set of AEIs  $\{C_1, \ldots, C_n\}$  and hence of an entire architectural description. Fixed an AEI  $C_j$  in the set, let  $\mathcal{LI}_{C_j}$  be the set of local interactions of  $C_j$  and  $\mathcal{LI}_{C_j;C_1,\ldots,C_n} \subseteq \mathcal{LI}_{C_j}$  be the set of local interactions of  $C_j$  attached to  $\{C_1,\ldots,C_n\}$ .

In order to make the process terms representing the semantics of these AEIs communicate in the presence of attached interactions having different names – in PA only actions with the same name can synchronize – we need a set  $\mathcal{S}(C_1,\ldots,C_n)$  of fresh action names, one for each pair of attached local uni-interactions in  $\{C_1,\ldots,C_n\}$  and for each set of local uni-interactions attached to the same local and-interaction in  $\{C_1,\ldots,C_n\}$ . In order to ensure the uniqueness of the elements of  $\mathcal{S}(C_1,\ldots,C_n)$ , each of them is built by concatenating through symbol # all the original names in the corresponding maximal set of attached local interactions. Then, we need suitable injective relabeling functions  $\varphi_{C_j;C_1,\ldots,C_n}$  mapping each set  $\mathcal{LI}_{C_j;C_1,\ldots,C_n}$  to  $\mathcal{S}(C_1,\ldots,C_n)$  in such a way that:

$$\varphi_{C_j;C_1,\dots,C_n}(a_1) = \varphi_{C_g;C_1,\dots,C_n}(a_2)$$

if and only if  $C_j.a_1$  and  $C_g.a_2$  are attached to each other or to the same and-interaction.

The interacting semantics of  $C_j$  with respect to  $\{C_1, \ldots, C_n\}$  is defined as follows:

$$[\![C_j]\!]_{C_1,\dots,C_n} = [\![C_j]\!] [\varphi_{C_j;C_1,\dots,C_n}]$$

In general, the interacting semantics of  $\{C'_1, \ldots, C'_{n'}\} \subseteq \{C_1, \ldots, C_n\}$  with respect to  $\{C_1, \ldots, C_n\}$  is defined as follows (assuming parallel composition to be left associative):

where  $\mathcal{S}(C'_j, C'_g; C_1, \ldots, C_n) = \mathcal{S}(C'_j; C_1, \ldots, C_n) \cap \mathcal{S}(C'_g; C_1, \ldots, C_n)$  is the pairwise synchronization set of  $C'_j$  and  $C'_g$  with respect to  $\{C_1, \ldots, C_n\}$ , with  $\mathcal{S}(C'_j; C_1, \ldots, C_n) = \varphi_{C'_j; C_1, \ldots, C_n}(\mathcal{LI}_{C'_j; C_1, \ldots, C_n})$  being the synchronization set of  $C'_j$  with respect to  $\{C_1, \ldots, C_n\}$ .

Finally, the semantics of an architectural type  $\mathcal{A}$  formed by the set of AEIs  $\{C_1, \ldots, C_n\}$  is defined as follows:

$$\boxed{\llbracket \mathcal{A} \rrbracket = \llbracket C_1, \dots, C_n \rrbracket_{C_1, \dots, C_n}}$$

**Example 2.3.** Consider again the client-server system of Ex. 2.1. Then the semantics of the entire description is given by the following process term:

### 3. Semi-Synchronous and Asynchronous Interactions

The interactions occurring in a PADL description can be involved only in synchronous communications, hence input and output interactions represent blocking operations. In order to increase the expressiveness of PADL, within the interface of each AET we will provide support for distinguishing among synchronous, semi-synchronous, and asynchronous interactions. The usability of the language will be preserved by means of suitable synchronicity-related qualifiers that are made available to PADL users.

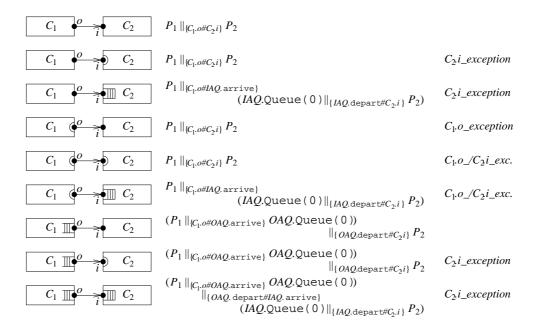

In this section – in which we use the same client-server running example as the previous section – we first enrich the textual and graphical notations in order to express nonsynchronous interactions (Sect. 3.1). Then, we discuss the treatment of semi-synchronous interactions through additional semantic rules (Sect. 3.2) and of asynchronous interactions through additional implicit AEIs (Sect. 3.3). Finally, we revise the semantics accordingly (Sect. 3.4). The nine resulting forms of communication are summarized by Fig. 1, with the first one being the only one originally available in PADL.

#### 3.1. Enriching PADL Textual and Graphical Notations

In the textual notation of PADL, we introduce a third qualifier for each interaction, to be used in the definition of the AETs. Such a qualifier establishes whether the interaction is synchronous (keyword SYNC), semi-synchronous (keyword SSYNC), or asynchronous (keyword ASYNC).

Figure 1: Forms of communications available in the extension of PADL

While a synchronous interaction blocks the AEI executing it as long as the interactions attached to it are not ready, this is not the case with nonsynchronous interactions. More precisely, a semi-synchronous interaction raises an exception if it cannot take place immediately due to the (temporary or permanent) unavailability of the interactions attached to it, so that the AEI executing it can proceed anyway. Likewise, in the case of an asynchronous interaction, the beginning and the end of the communication are decoupled, hence the AEI executing the interaction will never block.

A boolean variable  $s.\mathtt{success}$  is associated with each semi-synchronous interaction s. This implicitly declared variable is automatically set at each execution of s and is made available to PADL users in order to catch exceptions. In this way, it is easy to model different behaviors to be undertaken depending on the outcome of the execution of s.

In the graphical notation, a semi-synchronous interaction is depicted by extending the small circle/square of the interaction with an arc inside the AEI box. An asynchronous interaction, instead, is depicted by extending the small circle/square with a buffer inside the AEI box.

**Example 3.1.** Consider once more the client-server system of Ex. 2.1. Since

the server has no buffer for incoming requests, each client may want to send a request only if the server is not busy, so that the client can keep working instead of passively waiting for the server to become available. This can be achieved by transforming send\_request into a semi-synchronous interaction and by redefining the behavior of Client\_Type as follows:

On the other hand, the server should not make any assumption about the status of its clients, as these may be much more complicated than the description above. In particular, when sending out a response to a client, the server should not be blocked by the temporary or permanent unavailability of that client, as this would decrease the quality of service. This can be achieved by using keyword ASYNC in the declaration of output interaction send\_response within the definition of Server\_Type.

## 3.2. Semantics of Semi-Synchronous Interactions: Additional Rules

A local semi-synchronous interaction s executed by an AEI C gives rise to a transition labeled with C.s within  $[\![C]\!]$ , and hence to the setting of the related success variable to true. However, in an interacting context, this transition has to be relabeled with  $C.s\_exception$  if s cannot immediately participate in a communication. This is accomplished by means of additional semantic rules encoding a context-sensitive variant of the relabeling operator.

Suppose that the local output interaction o of an AEI  $C_1$  is attached to the local input interaction i of an AEI  $C_2$ , where  $C_1.o \# C_2.i$  is their fresh name. Let  $P_1$  (resp.  $P_2$ ) be the process term representing the current state of  $[\![C_1]\!]_{C_1,C_2}$  (resp.  $[\![C_2]\!]_{C_1,C_2}$ ) and  $S = \mathcal{S}(C_1,C_2;C_1,C_2)$ .

If o is synchronous and i is semi-synchronous – which is the second form of communication depicted in Fig. 1 – then the following additional semantic rule is necessary for handling exceptions:

$$P_1 \xrightarrow{C_1.o\#C_2.i} P_1' \qquad P_2 \xrightarrow{C_1.o\#C_2.i} P_2'$$

$$P_1 \parallel_S P_2 \xrightarrow{C_2.i\_exception} P_1 \parallel_S P_2' \qquad C_2.i.\texttt{success} = \texttt{false}$$

In the symmetric case in which o is semi-synchronous and i is synchronous – which corresponds to the fourth form of communication depicted in Fig. 1 – the following additional semantic rule is necessary for handling exceptions:

Finally, in the case in which both o and i are semi-synchronous – which corresponds to the fifth form of communication depicted in Fig. 1 – we have the previous two additional semantic rules together.

3.3. Semantics of Asynchronous Interactions: Additional Implicit AEIs While semi-synchronous interactions are dealt with by means of suitable semantic rules accounting for possible exceptions, asynchronous interactions need a different treatment because of the decoupling between the beginning and the end of the communications in which those interactions are involved.

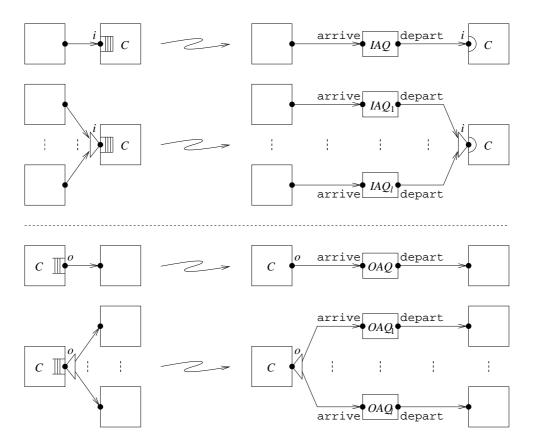

After the or-rewriting process, for each local asynchronous uni-/and-interaction of an AEI C we have to introduce additional implicit AEIs that behave like unbounded buffers, thus realizing the third, sixth, seventh, eighth, and ninth form of communication depicted in Fig. 1. As shown in Fig. 2, in the case of a local asynchronous and-interaction, it is necessary to introduce as many additional implicit AEIs as there are attachments involving the and-interaction.<sup>1</sup>

Each additional implicit input asynchronous queue (IAQ) and output asynchronous queue (OAQ) is of the following type, where arrive is an always-enabled input synchronous uni-interaction while depart is an output synchronous uni-interaction enabled only if the buffer is not empty:

<sup>&</sup>lt;sup>1</sup>In [10], a single additional implicit AEI was introduced even in the case of a local asynchronous and-interaction, thus determining an unnecessary synchronization among the AEIs attached to the and-interaction.

Figure 2: Topological management of local asynchronous uni-/and-interactions

```

ARCHI_ELEM_TYPE Async_Queue_Type(void)

BEHAVIOR

Queue(int n := 0;

void) =

choice

{

cond(true) -> arrive . Queue(n + 1),

cond(n > 0) -> depart . Queue(n - 1)

}

INPUT_INTERACTIONS SYNC UNI arrive

OUTPUT_INTERACTIONS SYNC UNI depart

```

In the case of a local input asynchronous uni-/and-interaction i of C, each local output uni-interaction originally attached to i is implicitly re-attached to the **arrive** interaction of one of the additional implicit IAQs. By contrast,

the depart interaction of each additional implicit IAQ is implicitly attached to i, which is implicitly converted into a semi-synchronous interaction. Note that i becomes semi-synchronous because the communications between the depart interactions and i must not block C whenever some buffers are empty.

In the case of a local output asynchronous uni-/and-interaction o of C, this interaction is implicitly converted into a synchronous interaction and reattached to each arrive interaction of the additional implicit OAQs. Note that o is never blocked because all arrive interactions are always enabled. By contrast, the depart interaction of each additional implicit OAQ is attached to one of the input interactions originally attached to o.

## 3.4. Revising PADL Semantics

Due to the way nonsynchronous interactions have been managed, we only need to revise the definition of the semantics of an AEI in isolation, while all the subsequent definitions given in Sect. 2.3 are unchanged. More precisely, we only have to take into account the possible presence of additional implicit AEIs acting as unbounded buffers for local asynchronous interactions.

**Definition 3.2.** Let  $\mathcal{C}$  be an AET,  $fp_1, \ldots, fp_m$  be its  $m \in \mathbb{N}_{\geq 0}$  formal parameters, and  $\mathcal{E}$  be a sequence of defining equations giving its behavior. Let C be an AEI of type  $\mathcal{C}$  with actual parameters  $ap_1, \ldots, ap_m$  consistent by order and type with the formal parameters. Suppose that C has:

- $h \in \mathbb{N}_{\geq 0}$  local input asynchronous uni-interactions  $i_1, \ldots, i_h$  handled through the related additional implicit AEIs  $IAQ_1, \ldots, IAQ_h$ ;

- $h' \in \mathbb{N}_{\geq 0}$  local input asynchronous and-interactions  $i'_1, \ldots, i'_{h'}$ , where each  $i'_j$  is handled through the  $attach-no(C.i'_j)=il_j$  related additional implicit AEIs  $IAQ_{j,1}, \ldots, IAQ_{j,il_j}$ ;

- $k \in \mathbb{N}_{\geq 0}$  local output asynchronous uni-interactions  $o_1, \ldots, o_k$  handled through the related additional implicit AEIs  $OAQ_1, \ldots, OAQ_k$ ;

- $k' \in \mathbb{N}_{\geq 0}$  local output asynchronous and-interactions  $o'_1, \ldots, o'_{k'}$ , where each  $o'_j$  is handled through the  $attach-no(C.o'_j) = ol_j$  related additional implicit AEIs  $OAQ_{j,1}, \ldots, OAQ_{j,ol_j}$ .

Then the semantics of C is the result of a cascade of function applications:

$$[\![C]\!] = o\text{-}and_{ol_{k'}}^{k'}(...o\text{-}and_{ol_{1}}^{1}(o\text{-}uni_{k}(i\text{-}and_{il_{h'}}^{h'}(...i\text{-}and_{il_{1}}^{1}(i\text{-}uni_{h}(C))...)))...)$$

where, denoted by f(C) the current result, we define:

$$\begin{array}{c} i\text{-}uni_0(C) = or\text{-}rewrite_\emptyset(C.\mathcal{E}\{ap_1 \hookrightarrow fp_1, \dots, ap_m \hookrightarrow fp_m\}) \left[\varphi_{C, \operatorname{async}}\right] \\ i\text{-}uni_j(C) = IAQ_j. \operatorname{Queue}(0) \left[\varphi_{C, \operatorname{async}}\right] & 1 \leq j \leq h \\ & \|\{IAQ_j. \operatorname{depart}\#C.i_j\} \left(i\text{-}uni_{j-1}(C)\right) \\ \hline i\text{-}and_1^j(f(C)) = IAQ_{j,1}. \operatorname{Queue}(0) \left[\varphi_{C, \operatorname{async}}\right] & 1 \leq j \leq h' \\ & \|\{IAQ_{j,1}. \operatorname{depart}\#...\#IAQ_{j,i_j}. \operatorname{depart}\#C.i_j'\} \left(f(C)\right) \\ \hline i\text{-}and_{j'}^j(f(C)) = IAQ_{j,j'}. \operatorname{Queue}(0) \left[\varphi_{C, \operatorname{async}}\right] & 2 \leq j' \leq il_j \\ & \|\{IAQ_{j,1}. \operatorname{depart}\#...\#IAQ_{j,i_j}. \operatorname{depart}\#C.i_j'\} \left(i\text{-}and_{j'-1}^j(f(C))\right) \\ \hline o\text{-}uni_0(f(C)) = f(C) \\ o\text{-}uni_j(f(C)) = \left(o\text{-}uni_{j-1}(f(C))\right) \|_{\{C.o_j\#OAQ_j.\operatorname{arrive}\}} \\ & OAQ_j. \operatorname{Queue}(0) \left[\varphi_{C, \operatorname{async}}\right] & 1 \leq j \leq k \\ \hline o\text{-}and_1^j(f(C)) = \left(f(C)\right) \|_{\{C.o_j'\#OAQ_{j,1}.\operatorname{arrive}\#...\#OAQ_{j,ol_j}.\operatorname{arrive}\}} \\ & OAQ_{j,1}. \operatorname{Queue}(0) \left[\varphi_{C, \operatorname{async}}\right] & 1 \leq j \leq k' \\ o\text{-}and_{j'}^j(f(C)) = \left(o\text{-}and_{j'-1}^j(f(C))\right) \|_{\{C.o_j'\#OAQ_{j,1}.\operatorname{arrive}\#...\#OAQ_{j,ol_j}.\operatorname{arrive}\}} \\ & OAQ_{j,j'}. \operatorname{Queue}(0) \left[\varphi_{C, \operatorname{async}}\right] & 2 \leq j' \leq ol_j \\ \hline \end{array}$$

with relabeling function  $\varphi_{C,async}$  transforming the originally asynchronous local interactions of C and the local interactions of the additional implicit AEIs attached to them into the respective fresh names occurring in the synchronization sets above.

**Example 3.3.** Consider the variant of the client-server system described in Ex. 3.1. With respect to Ex. 2.2, [S] changes as follows due to the presence of its two local output asynchronous uni-interactions:

```

\begin{split} & RewSer[S.send\_response\_1 \mapsto S.send\_response\_1\#0AQ\_1.arrive, \\ & S.send\_response\_2 \mapsto S.send\_response\_2\#0AQ\_2.arrive] \\ & \|_{\{S.send\_response\_1\#0AQ\_1.arrive\}} \\ & 0AQ\_1.Queue(0)[0AQ\_1.arrive \mapsto S.send\_response\_1\#0AQ\_1.arrive] \\ & \|_{\{S.send\_response\_2\#0AQ\_2.arrive\}} \end{split}

```

OAQ\_2.Queue(0)[OAQ\_2.arrive  $\mapsto$  S.send\_response\_2#OAQ\_2.arrive] As a consequence, with respect to Ex. 2.3, the semantics of the whole description changes as follows, where the roles of S.send\_response\_1 and S.send\_response\_2 are now played by AOQ\_1.depart and AOQ\_2.depart, respectively:

## 4. Modifying Architectural Checks

The objective of the architectural checks for PADL developed in [1] is to infer certain architectural properties like correct component coordination from the properties of the individual AEIs. The idea is to verify the absence of coordination mismatches resulting in property violations through a topological reduction process based on equivalence checking. Given an architectural description, the starting point is constituted by an abstract variant of its enriched flow graph, where vertices correspond to AEIs and two vertices are linked by an edge if and only if attachments have been declared among their interactions. From a topological viewpoint, the resulting graph is a combination of possibly intersecting stars (see Sect. 4.2) and cycles (see Sect. 4.3), which are thus viewed as basic topological formats.

The strategy then consists of applying specific checks locally to all stars and cycles occurring in the abstract graph. Each check verifies whether the star/cycle contains an AEI behaviorally equivalent to the whole star/cycle, in which case the star/cycle can be replaced by that AEI. The process successfully terminates when the whole graph has been reduced to a single behaviorally equivalent AEI, as at that point it is sufficient to verify whether that AEI satisfies the given property or not. In case of failure, the mentioned checks provide diagnostic information useful to pinpoint components responsible for possible property violations within a single star/cycle.

In order to be applicable, the strategy requires the existence of a behavioral equivalence that possesses the following characteristics. Firstly, the equivalence must preserve the property of interest – i.e., it cannot relate two models such that one of them enjoys the property whereas the other one does

not – which is fundamental for enabling the topological reduction process. Secondly, it must be a congruence with respect to static operators, thus allowing the topological reduction process to be applied to single portions of the topology of an architectural description – which is more efficient than considering the entire topology at once – without affecting the possible validity of the property. Thirdly, it must be able to abstract from internal actions, as an architectural property is typically expressed in terms of the possibility/necessity of executing local interactions in a certain order. Fourthly, it must have a modal logic characterization, which is necessary for producing diagnostic information in case of failure of the topological reduction process.

In this section, after introducing some further notation (Sect. 4.1), we show how to modify the compatibility check for stars (Sect. 4.2) and the interoperability check for cycles (Sect. 4.3) in such a way that both checks can still be applied in the presence of nonsynchronous interactions. Then, the two revised checks are exemplified on the architectural description of an applet-based simulator for a cruise control system (Sect. 4.4). Although these checks are conceived for an entire class of properties characterizable through behavioral equivalences that meet the four constraints mentioned above, for the sake of simplicity here the considered property is deadlock freedom and the behavioral equivalence chosen among those preserving deadlock freedom is weak bisimilarity  $\approx_{\rm B}$  introduced in Sect. 2.1.

#### 4.1. Revising Closed Interacting Semantics

Before applying the architectural checks to a star/cycle given by the set of AEIs  $\{C_1, \ldots, C_n\}$ , for each AEI  $C_j$  in the set we have to hide all of its internal actions and architectural interactions as well as all of its local interactions that are not attached to  $\{C_1, \ldots, C_n\}$ . The reason is that these actions cannot result in mismatches within the star/cycle, but may hamper the topological reduction process if left visible. Following the terminology of [1], we thus have to consider closed variants of the interacting semantics of the AEIs in the set, in which the mentioned actions are made unobservable.

In the framework of PADL enriched with nonsynchronous interactions, for each AEI  $C_j$  in the set we also have to hide all of its additional implicit AEIs that are not attached to  $\{C_1, \ldots, C_n\}$ , as those additional implicit AEIs are necessary only in the presence of the AEIs not in  $\{C_1, \ldots, C_n\}$  to which they are attached. Therefore, the only actions that remain observable are those in  $\mathcal{LI}_{C_i;C_1,\ldots,C_n}$  and those in  $\mathcal{OALI}_{C_i}$ . The latter set contains the

originally asynchronous local interactions of  $C_j$  together with the local interactions of the related additional implicit AEIs to which they have been re-attached, including the exceptions that may be raised by the local input semi-synchronous interactions in the set corresponding to local input asynchronous interactions. We point out that  $\mathcal{OALI}_{C_j}$  is disjoint from  $\mathcal{LI}_{C_j}$ , as it essentially comprises the action names forming the composite names occurring in the synchronization sets of the semantics of an AEI in isolation provided in Def. 3.2.

In order to set the visibility of each action of  $C_j$  according to the needs of the topological reduction process, we introduce a partially closed variant of the interacting semantics of an AEI defined at the end of Sect. 2.3, in which we hide all the actions not in  $\mathcal{LI}_{C_j;C_1,\ldots,C_n} \cup \mathcal{OALI}_{C_j}$ . Since in many cases we also have to hide all the actions in  $\mathcal{OALI}_{C_j}$ , we introduce a totally closed variant too. Thus, unlike [1], we have two closed variants of the interacting semantics of an AEI. Both variants are parameterized with respect to a set of AEIs  $\{C_1'',\ldots,C_{n''}''\}$ ,  $n'' \in \mathbb{N}$ , determining the additional implicit AEIs to be included.

**Definition 4.1.** Let  $\mathcal{C}$  be an AET,  $fp_1, \ldots, fp_m$  be its  $m \in \mathbb{N}_{\geq 0}$  formal parameters, and  $\mathcal{E}$  be a sequence of defining equations giving its behavior. Let  $C_j \in \{C_1, \ldots, C_n\}$  be an AEI of type  $\mathcal{C}$  with actual parameters  $ap_1, \ldots, ap_m$  consistent by order and type with the formal parameters. The interacting semantics of  $C_j$  with respect to  $\{C_1, \ldots, C_n\}$  without buffers for its originally asynchronous local interactions is defined as follows:

$$[\![C_j]\!]_{C_1,\ldots,C_n}^{\text{wob}} = or\text{-}rewrite_{\emptyset}(C_j.\mathcal{E}\{ap_1 \hookrightarrow fp_1,\ldots,ap_m \hookrightarrow fp_m\})$$

$$[\varphi_{C_j,\text{async}}] [\varphi_{C_j;C_1,\ldots,C_n}]$$

We denote by  $[\![C_j]\!]_{C_1,\dots,C_n}^{\#C_1'',\dots,C_{n''}''}$  the variant of  $[\![C_j]\!]_{C_1,\dots,C_n}^{\text{wob}}$  including the buffers for the originally asynchronous local interactions of  $C_j$  attached to  $\{C_1'',\dots,C_{n''}''\}$ .

**Definition 4.2.** Let  $C_j \in \{C_1, \ldots, C_n\}$ . The partially closed interacting semantics of  $C_j$  with respect to  $\{C_1, \ldots, C_n\}$  including its buffers attached to  $\{C''_1, \ldots, C''_{n''}\}$  is defined as follows:

$$[C_j]_{C_1,\dots,C_n}^{\mathrm{pc};\#C_1'',\dots,C_{n''}''} = [C_j]_{C_1,\dots,C_n}^{\#C_1'',\dots,C_{n''}'} / (Name - \mathcal{V}_{C_j;C_1,\dots,C_n})$$

with  $\mathcal{V}_{C_j;C_1,\dots,C_n} = \varphi_{C_j;C_1,\dots,C_n}(\mathcal{LI}_{C_j;C_1,\dots,C_n}) \cup \varphi_{C_j,async}(\mathcal{OALI}_{C_j})$  and we write  $[\![C_j]\!]_{C_1,\dots,C_n}^{pc;wob}$  if n''=0.

**Definition 4.3.** Let  $\{C'_1, \ldots, C'_{n'}\} \subseteq \{C_1, \ldots, C_n\}$ . The partially closed interacting semantics of  $\{C'_1, \ldots, C'_{n'}\}$  with respect to  $\{C_1, \ldots, C_n\}$  including their buffers attached to  $\{C''_1, \ldots, C''_{n''}\}$  is defined as follows:

where the synchronization sets are built as at the end of Sect. 2.3.

**Definition 4.4.** Let  $C_j \in \{C_1, \ldots, C_n\}$ . The totally closed interacting semantics of  $C_j$  with respect to  $\{C_1, \ldots, C_n\}$  including its buffers attached to  $\{C''_1, \ldots, C''_{n''}\}$  is defined as follows:

$$\boxed{ \begin{bmatrix} C_j \end{bmatrix}_{C_1,\dots,C_n}^{\operatorname{tc};\#C_1'',\dots,C_{n''}''} = \begin{bmatrix} C_j \end{bmatrix}_{C_1,\dots,C_n}^{\operatorname{pc};\#C_1'',\dots,C_{n''}'} / \varphi_{C_j,\operatorname{async}}(\mathcal{OALI}_{C_j}) }$$

and we write  $[\![C_j]\!]_{C_1,\dots,C_n}^{\text{tc;wob}}$  if n''=0.

**Definition 4.5.** Let  $\{C'_1, \ldots, C'_{n'}\} \subseteq \{C_1, \ldots, C_n\}$ . The totally closed interacting semantics of  $\{C'_1, \ldots, C'_{n'}\}$  with respect to  $\{C_1, \ldots, C_n\}$  including their buffers attached to  $\{C''_1, \ldots, C''_{n''}\}$  is defined as follows:

their buffers attached to

$$\{C_1'',\ldots,C_{n''}''\}$$

is defined as follows:

$$\begin{bmatrix} \mathbb{C}_1'',\ldots,C_{n'}' \end{bmatrix}_{C_1,\ldots,C_n}^{\mathrm{tc};\#C_1'',\ldots,C_{n''}''} = \\ \mathbb{C}_1'' \mathbb{I}_{C_1,\ldots,C_n}^{\mathrm{tc};\#C_1'',\ldots,C_{n''}''} \|_{\mathcal{S}(C_1',C_2';C_1,\ldots,C_n)} \\ \mathbb{C}_2' \mathbb{I}_{C_1,\ldots,C_n}^{\mathrm{tc};\#C_1'',\ldots,C_{n''}''} \|_{\mathcal{S}(C_1',C_2';C_1,\ldots,C_n)} \cup \mathcal{S}(C_2',C_3';C_1,\ldots,C_n) \cdots \\ \dots \|_{n'-1} & \cup \\ & \cup$$

where the synchronization sets are built as at the end of Sect. 2.3. The variant totally closed up to  $\{C_1''',\ldots,C_{n'''}''\}\subset\{C_1',\ldots,C_{n'}'\}$ , i.e., in which  $[\![C_j''']\!]_{C_1,\ldots,C_n}^{\mathrm{pc};\#C_1'',\ldots,C_{n''}'}$  is considered in place of  $[\![C_j''']\!]_{C_1,\ldots,C_n}^{\mathrm{tc};\#C_1'',\ldots,C_{n''}'}$ , is denoted by  $[\![C_1',\ldots,C_{n'}]\!]_{C_1,\ldots,C_n}^{\mathrm{tc};\#C_1'',\ldots,C_{n''}'}$ .

## 4.2. Adapting Architectural Compatibility for Stars

A star is a portion of the abstract enriched flow graph of an architectural description, which is not part of a cyclic subgraph. It is formed by a central AEI K and a border  $\mathcal{B}_K = \{C_1, \ldots, C_n\}$  including all the AEIs attached to K. As explained in [1], the validity of an architectural property over a star can be investigated by analyzing the interplay between the central AEI K and each of the AEIs in the border, as there cannot be attachments among AEIs in the border. In order to achieve a correct coordination between Kand  $C_j \in \mathcal{B}_K$ , the actual observable behavior of  $C_j$  should coincide with the observable behavior expected by K. In other words, the observable behavior of K should not be altered by the insertion of  $C_i$  into the border of the star.

In order to cope with the presence of nonsynchronous interactions, we modify the architectural compatibility check for stars as follows.

**Definition 4.6.** Given an architectural description  $\mathcal{A}$ , let K be the central AEI of a star of  $\mathcal{A}$ ,  $\mathcal{B}_K = \{C_1, \ldots, C_n\}$  be the border of the star,  $C_j$  be an AEI in  $\mathcal{B}_K$ ,  $H_{K,C_i}$  be the set of interactions of additional implicit AEIs of K that are attached to interactions of  $C_j$ , and  $E_{K,C_j}$  be the set of exceptions that may be raised by semi-synchronous interactions involved in attachments between K and  $C_j$ . We say that K is compatible with  $C_j$  iff:  $(\llbracket K \rrbracket_{\mathcal{A}}^{\mathrm{pc};\#C_j} \parallel_{\mathcal{S}(K,C_j;\mathcal{A})} \llbracket C_j \rrbracket_{K,\mathcal{B}_K}^{\mathrm{tc};\#K}) / (H_{K,C_j} \cup E_{K,C_j}) \approx_{\mathrm{B}} \llbracket K \rrbracket_{\mathcal{A}}^{\mathrm{pc};\mathrm{wob}}$

$$(\llbracket K \rrbracket_{\mathcal{A}}^{\mathrm{pc};\#C_j} \parallel_{\mathcal{S}(K,C_j;\mathcal{A})} \llbracket C_j \rrbracket_{K,\mathcal{B}_K}^{\mathrm{tc};\#K}) / (H_{K,C_j} \cup E_{K,C_j}) \approx_{\mathrm{B}} \llbracket K \rrbracket_{\mathcal{A}}^{\mathrm{pc};\mathrm{wob}}$$

All possible originally asynchronous local interactions of  $C_j$  and all of its interactions possibly attached to AEIs outside the star have been hidden by taking the totally closed interacting semantics of  $C_i$  with respect to the AEIs inside the star. We also observe that  $H_{K,C_i} \cup E_{K,C_i} = \emptyset$  whenever there are no local nonsynchronous interactions involved in attachments inside the star, in which case all partially closed interacting semantics between  $[\![K]\!]_{\mathcal{A}}^{\mathrm{pc};\#\mathcal{A}}$  and  $[\![K]\!]_{\mathcal{A}}^{\mathrm{pc;wob}}$  coincide with  $[\![K]\!]_{\mathcal{A}}^{\mathrm{tc;wob}}$ .

We now extend the compatibility theorem of [1] to nonsynchronous interactions. This provides a sufficient condition for reducing the deadlock verification of the entire star to the deadlock verification of its central AEI.

**Theorem 4.7.** Let  $\mathcal{A}$ , K,  $\mathcal{B}_K$ ,  $C_j$ ,  $H_{K,C_j}$ , and  $E_{K,C_j}$  be the same as Def. 4.6. Whenever K is compatible with every  $C_j \in \mathcal{B}_K$ , then:

$$[\![K,\mathcal{B}_K]\!]_{K,\mathcal{B}_K}^{\mathrm{tc};\#K,\mathcal{B}_K;K} / \bigcup_{j=1}^n (H_{K,C_j} \cup E_{K,C_j}) \approx_{\mathrm{B}} [\![K]\!]_{\mathcal{A}}^{\mathrm{pc};\mathrm{wob}}$$

hence  $\llbracket K, \mathcal{B}_K \rrbracket_{K,\mathcal{B}_K}^{\mathrm{tc};\#K,\mathcal{B}_K;K} / \bigcup_{j=1}^n (H_{K,C_j} \cup E_{K,C_j})$  is deadlock free iff so is  $\llbracket K \rrbracket_{\mathcal{A}}^{\mathrm{pc};\mathrm{wob}}$ .

**Proof** Since there cannot be attachments between interactions of the AEIs of  $\mathcal{B}_K$ , it turns out that  $\llbracket K, \mathcal{B}_K \rrbracket_{K,\mathcal{B}_K}^{\mathrm{tc};\#K,\mathcal{B}_K;K} / \bigcup_{j=1}^n (H_{K,C_j} \cup E_{K,C_j})$  is given by:

$$(\llbracket K \rrbracket_{\mathcal{A}}^{\mathrm{pc};\#\mathcal{B}_K} \parallel_{\mathcal{S}(K,C_1;\mathcal{A})} \llbracket C_1 \rrbracket_{K,\mathcal{B}_K}^{\mathrm{tc};\#K} \parallel_{\mathcal{S}(K,C_2;\mathcal{A})} \llbracket C_2 \rrbracket_{K,\mathcal{B}_K}^{\mathrm{tc};\#K}$$

$$\|_{\mathcal{S}(K,C_3;\mathcal{A})} \dots \|_{\mathcal{S}(K,C_n;\mathcal{A})} [\![C_n]\!]_{K,\mathcal{B}_K}^{\mathrm{tc};\#K}) / \bigcup_{j=1}^n (H_{K,C_j} \cup E_{K,C_j})$$

Since each local asynchronous and-interaction is dealt with by introducing as many additional implicit AEIs as there are attachments involving the and-interaction,  $H_{K,C_j} \cap H_{K,C_g} = \emptyset$  for all  $j \neq g$ . Hence, every hiding set  $H_{K,C_j}$  can be distributed in such a way that it is applied as soon as possible. Similarly, every hiding set  $E_{K,C_j}$  can be anticipated too, because  $E_{K,C_j}$  is independent from  $E_{K,C_g}$  for all  $j \neq g$  due to the fact that any exception is raised locally at a single AEI. As a consequence,  $[K, \mathcal{B}_K]_{K,\mathcal{B}_K}^{\text{tc};\#K,\mathcal{B}_K;K} / \bigcup_{j=1}^n (H_{K,C_j} \cup E_{K,C_j})$  can be rewritten in the following way:

Denoted by  $IAQ_{K,C_j}$  (resp.  $OAQ_{K,C_j}$ ) the parallel composition of the behaviors of the input (resp. output) asynchronous queues of K attached to  $C_j$  – whose local interactions are relabeled according to  $\varphi_{K,\text{async}}$  and  $\varphi_{K;\mathcal{A}}$  – and by  $\mathcal{OALI}_{K,C_j}^{\text{input}}$  (resp.  $\mathcal{OALI}_{K,C_j}^{\text{output}}$ ) their local interactions attached to K, it turns out that  $[\![K]\!]_{\mathcal{A}}^{\text{pc};\#\mathcal{B}_K}$  is given by:

$$\begin{split} IAQ_{K,C_n} \parallel_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_n}^{\mathrm{input}})} \\ (\cdots \\ (IAQ_{K,C_2} \parallel_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_2}^{\mathrm{input}})} \\ (IAQ_{K,C_1} \parallel_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_1}^{\mathrm{input}})} \\ \|_{K} \|_{\mathcal{A}}^{\mathrm{pc;wob}} \\ \|_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_1}^{\mathrm{output}})} \underbrace{OAQ_{K,C_1}} \\ \|_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_2}^{\mathrm{output}})} \underbrace{OAQ_{K,C_2}} \\ \cdots) \\ \|_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_n}^{\mathrm{output}})} \underbrace{OAQ_{K,C_n}} \end{split}$$

Since from the point of view of  $C_j$  and  $C_g$  the asynchronous queues of K attached to  $C_j$  are independent from the asynchronous queues of K attached to  $C_g$  for all  $j \neq g$ , we have that  $[\![K, \mathcal{B}_K]\!]_{K,\mathcal{B}_K}^{\mathrm{tc};\#K,\mathcal{B}_K;K} / \bigcup_{j=1}^n (H_{K,C_j} \cup E_{K,C_j})$  can

```

be rewritten in the following way:

```

```

(IAQ_{K,C_n} \parallel_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_n}^{\mathrm{input}})}

(\mathit{IAQ}_{K,C_2} \parallel_{\varphi_{K,\operatorname{async}}(\mathcal{OALI}_{K,C_2}^{\operatorname{input}})}

(IAQ_{K,C_1} \parallel_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_1}^{\mathrm{input}})} \\ \llbracket K \rrbracket_{A}^{\mathrm{pc};\mathrm{wob}}

\parallel_{\varphi_{K, \operatorname{async}}(\mathcal{OALI}_{K, C_{1}}^{\operatorname{output}})} OAQ_{K, C_{1}} \parallel_{\mathcal{S}(K, C_{1}; \mathcal{A})} \llbracket C_{1} \rrbracket_{K, \mathcal{B}_{K}}^{\operatorname{tc}; \#K}) / (H_{K, C_{1}} \cup E_{K, C_{1}})

\parallel_{\varphi_{K, \operatorname{async}}(\mathcal{OALI}_{K, C_{2}}^{\operatorname{output}})} OAQ_{K, C_{2}} \parallel_{\mathcal{S}(K, C_{2}; \mathcal{A})} \llbracket C_{2} \rrbracket_{K, \mathcal{B}_{K}}^{\operatorname{tc}; \#K}) / (H_{K, C_{2}} \cup E_{K, C_{2}})

\cdots)

```

$\|_{\varphi_{K,\operatorname{async}}(\mathcal{OALI}_{K,C_{n}}^{\operatorname{output}})} OAQ_{K,C_{n}} \|_{\mathcal{S}(K,C_{n};\mathcal{A})} [\![C_{n}]\!]_{K,\mathcal{B}_{K}}^{\operatorname{tc};\#K}) / (H_{K,C_{n}} \cup E_{K,C_{n}})$ Since  $IAQ_{K,C_{1}} \|_{\varphi_{K,\operatorname{async}}(\mathcal{OALI}_{K,C_{1}}^{\operatorname{input}})} [\![K]\!]_{\mathcal{A}}^{\operatorname{pc};\operatorname{wob}} \|_{\varphi_{K,\operatorname{async}}(\mathcal{OALI}_{K,C_{1}}^{\operatorname{output}})} OAQ_{K,C_{1}} \text{ is}$ precisely  $[\![K]\!]_{\mathcal{A}}^{\operatorname{pc};\#C_{1}}$  and  $([\![K]\!]_{\mathcal{A}}^{\operatorname{pc};\#C_{1}} \|_{\mathcal{S}(K,C_{1};\mathcal{A})} [\![C_{1}]\!]_{K,\mathcal{B}_{K}}^{\operatorname{tc};\#K}) / (H_{K,C_{1}} \cup E_{K,C_{1}}) \approx_{\mathbf{B}} C_{1} (\mathbb{C}_{K,\mathcal{C}_{1}}) \otimes_{\mathbf{B}} C_{1} (\mathbb{C}_{1}) \otimes_{\mathbf{B}} C_{1} (\mathbb{C}_{1}) \otimes_{\mathbf{B}} C_{1} (\mathbb{C}_{1}) \otimes$  $[\![K]\!]_{\mathcal{A}}^{\mathrm{pc;wob}}$  due to the compatibility of K with  $C_1$ , by virtue of the congruence property of  $\approx_{\rm B}$  with respect to static operators – and also with respect to the context-sensitive variant of the relabeling operator governing exceptions as it encodes an injective relabeling function over actions in dot notation, which thus preserves action qualifiers - it turns out that  $[\![K,\mathcal{B}_K]\!]_{K,\mathcal{B}_K}^{\mathrm{tc};\#K,\mathcal{B}_K;K} / \bigcup_{i=1}^n (H_{K,C_i} \cup E_{K,C_i})$  is weakly bisimilar to:

```

(IAQ_{K,C_n} \parallel_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_n}^{\mathrm{input}})})

(\cdots

\begin{array}{c} (\mathit{IAQ}_{K,C_2} \parallel_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_2}^{\mathrm{input}})} \\ [\![K]\!]_{A}^{\mathrm{pc};\mathrm{wob}} \end{array}

\|_{\varphi_{K,\operatorname{async}}(\mathcal{OALI}_{K,C_2}^{\operatorname{output}})} \operatorname{OAQ}_{K,C_2} \|_{\mathcal{S}(K,C_2;\mathcal{A})} [\![C_2]\!]_{K,\mathcal{B}_K}^{\operatorname{tc};\#K}) / (H_{K,C_2} \cup E_{K,C_2})

...)

\parallel_{\varphi_{K,\mathrm{async}}(\mathcal{OALI}_{K,C_n}^{\mathrm{output}})} OAQ_{K,C_n} \parallel_{\mathcal{S}(K,C_n;\mathcal{A})} \llbracket C_n \rrbracket_{K,\mathcal{B}_K}^{\mathrm{tc};\#K}) \, / \, \big( H_{K,C_n} \cup E_{K,C_n} \big)

```

By reasoning in the same way for each of the other AEIs  $C_2, \ldots, C_n$  of  $\mathcal{B}_K$ , we end up with  $[\![K,\mathcal{B}_K]\!]_{K,\mathcal{B}_K}^{\mathrm{tc};\#K,\mathcal{B}_K;K} / \bigcup_{j=1}^n (H_{K,C_j} \cup E_{K,C_j}) \approx_{\mathrm{B}} [\![K]\!]_{\mathcal{A}}^{\mathrm{pc};\mathrm{wob}}$ . The second part of the result then follows from the fact that  $\approx_B$  preserves deadlock freedom.

(An induction on the size of  $\mathcal{B}_K$  is hampered by the variability of the set of AEIs with respect to which the interacting semantics are defined.)

## 4.3. Adapting Architectural Interoperability for Cycles

A cycle is a closed simple path in the abstract enriched flow graph of an architectural description, which traverses a set  $\mathcal{Y} = \{C_1, \dots, C_n\}$  of  $n \geq 3$  AEIs. As explained in [1], the validity of an architectural property over a cycle cannot be investigated by analyzing the interplay between pairs of AEIs, because of the possible presence of arbitrary interferences among the various AEIs in the cycle. In order to achieve a correct coordination between any  $C_j$  and the rest of the cycle, the actual observable behavior of  $C_j$  should coincide with the observable behavior expected by the rest of the cycle. In other words, the observable behavior of  $C_j$  should not be altered by the insertion of  $C_j$  itself into the cycle.

In order to cope with the presence of nonsynchronous interactions, we modify the architectural interoperability check for cycles as follows.

**Definition 4.8.** Given an architectural description  $\mathcal{A}$ , let  $\mathcal{Y} = \{C_1, \ldots, C_n\}$  be the set of AEIs traversed by a cycle of  $\mathcal{A}$ ,  $C_j$  be an AEI in the cycle,  $H_{C_j,\mathcal{Y}}$  be the set of interactions of additional implicit AEIs of  $C_j$  that are attached to  $\mathcal{Y}$ , and  $E_{C_j,\mathcal{Y}}$  be the set of exceptions that may be raised by semi-synchronous interactions involved in attachments between  $C_j$  and  $\mathcal{Y}$ . We say that  $C_j$  interoperates with the other AEIs in the cycle iff:

$$[\![\mathcal{Y}]\!]_{\mathcal{A}}^{\mathrm{tc};\#\mathcal{Y};C_j} / (Name - \mathcal{V}_{C_j;\mathcal{A}}) / (H_{C_j,\mathcal{Y}} \cup E_{C_j,\mathcal{Y}}) \approx_{\mathrm{B}} [\![C_j]\!]_{\mathcal{A}}^{\mathrm{pc};\mathrm{wob}}$$

All possible originally asynchronous local interactions of the other AEIs in the cycle and all of their interactions that are not attached to  $C_j$  have been hidden by taking the totally closed interacting semantics of those AEIs and by leaving visible only the actions in  $\mathcal{V}_{C_j;\mathcal{A}}$ . We also observe that, whenever  $C_j$  has no local nonsynchronous interactions and is not attached to semi-synchronous interactions of other AEIs in the cycle, then  $H_{C_j,\mathcal{Y}} \cup E_{C_j,\mathcal{Y}} = \emptyset$  and both  $[C_j]_{\mathcal{A}}^{\mathrm{pc};\#\mathcal{Y}}$  and  $[C_j]_{\mathcal{A}}^{\mathrm{pc};\mathrm{wob}}$  coincide with  $[C_j]_{\mathcal{A}}^{\mathrm{tc};\mathrm{wob}}$ .

We now extend the interoperability theorem of [1] to nonsynchronous interactions. This provides a sufficient condition for reducing the deadlock verification of the entire cycle to the deadlock verification of one of its AEIs.

**Theorem 4.9.** Let  $\mathcal{A}$ ,  $\mathcal{Y}$ ,  $C_j$ ,  $H_{C_j,\mathcal{Y}}$ , and  $E_{C_j,\mathcal{Y}}$  be the same as Def. 4.8. Whenever  $C_j$  interoperates with the other AEIs in the cycle, then  $[\![\mathcal{Y}]\!]_{\mathcal{A}}^{\mathrm{tc};\#\mathcal{Y};C_j}$  /  $(Name - \mathcal{V}_{C_j,\mathcal{A}})$  /  $(H_{C_j,\mathcal{Y}} \cup E_{C_j,\mathcal{Y}})$  is deadlock free iff so is  $[\![C_j]\!]_{\mathcal{A}}^{\mathrm{pc};\mathrm{wob}}$ .

**Proof** A straightforward consequence of Def. 4.8 and of the fact that  $\approx_B$  preserves deadlock freedom.

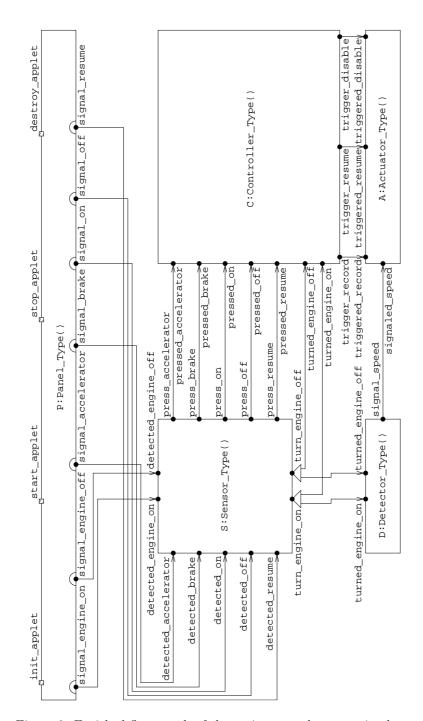

4.4. Case Study: An Applet-Based Simulator for a Cruise Control System In this section, we discuss the application of the modified architectural checks by revisiting the cruise control system considered in [32, 11].

Once the engine has been turned on, this system is governed by the two standard pedals of the automobile – accelerator and brake – and by three additional buttons – on, off, and resume. When on is pressed, the cruise control system records the current speed and maintains the automobile at that speed. When the accelerator, the brake, or off is pressed, the cruise control system disengages but retains the speed setting. If resume is pressed later on, then the system is able to accelerate or decelerate the automobile to the previously recorded speed.

The cruise control system is formed by four software components: a sensor, a speed controller, a speed detector, and a speed actuator. The sensor detects the driver commands and forwards them to the speed controller, which in turn triggers the speed actuator. The speed detector periodically measures the number of wheel revolutions per time unit. The speed actuator adjusts the throttle on the basis of the triggers received from the controller and of the speed measured by the detector.

Let us describe the cruise control system with PADL. The sensor AET is defined as follows:

```

ARCHI_ELEM_TYPE Sensor_Type(void)

BEHAVIOR

Sensor_Off(void; void) =

detected_engine_on . turn_engine_on . Sensor_On();

Sensor_On(void; void) =

choice

detected_accelerator . press_accelerator . Sensor_On(),

detected_brake . press_brake . Sensor_On(),

detected_on . press_on . Sensor_On(),

detected_off . press_off . Sensor_On(),

detected_resume . press_resume . Sensor_On(),

detected_engine_off . turn_engine_off . Sensor_Off()

INPUT_INTERACTIONS SYNC UNI detected_engine_on; detected_engine_off;

detected_accelerator; detected_brake;

detected_on; detected_off; detected_resume

OUTPUT_INTERACTIONS SYNC UNI press_accelerator; press_brake;

press_on; press_off; press_resume

AND turn_engine_on; turn_engine_off

```

The speed controller triggers the speed actuator on the basis of the commands forwarded by the sensor. It can be inactive (when the engine is off), active (when the engine is on), cruising (after pressing the on button in the active state or the resume button in the suspended state), or suspended (after pressing any pedal or button different from on/resume in the cruising state):

```

ARCHI_ELEM_TYPE Controller_Type(void)

BEHAVIOR

Inactive(void; void) =

turned_engine_on . Active();

Active(void; void) =

choice

pressed_accelerator . Active(),

pressed_brake . Active(),

pressed_on . trigger_record . Cruising(),

pressed_off . Active(),

pressed_resume . Active(),

turned_engine_off . Inactive()

Cruising(void; void) =

choice

{

pressed_accelerator . trigger_disable . Suspended(),

pressed_brake . trigger_disable . Suspended(),

pressed_on . Cruising(),

pressed_off . trigger_disable . Suspended(),

pressed_resume . Cruising(),

turned_engine_off . trigger_disable . Inactive()

};

Suspended(void; void) =

choice

{

pressed_accelerator . Suspended(),

pressed_brake . Suspended(),

pressed_on . trigger_record . Cruising(),

pressed_off . Suspended(),

pressed_resume . trigger_resume . Cruising(),

turned_engine_off . Inactive()

INPUT_INTERACTIONS SYNC UNI turned_engine_on; turned_engine_off;

pressed_accelerator; pressed_brake;

pressed_on; pressed_off; pressed_resume

OUTPUT_INTERACTIONS SYNC UNI trigger_record; trigger_resume;

trigger_disable

```

The speed detector periodically communicates the number of wheel revolutions per time unit to the speed actuator:

```

ARCHI_ELEM_TYPE Detector_Type(void)

BEHAVIOR

Detector_Off(void; void) =

turned_engine_on . Detector_On();

Detector_On(void; void) =

choice

{

measure_speed . signal_speed . Detector_On(),

turned_engine_off . Detector_Off()

}

INPUT_INTERACTIONS SYNC UNI turned_engine_on; turned_engine_off

OUTPUT_INTERACTIONS SYNC UNI signal_speed

```

The speed actuator adjusts the throttle on the basis of the triggers received from the controller and of the speed measured by the detector. It can be disabled (until the on/resume button is pressed) or enabled (until any pedal or button different from on/resume is pressed):

Suppose we want to design an applet-based simulator for the cruise control system. The applet must contain a panel with seven software buttons – corresponding to turning the engine on/off, the two pedals, and the three hardware buttons – and a text area showing the sequence of buttons that

have been pressed. When pressing one of the seven software buttons, the corresponding operation either succeeds or fails. In the first case, the panel can interact with the sensor and the text area is updated accordingly. In the second case – think, e.g., of pressing the accelerator button when the engine is off – the panel cannot interact with the sensor, rather it emits a beep.

In order not to block the simulator when the pressure of a software button fails, we need to model several operations of the panel through semisynchronous interactions, as shown below:

```

ARCHI_ELEM_TYPE Panel_Type(void)

BEHAVIOR

Unallocated(void; void) =

init_applet . start_applet . Active();

Active(void; void) =

choice

signal_engine_on . Checking(signal_engine_on.success),

signal_accelerator . Checking(signal_accelerator.success),

signal_brake . Checking(signal_brake.success),

signal_on . Checking(signal_on.success),

signal_off . Checking(signal_off.success),

signal_resume . Checking(signal_resume.success),

signal_engine_off . Checking(signal_engine_off.success),

stop_applet . Inactive()

Checking(boolean success; void) =

choice

{

cond(success = true) -> update . Active(),

cond(success = false) -> beep . Active(),

};

Inactive(void; void) =

choice

start_applet . Active(),

destroy_applet . Unallocated()

INPUT_INTERACTIONS SYNC UNI init_applet; start_applet;