# Fault-tolerant Algorithms for Tick-Generation in Asynchronous Logic: Robust Pulse Generation

Danny Dolev, Matthias Függer, Christoph Lenzen, and Ulrich Schmid

## Abstract

Today's hardware technology presents a new challenge in designing robust systems. Deep submicron VLSI technology introduced transient and permanent faults that were never considered in low-level system designs in the past. Still, robustness of that part of the system is crucial and needs to be guaranteed for any successful product. Distributed systems, on the other hand, have been dealing with similar issues for decades. However, neither the basic abstractions nor the complexity of contemporary fault-tolerant distributed algorithms match the peculiarities of hardware implementations.

This paper is intended to be part of an attempt striving to overcome this gap between theory and practice for the clock synchronization problem. Solving this task sufficiently well will allow to build a very robust high-precision clocking system for hardware designs like systems-on-chips in critical applications. As our first building block, we describe and prove correct a novel Byzantine fault-tolerant self-stabilizing pulse synchronization protocol, which can be implemented using standard asynchronous digital logic. Despite the strict limitations introduced by hardware designs, it offers optimal resilience and smaller complexity than all existing protocols.

# 1 Introduction & Related Work

With today's deep submicron technology running at GHz clock speeds [20], disseminating the highspeed clock throughout a very large scale integrated (VLSI) circuit, with negligible skew, is difficult and costly [2, 3, 12, 24, 29]. Systems-on-chip are hence increasingly designed globally asynchronous locally synchronous (GALS) [4], where different parts of the chip use different local clock signals. Two main types of clocking schemes for GALS systems exist, namely, (i) those where the local clock signals are unrelated, and (ii) multi-synchronous ones that provide a certain degree of synchrony between local clock signals [30, 34].

GALS systems clocked by type (i) permanently bear the risk of *metastable upsets* when conveying information from one clock domain to another. To explain the issue, consider a physical implementation of a bistable storage element, like a register cell, which can be accessed by read and write operations concurrently. It can be shown that two operations (like two writes with different values) occurring very closely to each other can cause the storage cell to attain neither of its two stable states for an unbounded time [23], and thereby, during an unbounded time afterwards, successive reads may return none of the stable states. Although the probability of a single upset is very small, one has to take into account that every bit of transmitted information across clock domains is a candidate for an upset. Elaborate synchronizers [8, 21, 28] are the only means for achieving an acceptably low probability for metastable upsets here.

This problem can be circumvented in clocking schemes of type (ii): Common synchrony properties offered by multi-synchronous clocking systems are:

- bounded skew, i.e., bounded maximum time between the occurence of any two matching clock transitions of any two local clock signals. Thereby, in classic clock synchronization, two clock transitions are matching iff they are both the  $k^{\text{th}}$ ,  $k \ge 1$ , clock transition of a local clock.

- *bounded accuracy*, i.e., bounded minimum and maximum time between the occurence of any two successive clock transitions of any local clock signal.

Type (ii) clocking schemes are particularly beneficial from a designer's point of view, since they combine the convenient local synchrony of a GALS system with a global time base across the whole chip. It has been shown in [27] that these properties indeed facilitate metastability-free high-speed communication across clock domains.

The decreasing structure sizes of deep submicron technology also resulted in an increased likelihood of chip components failing during operation: Reduced voltage swing and smaller critical charges make circuits more susceptible to ionized particle hits, crosstalk, and electromagnetic interference [5, 18]. *Fault-tolerance* hence becomes an increasingly pressing issue in chip design. Unfortunately, faulty components may behave non-benign in many ways. They may perform signal transitions at arbitrary times and even convey inconsistent information to their successor components if their outgoing communication channels are affected by a failure. This forces to model faulty components as unrestricted, i.e., Byzantine, if a high fault coverage is to be guaranteed.

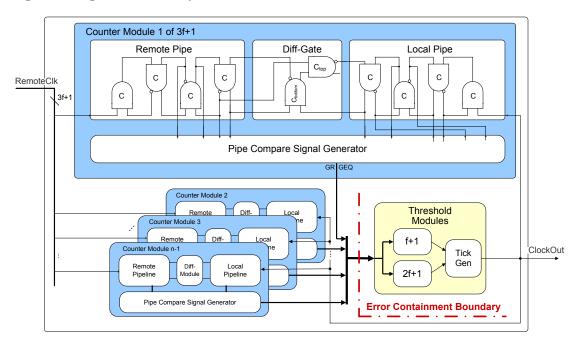

The DARTS fault-tolerant clock generation approach [15, 17] developed by some of the authors of this paper is a Byzantine fault-tolerant multi-synchronous clocking scheme. DARTS comprises a set of modules, each of which generates a local clock signal for a single clock domain. The DARTS modules (nodes) are synchronized to each other to within a few clock cycles. This is achieved by exchanging binary clock signals only, via single wires. The basic idea behind DARTS is to employ a simple fault-tolerant distributed algorithm [35]—based on Srikanth & Toueg's consistent broadcasting primitive [31]—implemented in asynchronous digital logic. An important property of the DARTS clocking scheme is that it guarantees that no metastable upsets occur during fault-free executions. For executions with faults, metastable upsets cannot be ruled out: Since Byzantine faulty components are allowed to issue unrelated read and write accesses by definition, the same arguments as for clocking schemes of type (i) apply. However, in [13], it was shown that by proper chip design the probability of a Byzantine component leading to a metastable upset of DARTS can be made arbitrarily small.

Although both theoretical analysis and experimental evaluation revealed many attractive additional features of DARTS, like guaranteed startup, automatic adaption to current operating conditions, etc., there is room for improvement. The most obvious drawback of DARTS is its inability to support late joining and restarting of nodes, and, more generally, its lack of self-stabilization properties. If, for some reasons, more than a third of the DARTS nodes ever become faulty, the system cannot be guaranteed to resume normal operation even if all failures cease. Even worse, simple transient faults such as radiation- or crosstalk-induced additional (or omitted) clock ticks accumulate over time to arbitrarily large skews in an otherwise benign execution.

Byzantine-tolerant self-stabilization, on the other hand, is the major strength of a number of protocols [1, 6, 9, 19, 22] primarily devised for distributed systems. Of particular interest in the above context is the work on self-stabilizing *pulse synchronization*, where the purpose is to generate well-separated anonymous pulses that are synchronized at all correct nodes. This facilitates selfstabilizing clock synchronization, as agreement on a time window permits to simulate a synchronous protocol in a bounded-delay system. Beyond optimal (i.e.,  $\lceil n/3 \rceil - 1$ , c.f. [26]) resilience, an attractive feature of these protocols is a small stabilization time [1, 6, 19, 22], which is crucial for applications with stringent availability requirements. In particular, [1] synchronizes clocks in expected constant time in a synchronous system. Given any pulse synchronization protocol stabilizing in a bounded-delay system in expected time T, this implies an expected (T + O(1))stabilizing clock synchronization protocol.

Nonetheless, it remains open whether a (with respect to the number of nodes n) sublinear convergence time can be achieved: While the classical consensus lower bound of f + 1 rounds for synchronous, deterministic algorithms in a system with f < n/3 faults [11] proves that *exact* agreement on a clock value requires at least  $f + 1 \in \Omega(n)$  deterministic rounds, one has to face the fact that only approximate agreement on the current time is achievable in a bounded-delay system anyway. However, no non-trivial lower bounds on approximate deterministic synchronization or the exact problem with randomization are known by now.

Note that existing synchronization algorithms, in particular those that do not rely on pulse synchronization, have deficiencies rendering them unsuitable in our context. For example, they have exponential convergence time [9], require the relative drift of the nodes' local clocks to be very small [7, 22],<sup>1</sup> provide larger skew only [22] or make use of linear-sized messages [6]. Furthermore, standard models used by the distributed systems community do not account for metastability, resulting in the same to be true for the existing solutions.

It is hence natural to explore ways of combining and extending the above lines of research. The present paper is the first step towards this goal.

Detailed contributions. We describe and prove correct the novel FATAL pulse synchroniza-

<sup>&</sup>lt;sup>1</sup>Note that it is too costly and space consuming to equip each node with a quartz oscillator. Simple digital oscillators, like inverters with feedback, in turn exhibit drifts of at least several percent, which heavily vary with operating conditions.

tion protocol, which facilitates a direct implementation in standard asynchronous digital logic. It self-stabilizes within  $\mathcal{O}(n)$  time with probability  $1-2^{n-f}$ , in the presence of up to  $\lfloor n/3 \rfloor - 1$ Byzantine faulty nodes, and is metastability-free by construction after stabilization in failure-free runs. While executing the protocol, non-faulty nodes broadcast a constant number of bits in constant time. In terms of distributed message complexity, this implies that stabilization is achieved after broadcasting  $\mathcal{O}(n)$  messages of size  $\mathcal{O}(1)$ , improving by factor  $\Omega(n)$  on the number of bits transmitted by previous algorithms.<sup>3</sup> The protocol can sustain large relative clock drifts of more than 10%, which is crucial if the local clock sources are simple ring oscillators (uncompensated ring oscillators suffer from clock drifts of up to 9% [32]). If the number of faults is not overwhelming, i.e., a majority of at least n - f nodes continues to execute the protocol in an orderly fashion, recovering nodes and late joiners (re)synchronize in constant time. This property is highly desirable in practical systems, in particular in combination with Byzantine fault-tolerance: Even if nodes randomly experience transient faults on a regular basis, quick recovery ensures that the mean time until failure of the system as a whole is substantially increased. All this is achieved against a powerful adversary that, at time t, knows the whole history of the system up to time  $t + \varepsilon$  (where  $\varepsilon > 0$  is infinitesimally small) and does not need to choose the set of faulty nodes in advance. Apart from bounded drifts and communication delays, our solution solely requires that receivers can unambiguously identify the sender of a message, which is a property that arises naturally in hardware designs.

We also describe how the pulse synchronization protocol can be implemented using asynchronous digital logic. Moreover, we sketch how the pulse synchronization protocol will be integrated with DARTS clocks to build a high-precision self-stabilizing clocking system for multi-synchronous GALS. The basic idea of our integration is to let the pulse synchronization protocol non-intrusively monitor the operation of DARTS clocks and to recover DARTS clocks that run abnormally. Like the original DARTS, the joint system is metastability-free in failure-free runs after stabilization. During stabilization, the fact that nodes merely undergo a constant number of state transitions in constant time ensures a very small probability of metastable upsets.

## 2 Model

Our formal framework will be tied to the peculiarities of hardware designs, which consist of modules that *continuously*<sup>4</sup> compute their output signals based on their input signals. Following [14, 16], we define (the trace of) a *signal* to be a timed event trace over a finite alphabet S of possible signal states: Formally, signal  $\sigma \subseteq S \times \mathbb{R}_0^+$ . All times and time intervals refer to a global *reference time* taken from  $\mathbb{R}_0^+$ , that is, signals describe the system's behaviour from time 0 on. The elements of  $\sigma$ are called *events*, and for each event (s, t) we call s the state of event (s, t) and t the time of event (s, t). In general, a signal  $\sigma$  is required to fulfill the following conditions: (i) for each time interval  $[t^-, t^+] \subseteq \mathbb{R}_0^+$  of finite length, the number of events in  $\sigma$  with times within  $[t^-, t^+]$  is finite, (ii) from  $(s, t) \in \sigma$  and  $(s', t) \in \sigma$  follows that s = s', and (iii) there exists an event at time 0 in  $\sigma$ .

<sup>&</sup>lt;sup>2</sup>Note that the algorithm from [1] achieving an expected constant stabilization time in a synchronous model needs to run for  $\Omega(n)$  rounds to ensure the same probability of stabilization.

$<sup>^{3}</sup>$ We remark that [22] achieves the same complexity, but considers a much simpler model. In particular, *all* communication is restricted to broadcasts, i.e., all nodes observe the same behaviour of a given other node, even if it is faulty.

<sup>&</sup>lt;sup>4</sup>In sharp contrast to classic distributed computing models, there is no computationally complex discrete zero-time state-transition here.

Note that our definition allows for events (s, t) and  $(s, t') \in \sigma$ , where t < t', without having an event  $(s', t'') \in \sigma$  with  $s' \neq s$  and t < t'' < t'. In this case, we call event (s, t') *idempotent*. Two signals  $\sigma$  and  $\sigma'$  are *equivalent*, iff they differ in idempotent events only. We identify all signals of an equivalence class, as they describe the same physical signal. Each equivalence class  $[\sigma]$  of signals contains a unique signal  $\sigma_0$  having no idempotent events. We say that signal  $\sigma$  switches to s at time t iff event  $(s, t) \in \sigma_0$ .

The state of signal  $\sigma$  at time  $t \in \mathbb{R}_0^+$ , denoted by  $\sigma(t)$ , is given by the state of the event with the maximum time not greater than t.<sup>5</sup> Because of (i), (ii) and (iii),  $\sigma(t)$  is well defined for each time  $t \in \mathbb{R}_0^+$ . Note that  $\sigma$ 's state function in fact depends on  $[\sigma]$  only, i.e., we may add or remove idempotent events at will without changing the state function.

**Distributed System** On the topmost level of abstraction, we see the system as a set of  $V = \{1, \ldots, n\}$  physically remote *nodes* that communicate by means of *channels*. In the context of a VLSI circuit, "physically remote" actually refers to quite small distances (centimeters or even less). However, at gigahertz frequencies, a local state transition will not be observed remotely within a time that is negligible compared to clock speeds. We stress this point, since it is crucial that different clocks (and their attached logic) are not too close to each other, as otherwise they might fail due to the same event such as a particle hit. This would render it pointless to devise a system that is resilient to a certain fraction of the nodes failing.

Each node *i* comprises a number of *input ports*, namely  $S_{i,j}$  for each node *j*, an *output port*  $S_i$ , and a set of *local ports*, introduced later on. An *execution* of the distributed system assigns to each port of each node a signal. For convenience of notation, for any port *p*, we refer to the signal assigned to port *p* simply by signal *p*. We say that *node i is in state s* at time *t* iff  $S_i(t) = s$ . We further say that *node i switches to state s* at time *t* iff signal  $S_i$  switches to *s* at time *t*.

Nodes exchange their states via the channels between them: for each pair of nodes i, j, output port  $S_i$  is connected to input port  $S_{j,i}$  by a FIFO channel from i to j. Note that this includes a channel from i to i itself. Intuitively,  $S_i$  being connected to  $S_{j,i}$  by a (non-faulty) channel means that  $S_{j,i}(\cdot)$  should mimic  $S_i(\cdot)$ , however, with a slight delay accounting for the time it takes the signal to propagate. In contrast to an asynchronous system, this delay is bounded by the maximum delay d > 0.6

Formally we define: The *channel* from node *i* to *j* is said to be *correct* during  $[t^-, t^+]$  iff there exists a function  $\tau_{i,j} : \mathbb{R}_0^+ \to \mathbb{R}_0^+$ , called the channel's *delay function*, such that: (i)  $\tau_{i,j}$  is continuous and strictly increasing, (ii)  $\forall t \in [t^-, t^+] : 0 \leq \tau_{i,j}(t) - t < d$ , and (iii) for each  $t \in [t^-, t^+]$ ,  $(s, \tau_{i,j}(t)) \in S_{j,i} \Leftrightarrow (s, t) \in S_i$ . We say that node *i* observes node *j* in state *s* at time *t* if  $S_{i,j}(t) = s$ .

**Clocks and Timeouts** Nodes are never aware of the current reference time and we also do not require the reference time to resemble Newtonian "real" time. Rather we allow for physical clocks that run arbitrarily fast or slow, as long as their speeds are close to each other in comparison. One may hence think of the reference time as progressing at the speed of the currently slowest correct clock. In this framework, nodes essentially make use of bounded clocks with bounded drift.

Formally, clock rates are within  $[1, \vartheta]$  (with respect to reference time), where  $\vartheta > 1$  is constant and  $\vartheta - 1$  is the *(maximum) clock drift*. A *clock* C is a continuous, strictly increasing function

<sup>&</sup>lt;sup>5</sup>To facilitate intuition, we here slightly abuse notation, as this way  $\sigma$  denotes both a function of time and the signal (trace), which is a subset of  $\mathbb{S} \times \mathbb{R}_0^+$ . Whenever referring to  $\sigma$ , we will talk of the signal, not the state function. <sup>6</sup>With respect to  $\mathcal{O}$ -notation, we normalize  $d \in \mathcal{O}(1)$ , as all time bounds simply depend linearly on d.

$C : \mathbb{R}_0^+ \to \mathbb{R}_0^+$  mapping reference time to some local time. Clock C is said to be *correct* during  $[t^-, t^+] \subseteq \mathbb{R}_0^+$  iff we have for any  $t, t' \in [t^-, t^+]$ , t < t', that  $t' - t \leq C(t') - C(t) \leq \vartheta(t' - t)$ . Each node comprises a set of clocks assigned to it, which allow the node to estimate the progress of reference time.

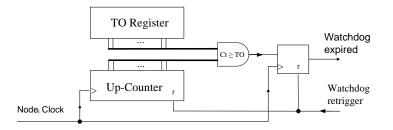

Instead of directly accessing the value of their clocks, nodes have access to so-called *timeout* ports of watchdog timers. A *timeout* is a triple (T, s, C), where  $T \in \mathbb{R}^+$  is a duration,  $s \in \mathbb{S}$  is a state, and C is a clock, say of node i. Each timeout (T, s, C) has a corresponding timeout port Time<sub>T,s,C</sub>, being part of node i's local ports. Signal Time<sub>T,s,C</sub> is Boolean, that is, its possible states are from the set  $\{0, 1\}$ . We say that timeout (T, s, C) is correct during  $[t^-, t^+] \subseteq \mathbb{R}^+_0$  iff clock C is correct during  $[t^-, t^+]$  and the following holds:

- 1. For each time  $t_s \in [t^-, t^+]$  when node *i* switches to state *s*, there is a time  $t \in [t_s, \tau_{i,i}(t_s)]$  such that (T, s, C) is *reset*, i.e.,  $(0, t) \in \text{Time}_{T,s,C}$ . This is a one-to-one correspondence, i.e., (T, s, C) is not reset at any other times.

- 2. For a time  $t \in [t^-, t^+]$ , denote by  $t_0$  the supremum of all times from  $[t^-, t]$  when (T, s, C) is reset. Then it holds that  $(1, t) \in \text{Time}_{T,s,C}$  iff  $C(t) C(t_0) = T$ . Again, this is a one-to-one correspondence.

We say that timeout (T, s, C) expires at time t iff  $\operatorname{Time}_{T,s,C}$  switches to 1 at time t, and it is expired at time t iff  $\operatorname{Time}_{T,s,C}(t) = 1$ . For notational convenience, we will omit the clock C and simply write (T, s) for both the timeout and its signal.

A randomized timeout is a triple  $(\mathcal{D}, s, C)$ , where  $\mathcal{D}$  is a bounded random distribution on  $\mathbb{R}^+_0$ ,  $s \in \mathbb{S}$  is a state, and C is a clock. Its corresponding timeout port  $\operatorname{Time}_{\mathcal{D},s,C}$  behaves very similar to the one of an ordinary timeout, except that whenever it is reset, the local time that passes until it expires next—provided that it is not reset again before that happens—follows the distribution  $\mathcal{D}$ . Formally,  $(\mathcal{D}, s, C)$  is correct during  $[t^-, t^+] \subseteq \mathbb{R}^+_0$ , if C is correct during  $[t^-, t^+]$  and the following holds:

- 1. For each time  $t_s \in [t^-, t^+]$  when node *i* switches to state *s*, there is a time  $t \in [t_s, \tau_{i,i}(t_s)]$  such that  $(\mathcal{D}, s, C)$  is *reset*, i.e.,  $(0, t) \in \text{Time}_{\mathcal{D}, s, C}$ . This is a one-to-one correspondence, i.e.,  $(\mathcal{D}, s, C)$  is not reset at any other times.

- 2. For a time  $t \in [t^-, t^+]$ , denote by  $t_0$  the supremum of all times from  $[t^-, t]$  when  $(\mathcal{D}, s, C)$  is reset. Let  $\mu : \mathbb{R}^+_0 \to \mathbb{R}^+_0$  denote the density of  $\mathcal{D}$ . Then  $(1,t) \in \text{Time}_{\mathcal{D},s,C}$  "with probability  $\mu(C(t) - C(t_0))$ " and we require that the probability of  $(1,t) \in \text{Time}_{\mathcal{D},s,C}$ —conditional to  $t_0$  and C on  $[t_0,t]$  being given—is independent of the system's state at times smaller than t. More precisely, if superscript  $\mathcal{E}$  identifies variables in execution  $\mathcal{E}$  and  $t'_0$  is the infimum of all times from  $(t_0,t^+]$  when node i switches to state s, then we demand for any  $[\tau^-,\tau^+] \subseteq [t_0,t'_0]$ that

$$P\left[\exists t' \in [\tau^{-}, \tau^{+}] : (1, t') \in \text{Time}_{\mathcal{D}, s, C} \left| t_{0}^{\mathcal{E}} = t_{0} \wedge C \right|_{[t_{0}, t']}^{\mathcal{E}} = C \big|_{[t_{0}, t']}\right] = \int_{\tau^{-}}^{\tau^{+}} \mu(C(\tau) - C(t_{0})) d\tau,$$

independently of  $\mathcal{E}|_{[0,\tau^-)}$ .

We will apply the same notational conventions to randomized timeouts as we do for regular timeouts.

Note that, strictly speaking, this definition does not induce a random variable describing the time  $t' \in [t_0, t'_0)$  satisfying that  $(1, t') \in \text{Time}_{\mathcal{D},s,C}$ . However, for the state of the timeout port, we get the meaningful statement that for any  $t' \in [t_0, t'_0)$ ,

$$P[\text{Time}_{\mathcal{D},s,C} \text{ switches to 1 during } [t_0,t']] = \int_{t_0}^{t'} \mu(C(t') - C(t_0)) \ d\tau.$$

The reason for phrasing the definition in the above more cumbersome way is that we want to guarantee that an adversary knowing the full present state of the system and memorizing its whole history cannot reliably predict when the timeout will expire.<sup>7</sup>

We remark that these definitions allow for different timeouts to be driven by the same clock, implying that an adversary may derive some information on the state of a randomized timeout before it expires from the node's behaviour, even if it cannot directly access the values of the clock driving the timeout. This is crucial for implementability, as it might be very difficult to guarantee that the behaviour of a dedicated clock that drives a randomized timeout is indeed independent of the execution of the algorithm.

**Memory Flags** Besides timeout and randomized timeout ports, another kind of node *i*'s local ports are *memory flags*. For each state  $s \in S$  and each node  $j \in V$ ,  $\operatorname{Mem}_{i,j,s}$  is a local port of node *i*. It is used to memorize whether node *i* has observed node *j* in state *s* since the last reset of the flag. We say that node *i memorizes node j in state s* at time *t* if  $\operatorname{Mem}_{i,j,s}(t) = 1$ . Formally, we require that signal  $\operatorname{Mem}_{i,j,s}$  switches to 1 at time *t* iff node *i* observes node *j* in state *s* at time *t* and  $\operatorname{Mem}_{i,j,s}$  is not already in state 1. The times *t* when  $\operatorname{Mem}_{i,j,s}$  is *reset*, i.e.,  $(0, t) \in \operatorname{Mem}_{i,j,s}$ , are specified by node *i*'s state machine, which is introduced next.

**State Machine** It remains to specify how nodes switch states and when they reset memory flags. We do this by means of state machines that may attain states from the finite alphabet S. A node's state machine is specified by (i) the set S, (ii) a function tr, called the *transition function*, from  $\mathcal{T} \subseteq \mathbb{S}^2$  to the set of Boolean predicates on the alphabet consisting of expressions "p = s" (used for expressing guards), where p is from the node's input and local ports and s is from the set of possible states of signal p, and (iii) a function re, called the *reset function*, from  $\mathcal{T}$  to the power set of the node's memory flags.

Intuitively, the transition function specifies the conditions (guards) under which a node switches states, and the reset function determines which memory flags to reset upon the state change. Formally, let P be a predicate on node *i*'s input and local ports. We define P holds at time t by structural induction: If P is equal to p = s, where p is one of node *i*'s input and local ports and s is one of the states signal p can obtain, then P holds at time t iff p(t) = s. Otherwise, if P is of the form  $\neg P_1$ ,  $P_1 \land P_2$ , or  $P_1 \lor P_2$ , we define P holds at time t in the straightforward manner.

We say node *i* follows its state machine during  $[t^-, t^+]$  iff the following holds: Assume node *i* observes itself in state  $s \in S$  at time  $t \in [t^-, t^+]$ , i.e.,  $S_{i,i}(t) = s$ . Then, for each  $(s, s') \in \mathcal{T}$ , both:

1. Node i switches to state s' at time t iff tr(s, s') holds at time t and i is not already in state s'.<sup>8</sup>

<sup>&</sup>lt;sup>7</sup>This is a non-trivial property. For instance nodes could just determine, by drawing from the desired random distribution at time  $t_0$ , at which local clock value the timeout shall expire next. This would, however, essentially give away early when the timeout will expire, greatly reducing the power of randomization!

<sup>&</sup>lt;sup>8</sup>In case more than one guard tr(s, s') can be true at the same time, we assume that an arbitrary tie-breaking ordering exists among the transition guards that specifies to which state to switch.

2. Node *i* resets memory flag *m* at some time in the interval  $[t, \tau_{i,i}(t)]$  iff  $m \in re(s, s')$  and *i* switches from state *s* to state *s'* at time *t*. This correspondence is one-to-one.

A node is defined to be *non-faulty* during  $[t^-, t^+]$  iff during  $[t^-, t^+]$  all its timeouts and randomized timeouts are correct and it follows its state machine. If it employs multiple state machines (see below), it needs to follow all of them.

In contrast, a faulty node may change states arbitrarily. Note that while a faulty node may be forced to send consistent output state signals to all other nodes if its channels remain correct, there is no way to guarantee that this still holds true if channels are faulty.<sup>9</sup>

**Metastability** In our discrete system model, the effect of metastability is captured by the lacking capability of state machines to instantaneously take on new states: Node *i* decides on state transitions based on the delayed status of port  $S_{i,i}$  instead of its "true" current state  $S_i$ . This non-zero delay from  $S_i$  to  $S_{i,i}$  bears the potential for metastability, as a successful state transition can only be guaranteed if after a transition guard from some state *s* to some state *s'* becomes true, all other transition guards from *s* to  $s'' \neq s'$  remain false during this delay at least.

This is exemplified in the following scenario: Assume node *i* is in state *s* at some time *t*. However, since it switched to *s* only very recently, it still observes itself in state  $s' \neq s$  at time *t* via  $S_{i,i}$ . Given that there is a transition (s', s'') in  $\mathcal{T}, s'' \neq s$ , whose condition is fulfilled at time *t*, it will switch to state s'' at time *t* (although state *s* has not even stabilized yet). That is, due to the discrepancy between  $S_{i,i}$  and  $S_i$ , node *i* switches from state *s* to state s'' at time *t* even if (s, s'') is not in  $\mathcal{T}$  at all.<sup>10</sup> In a physical chip design, this premature change of state might even result in inconsistent operations on the local memory, up to the point where it cannot be properly described in terms of S, and thus in terms of our discrete model, anymore. Even worse, the state of *i* is part of the local memory and the node's state signal may attain an undefined value that is propagated to other nodes and their memory. While avoiding the latter is the task of the input ports of a non-faulty node, our goal is to prevent this erroneous behaviour in situations where input ports attain legitimate values only.

Therefore, we define node i to be *metastability-free*, if the situation described above does not occur.

**Definition 2.1** (Metastability-Freedom). Node  $i \in V$  is called metastability-free during  $[t^-, t^+]$ , iff for each time  $t \in [t^-, t^+]$  when i switches to some state  $s \in S$ , it holds that  $\tau_{i,i}(t) < t'$ , where t' is the infimum of all times in  $(t, t^+]$  when i switches to some state  $s' \in S$ .

Multiple State Machines In some situations the previous definitions are too stringent, as there might be different "components" of a node's state machine that act concurrently and independently, mostly relying on signals from disjoint input ports or orthogonal components of a signal. We model this by permitting that nodes run several state machines in parallel. All these state machines share the input and local ports of the respective node and are required to have disjoint state spaces. If node *i* runs state machines  $M_1, \ldots, M_k$ , node *i*'s output signal is the product of the output signals

<sup>&</sup>lt;sup>9</sup>A single physical fault may cause this behaviour, as at some point a node's output port must be connected to remote nodes' input ports. Even if one places bifurcations at different physical locations striving to mitigate this effect, if the voltage at the output port drops below specifications, the values of corresponding input channels may deviate in unpredictable ways.

<sup>&</sup>lt;sup>10</sup>Note that while the "internal" delay  $\tau_{i,i}(t) - t$  can be made quite small, it cannot be reduced to zero if the model is meant to reflect physical implementations.

of the individual machines. Formally we define: Each of the state machines  $M_j$ ,  $1 \le j \le k$ , has an additional own output port  $s_j$ . The state of node *i*'s output port  $S_i$  at any time *t* is given by  $S_i(t) := (s_1(t), \ldots, s_k(t))$ , where the signals of ports  $s_1, \ldots, s_k$  are definied analogously to the signals of the output ports of state machines in the single state machine case, each. Note that by this definition, the only (local) means for node *i*'s state machines to interact with each other is by reading the delayed state signal  $S_{i,i}$ .

We say that node i's state machine  $M_j$  is in state s at time t iff  $s_j(t) = s$ , where  $S_i(t) = (s_1(t), \ldots, s_k(t))$ , and that node i's state machine  $M_j$  switches to state s at time t iff signal  $s_j$  switches to s at time t. Since the state spaces of the machines  $M_j$  are disjoint, we will omit the phrase "state machine  $M_j$ " from the notation, i.e., we write "node i is in state s" or "node i switched to state s", respectively.

Recall that the various state machines of node i are as loosely coupled as remote nodes, namely via the delayed status signal on channel  $S_{i,i}$  only. Therefore, it makes sense to consider them independently also when it comes to metastability.

**Definition 2.2** (Metastability-Freedom (Multiple State Machines)). State machine M of node  $i \in V$  is called metastability-free during  $[t^-, t^+]$ , iff for each time  $t \in [t^-, t^+]$  when M switches to some state  $s \in \mathbb{S}$ , it holds that  $\tau_{i,i}(t) < t'$ , where t' is the infimum of all times in  $(t, t^+]$  when M switches to some state  $s' \in \mathbb{S}$ .

Note that by this definition the different state machines may switch states concurrently without suffering from metastability.<sup>11</sup> It is even possible that some state machine suffers metastability, while another is not affected by this at all.<sup>12</sup>

**Problem Statement** The purpose of the pulse synchronization protocol is that nodes generate synchronized, well-separated pulses by switching to a distinguished state *accept*. Self-stabilization requires that they start to do so within bounded time, for any possible initial state. However, as our protocol makes use of randomization, there are executions where this does not happen at all; instead, we will show that the protocol stabilizes with probability one in finite time. To give a precise meaning to this statement, we need to define appropriate probability spaces.

**Definition 2.3** (Adversarial Spaces). Denote for  $i \in V$  by  $C_i = \{C_{i,k} | k \in \{1, \ldots, c_i\}\}$  the set of clocks of node *i*. An adversarial space is a probabilistic space that is defined by subsets of nodes and channels  $W \subseteq V$  and  $E \subseteq V \times V$ , a time interval  $[t^-, t^+]$ , a protocol  $\mathcal{P}$  (nodes' ports, state machines, etc.) as previously defined, sets of clock and delay functions  $\mathcal{C} = \bigcup_{i \in V} C_i$  and  $\Theta = \{\tau_{i,j} : \mathbb{R}^+_0 \to \mathbb{R}^+_0 | (i, j) \in V^2\}$ , an initial state  $\mathcal{E}_0$  of all ports, and an adversarial function  $\mathcal{A}$ . Here  $\mathcal{A}$  is a function that maps a partial execution  $\mathcal{E}|_{[0,t]}$  until time t (i.e., all ports' values until time t), W, E,  $[t^-, t^+]$ ,  $\mathcal{P}$ ,  $\mathcal{C}$ , and  $\Theta$  to the states of all faulty ports during the time interval (t, t'], where t' is the infimum of all times greater than t when a non-faulty node or channel switches states.

<sup>&</sup>lt;sup>11</sup>However, care has to be taken when implementing the inter-node communication of the state components in a metastability-free manner, cf. Section 6.

$<sup>^{12}</sup>$ This is crucial for the algorithm we are going to present. For stabilization purposes, nodes comprise a state machine that is prone to metastability. However, the state machine generating pulses (i.e., having the state *accept*, cf. Definition 2.4) does not take its output signal into account once stabilization is achieved. Thus, the algorithm is metastability-free after stabilization in the sense that we guarantee a metastability-free signal indicating when pulses occur.

The adversarial space  $\mathcal{AS}(W, E, [t^-, t^+], \mathcal{P}, \mathcal{C}, \Theta, \mathcal{E}_0, \mathcal{A})$  is now defined on the set of all executions  $\mathcal{E}$  satisfying that (i) the initial state of all ports is given by  $\mathcal{E}|_{[0,0]} = \mathcal{E}_0$ , (ii) for all  $i \in V$  and  $k \in \{1, \ldots, c_i\} : C_{i,k}^{\mathcal{E}} = C_{i,k}$ , (iii) for all  $(i, j) \in V^2$ ,  $\tau_{i,j}^{\mathcal{E}} = \tau_{i,j}$ , (iv) nodes in W are non-faulty during  $[t^-, t^+]$  with respect to the protocol  $\mathcal{P}$ , (v) all channels in E are correct during  $[t^-, t^+]$ , and (vi) given  $\mathcal{E}|_{[0,t]}$  for any time t,  $\mathcal{E}|_{(t,t']}$  is given by  $\mathcal{A}$ , where t' is the infimum of times greater than t when a non-faulty node switches states. Thus, except for when randomized timeouts expire,  $\mathcal{E}$  is fully predetermined by the parameters of  $\mathcal{AS}$ .<sup>13</sup> The probability measure on  $\mathcal{AS}$  is induced by the random distributions of the randomized timeouts specified by  $\mathcal{P}$ .

To avoid confusion, observe that if the clock functions and delays do not follow the model constraints during  $[t^-, t^+]$ , the respective adversarial space is empty and thus of no concern. This cumbersome definition provides the means to formalize a notion of stabilization that accounts for worst-case drifts and delays and an adversary that knows the full state of the system up to the current time.

We are now in the position to formally state the pulse synchronization problem in our framework. Intuitively, the goal is that after transient faults cease, nodes should with probability one eventually start to issue well-separated, synchronized pulses by switching to a dedicated state *accept*. Thus, as the initial state of the system is arbitrary, specifying an algorithm<sup>14</sup> is equivalent to defining the state machines that run at each node, one of which has a state *accept*.

**Definition 2.4** (Self-Stabilizing Pulse Synchronization). Given a set of nodes  $W \subseteq V$  and a set  $E \subseteq V \times V$  of channels, we say that protocol  $\mathcal{P}$  is a (W, E)-stabilizing pulse synchronization protocol with skew  $\Sigma$  and accuracy bounds  $T^-, T^+$  that stabilizes within time T with probability p iff the following holds. Choose any time interval  $[t^-, t^+] \supseteq [t^-, t^- + T + \Sigma]$  and any adversarial space  $\mathcal{AS}(W, E, [t^-, t^+], \mathcal{P}, \cdot, \cdot, \cdot)$  (i.e.,  $\mathcal{C}, \Theta, \mathcal{E}_0$ , and  $\mathcal{A}$  are arbitrary). Then executions from  $\mathcal{AS}$  satisfy with probability at least p that there exists a time  $t_s \in [t^-, t^- + T]$  so that, denoting by  $t_i(k)$  the time when node i switches to a distinguished state accept for the  $k^{\text{th}}$  time after  $t_s$  ( $t_i(k) = \infty$  if no such time exists), (i)  $t_i(1) \in (t_s, t_s + \Sigma)$ , (ii)  $|t_i(k) - t_j(k)| \leq \Sigma$  if  $\max\{t_i(k), t_j(k)\} \leq t^+$ , and (iii)  $T^- \leq |t_i(k+1) - t_i(k)| \leq T^+$  if  $t_i(k) + T^+ \leq t^+$ .

Note that the fact that  $\mathcal{A}$  is a deterministic function and, more generally, that we consider each space  $\mathcal{AS}$  individually, is no restriction: As  $\mathcal{P}$  succeeds for any adversarial space with probability at least p in achieving stabilization, the same holds true for randomized adversarial strategies  $\mathcal{A}$  and worst-case drifts and delays.

# 3 The FATAL Pulse Synchronization Protocol

In this section, we present our self-stabilizing pulse generation algorithm. In order to be suitable for implementation in hardware, it needs to utilize very simple rules only. It is stated in terms of a state machine as introduced in the previous section.

Since the ultimate goal of the pulse generation algorithm is to stabilize a system of DARTS clocks, we introduce an additional port  $DARTS_i$ , for each node *i*, which is driven by node *i*'s DARTS

<sup>&</sup>lt;sup>13</sup>This follows by induction starting from the initial configuration  $\mathcal{E}_0$ . Using  $\mathcal{A}$ , we can always extend  $\mathcal{E}$  to the next time when a correct node switches states, and when correct nodes switch states is fully determined by the parameters of  $\mathcal{AS}$  except for when randomized timeouts expire. Note that the induction reaches any finite time within a finite number of steps, as signals switch states finitely often in finite time.

<sup>&</sup>lt;sup>14</sup>We use the terms "algorithm" and "protocol" interchangably throughout this work.

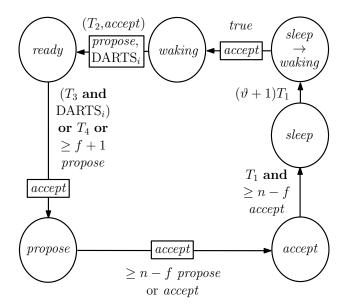

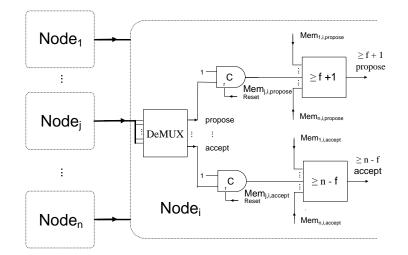

Figure 1: Basic cycle of node i once the algorithm has stabilized.

instance. As for other state signals, its output raises flag  $Mem_{i,DARTS}$ , to which for simplicity we refer to as  $DARTS_i$  as well. Note that the DARTS signals are of no concern to the liveliness or stabilization of the pulse algorithm itself; rather, it is a control signal from the DARTS component that helps in adjusting the frequency of pulses to the speed of the DARTS clocks once the system as a whole (including the DARTS component) is stable. The pulse algorithm will stabilize independently of the DARTS signal, and the DARTS component will stabilize once the pulse component did so. Therefore we can partition the algorithm's analysis into two parts. When proving the correctness of the algorithm in Section 4, we assume that for each node *i*,  $DARTS_i$  is arbitrary. In Section 7, we will outline how the pulse algorithm and DARTS interact.

## 3.1 Basic Cycle

The full algorithm makes use of a rather involved interplay between conditions on timeouts, states, and thresholds to converge to a safe state despite a limited number of faulty components. As our approach is thus difficult to present in bulk, we break it down into pieces. Moreover, to facilitate giving intuition about the key ideas of the algorithm, in this section we assume that there are f < n/3 faulty nodes, and the remaining n - f nodes are non-faulty within  $[0, \infty)$  (where of course the time 0 is unknown to the nodes). We further assume that channels between non-faulty nodes (including loopback channels) are correct within  $[0, \infty)$ . We start by presenting the basic cycle that is repeated every pulse once a safe configuration is reached (see Figure 1).

We employ graphical representations of the state machine of each node  $i \in V$ . States are represented by circles containing their names, while transition  $(s, s') \in \mathcal{T}$  is depicted as an arrow from s to s'. The guard tr(s, s') is written as a label next to the arrow, and the reset function's value re(s, s') is depicted in a rectangular box on the arrow. To keep labels more simple we make use of some abbreviations. We write T instead of (T, s) if s is the state which node i leaves if the condition involving (T, s) is satisfied. Threshold conditions like " $\geq f + 1 s$ ", where  $s \in S$ , abbreviate Boolean predicates that reach over all of node i's memory flags  $\operatorname{Mem}_{i,j,s}$ , where  $j \in V$ , and are defined in a straightforward manner. If in such an expression we connect two states by "or", e.g., " $\geq n - f$  s or s'" for  $s, s' \in \mathbb{S}$ , the summation considers flags of both types s and s'. Thus, such an expression is equivalent to  $\sum_{j \in V} \max\{\operatorname{Mem}_{i,j,s}, \operatorname{Mem}_{i,j,s'}\} \geq f + 1$ . For any state  $s \in \mathbb{S}$ , the condition  $S_{i,j} = s$ , (respectively,  $\neg(S_{i,j} = s)$ ) is written in short as "j in s" (respectively, "j not in s"). If j = i, we simply write "(not) in s". We write "true" instead of a condition that is always true (like e.g. "(in s) **or** (not in s)" for an arbitrary state  $s \in \mathbb{S}$ ). Finally,  $re(\cdot, \cdot)$ always requires to reset all memory flags of certain types, hence we write e.g. propose if all flags  $\operatorname{Mem}_{i,j,propose}$  are to be reset.

We now briefly introduce the basic flow of the algorithm once it stabilizes, i.e., once all n - fnon-faulty nodes are well-synchronized. Recall that the remaining up to f < n/3 faulty nodes may produce arbitrary signals on their outgoing channels. A pulse is locally triggered by switching to state accept. Thus, assume that at some time all non-faulty nodes switch to state accept within a time window of 2d, i.e., a valid pulse is generated. Supposing that  $T_1 \geq 3\vartheta d$ , these nodes will observe, and thus memorize, each other and themselves in state *accept* before  $T_1$  expires. This makes timeout  $T_1$  the critical condition for switching to state *sleep*. From state *sleep*, they will switch to states sleep  $\rightarrow$  waking, waking, and finally ready, where the timeout  $(T_2, accept)$  is determining the time this takes, as it is considerably larger than  $\vartheta(\vartheta+2)T_1$ . The intermediate states serve the purpose of achieving stabilization, hence we leave them out for the moment. Note that upon switching to state ready, nodes reset their propose flags and DARTS<sub>i</sub>. Thus, they essentially ignore these signals between the most recent time they switched to *propose* before switching to *accept* and the subsequent time when they switch to ready. This ensures that nodes do not take into account outdated information for the decision when to switch to state *propose*. Hence, it is guaranteed that the first node switching from state ready to state propose again does so because  $T_4$  expired or because  $T_3$  expired and its DARTS memory flag is true. Due to the constraint min $\{T_3, T_4\} \geq \vartheta(T_2 + 4d)$ , we are sure that all non-faulty nodes observe themselves in state *ready* before the first one switches to propose. Hence, no node deletes information about nodes that switch to propose again after the previous pulse. The first non-faulty node that switches to state *accept* again cannot do so before it memorizes at least n-f nodes in state propose, as the accept flags are reset upon switching to state propose. Therefore, at this time at least  $n-2f \ge f+1$  non-faulty nodes are in state propose. Hence, the rule that nodes switch to propose if they memorize f + 1 nodes in states propose will take effect, i.e., the remaining non-faulty nodes in state ready switch to propose after less than d time. Another d time later all non-faulty nodes in state propose will have become aware of this and switch to state accept as well, as the threshold of n-f nodes in states propose or accept is reached. Thus the cycle is complete and the reasoning can be repeated inductively.

Clearly, for this line of argumentation to be valid, the algorithm could be simpler than stated in Figure 1. We already mentioned that the motivation of having three intermediate states between *accept* and *ready* is to facilitate stabilization. Similarly, there is no need to make use of the *accept* flags in the basic cycle at all; in fact, it adversely affects the constraints the timeouts need to satisfy for the above reasoning to be valid. However, the *accept* flags are much better suited for diagnostic purposes than the *propose* flags, since nodes are expected to switch to *accept* in a small time window and remain in state *accept* for a small period of time only (for all our results, it is sufficient if  $T_1 = 4\vartheta d$ ). Moreover, two different timeout conditions for switching from *ready* to *propose* are unnecessary for correct operation of the pulse synchronization routine. As discussed before, they are introduced in order to allow for a seamless coupling to the DARTS system. We elaborate on this in Section 7.

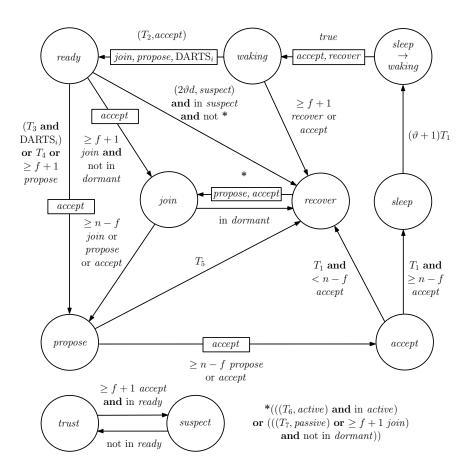

Figure 2: Overview of the core routine of node *i*'s self-stabilizing pulse algorithm.

## 3.2 Main Algorithm

We proceed by describing the main routine of the pulse algorithm in full. Alongside the main routine, several other state machines run concurrently and provide additional information to be used during recovery.

The main routine is graphically presented in Figure 2, together with a very simple second component whose sole purpose is to simplify the otherwise overloaded description of the main routine. Except for the states *recover* and *join* and additional resets of memory flags, the main routine is identical to the basic cycle. The purpose of the two additional states is the following: Nodes switch to state *recover* once they detect that something is wrong, that is, non-faulty nodes do not execute the basic cycle as outlined in Section 3.1. This way, non-faulty nodes will not continue to confuse others by sending for example state signals *propose* or *accept* despite clearly being out-of-sync. There are various consistency checks that nodes perform during each execution of the basic cycle. The first one is that in order to switch from state *accept* to state *sleep*, non-faulty nodes need to memorize at least n - f nodes in state *accept*. If this does not happen within  $T_1$  time after switching to state *accept*, by the arguments given in Section 3.1, they could not have entered state *accept* within 2d of each other. Therefore, something must be wrong and it is feasible to switch to state *recover*. Next, whenever a non-faulty node is in state *waking*, there should be no non-faulty nodes in states *accept* or *recover*. Considering that the node resets its *accept* and

recover flags upon switching to waking, it should not memorize f+1 or more nodes in states accept or recover at a time when it observes itself in state waking. If it does, however, it again switches to state recover. Similarly, when in state ready, nodes expect others not to be in state accept for more than a short period of time, as a non-faulty node switching to accept should imply that every non-faulty node switches to propose and then to accept shortly thereafter. This is expressed by the second state machine comprising two states only. If a node is in state ready and memorizes f+1 nodes in state accept, it switches to suspect. Subsequently, if it remains in state ready until a timeout of  $2\vartheta d$  expires, it will switch to state recover. Last but not least, during a synchronized execution of the basic cycle, no non-faulty node may be in state propose for more than a certain amount of time before switching to state accept. Therefore, nodes will switch from propose to recover when timeout  $T_5$  expires.

Nodes can join the basic cycle again via the second new state, called *join*. Since the Byzantine nodes may "play nice" towards n - 2f or more nodes still executing the basic cycle, making them believe that system operation continues as usual, it must be possible to join the basic cycle again without having a majority of nodes in state *recover*. On the other hand, it is crucial that this happens in a sufficiently well-synchronized manner, as otherwise nodes could drop out again because the various checks of consistency detect an erroneous execution of the basic cycle.

In part, this issue is solved by an additional agreement step. In order to enter the basic cycle again, nodes need to memorize n - f nodes in states join (the respective nodes detected an inconsistency), propose (these nodes continued to execute the basic cycle), or accept (there are executions where nodes reset their propose flags because of switching to join when other nodes already switched to accept). Since there are thresholds of f + 1 nodes memorized in state join both for leaving state recover and switching from ready to join, all nodes will follow the first one switching from join to propose quickly, just as with the switch from propose to accept in an ordinary execution of the basic cycle. However, it is decisive that all nodes are in states that permit to participate in this agreement step in order to guarantee success of this approach.

As a result, still a certain degree of synchronization needs to be established beforehand, both among nodes that still execute the basic cycle and those that do not. For instance, if at the point in time when a majority of nodes and channels become non-faulty, some nodes already memorize nodes in *join* that are not, they may switch to state *join* and subsequently *propose* prematurely, causing others to have inconsistent memory flags as well. Again, Byzantine faults may sustain this amiss configuration of the system indefinitely.

So why did we put so much effort in "shifting" the focus to this part of the algorithm? The key advantage is that nodes outside the basic cycle may take into account less reliable information for stabilization purposes. They may take the risk of metastable upsets (as we know it is impossible to avoid these during the stabilization process, anyway) and make use of randomization.

In fact, to make the above scheme work, it is sufficient that all non-faulty nodes agree on a so called *resynchronization point* (formally defined later on), that is, a point in time at which nodes reset the memory flags for states *join* and *sleep*  $\rightarrow$  *waking* as well as certain timeouts, while guaranteeing that no node is in these states close to the respective reset times. Except for state *sleep*  $\rightarrow$  *waking*, all of these timeouts, memory flags, etc. are not part of the basic cycle at all, thus nodes may enforce consistent values for them when they agree on such a resynchronization point.

Conveniently, the use of randomization also ensures that it is quite unlikely that nodes are in state  $sleep \rightarrow waking$  close to a resynchronization point, as the consistency check of having to memorize n - f nodes in state *accept* in order to switch to state *sleep* guarantees that the time

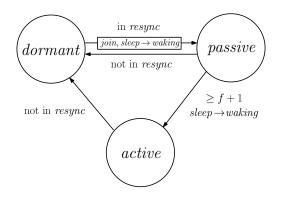

Figure 3: Extension of node *i*'s core routine.

windows during which non-faulty nodes may switch to *sleep* make up a small fraction of all times only.

Consequently, the remaining components of the algorithm deal with agreeing on resynchronization points and utilizing this information in an appropriate way to ensure stabilization of the main routine. We describe this connection to the main routine first. It is done by another, quite simple state machine, which runs in parallel alongside the core routine. It is depicted in Figure 3.

Its purpose is to reset memory flags in a consistent way and to determine when a node is permitted to switch to *join*. In general, a resynchronization point (locally observed by switching to state *resync*, which is introduced later) triggers the reset of the *join* and *sleep*  $\rightarrow$  *waking* flags. If there are still nodes executing the basic cycle, a node may become aware of it by observing f + 1nodes in state *sleep*  $\rightarrow$  *waking* at some time. In this case it switches from the state *passive*, which it entered at the point in time when it locally observed the resynchronization point, to the state *active*, which enables an earlier transition to state *join*. This is expressed by the rather involved transition rule tr(recover, join):  $T_6$  is much smaller than  $T_7$ , but  $T_6$  is of no concern until the node switches to state *active* and resets  $T_6$ .<sup>15</sup>

It remains to explain how nodes agree on resynchronization points.

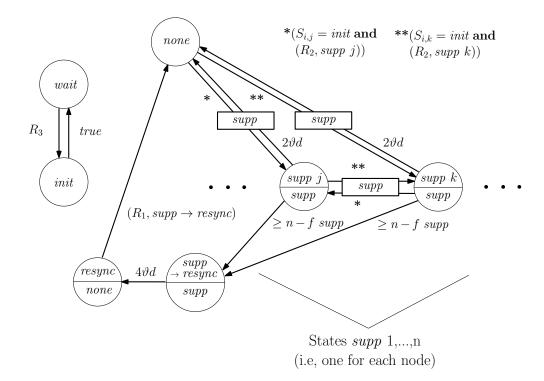

### 3.3 Resynchronization Algorithm

The resynchronization routine is specified in Figure 4 as well. It is a lower layer that the core routine uses for stabilization purposes only. It provides some synchronization that is very similar to that of a pulse, except that such "weak pulses" occur at random times, and may be generated inconsistently after the algorithm as a whole has stabilized. Since the main routine operates independently of the resynchronization routine once the system has stabilized, we can afford the weaker guarantees of the routine: If it succeeds in generating a "good" resynchronization point merely once, the main routine will stabilize deterministically.

**Definition 3.1** (Resynchronization Points). Given  $W \subseteq V$ , time t is a W-resynchronization point iff each node in W switches to state supp  $\rightarrow$  resync in the time interval (t, t + 2d).

Definition 3.2 (Good Resynchronization Points). A W-resynchronization point is called good if

<sup>&</sup>lt;sup>15</sup>The condition "not in *dormant*" here ensures that the transition is not performed because the node has been in state *resync* a long time ago, but there was no recent switching to *resync*.

Figure 4: Resynchronization algorithm, comprising two state machines executed in parallel at node i.

no node from W switches to state sleep during  $(t - (\vartheta + 3)T_1, t)$  and no node is in state join during  $[t - T_1 - d, t + 4d)$ .

In order to clarify that despite having a linear number of states  $(supp_1, \ldots, supp_n)$ , this part of the algorithm can be implemented using 2-bit communication channels between state machines only, we generalize our description of state machines as follows. If a state is depicted as a circle separated into an upper and a lower part, the upper part denotes the local state, while the lower part indicates the signal state to which it is mapped. A node's memory flags then store the respective signal states only, i.e., remote nodes do not distinguish between states that share the same signal. Clearly, such a machine can be simulated by a machine as introduced in the model section. The advantage is that such a mapping can be used to reduce the number of transmitted state bits; for the resynchronization routine given in Figure 4, we merely need two bits (init/wait and none/supp)instead of  $\lceil \log(n+3) \rceil + 1$  bits.

The basic idea behind the resynchronization algorithm is the following: Every now and then, nodes will try to initiate agreement on a resynchronization point. This is the purpose of the small state machine on the left in Figure 4. Recalling that the transition condition "true" simply means that the node switches to state *wait* again as soon as it observes itself in state *init*, it is easy to see that it does nothing else than creating an *init* signal as soon as  $R_3$  expires and resetting  $R_3$  again as quickly as possible. As the time when a node switches to *init* is determined by the randomized timeout  $R_3$  distributed over a large interval (cf. Equality (11)) only, it is impossible to predict when it will expire, even with full knowledge of the execution up to the current point in time. Note that the complete independence of this part of node *i*'s state from the remaining protocol implies that faulty nodes are not able to influence the respective times by any means.

Consider now the state machine displayed on the right of Figure 4. To understand how the routine is intended to work, assume that at the time t when a non-faulty node i switches to state *init*, all non-faulty nodes are not in any of the states  $supp \to resync$ , resync, or supp i, and at all non-faulty nodes the timeout  $(R_2, supp i)$  has expired. Then, no matter what the signals from faulty nodes or on faulty channels are, all non-faulty nodes will be in one of the states supp j,  $j \in V$ , or  $supp \to resync$  at time t + d. Hence, they will observe each other (and themselves) in one of these states at some time smaller than t + 2d. These statements follow from the various timeout conditions of at least  $2\vartheta d$  and the fact that observing node i in state *init* will make nodes switch to state  $supp \downarrow i$  if in none or supp j,  $j \neq i$ . Hence, all of them will switch to state  $supp \to resync$  during (t, t + 2d), i.e., t is a resynchronization point. Since t follows a random distribution that is independent of the remaining algorithm and, as mentioned earlier, most of the times nodes cannot switch to state *sleep* and it is easy to deal with the condition on *join* states, there is a large probability that t is a good resynchronization point. Note that timeout  $R_1$  makes sure that no non-faulty node will switch to  $supp \to resync$  again anytime soon, leaving sufficient time for the main routine to stabilize.

The scenario we just described relies on the fact that at time t no node is in state  $supp \rightarrow resync$ or state resync. We will choose  $R_2 \gg R_1$ , implying that  $R_2 + 3d$  time after a node switched to state *init* all nodes have "forgotten" about this, i.e.,  $(R_2, supp i)$  is expired and they switched back to state *none* (unless other *init* signals interfered). Thus, in the absence of Byzantine faults, the above requirement is easily achieved with a large probability by choosing  $R_3$  as a uniform distribution over some interval  $[R_2 + 3d, R_2 + \Theta(nR_1)]$ : Other nodes will switch to *init*  $\mathcal{O}(n)$  times during this interval, each time "blocking" other nodes for at most  $\mathcal{O}(R_1)$  time. If the random choice picks any other point in time during this interval, a resynchronization point occurs. Even if the clock speed of the clock driving  $R_3$  is manipulated in a worst-case manner (affecting the density of the probability distribution with respect to real time by a factor of at most  $\vartheta$ ), we can just increase the size of the interval to account for this.

However, what happens if only *some* of the nodes receive an *init* signal due to faulty channels or nodes? If the same holds for some of the subsequent supp signals, it might happen that only a fraction of the nodes reaches the threshold for switching to state  $supp \rightarrow resync$ , resulting in an inconsistent reset of flags and timeouts across the system. Until the respective nodes switch to state *none* again, they will not support a resynchronization point again, i.e., about  $R_1$  time is "lost". This issue is the reason for the agreement step and the timeouts  $(R_2, supp j)$ . In order for any node to switch to state  $supp \rightarrow resync$ , there must be at least  $n-2f \ge f+1$  non-faulty nodes supporting this. Hence, all of these nodes recently switched to a state supp j for some  $j \in V$ , resetting  $(R_2, supp j)$ . Until these timeouts expire,  $f + 1 \in \Omega(n)$  non-faulty nodes will ignore *init* signals on the respective channels. Since there are  $\mathcal{O}(n^2)$  channels, it is possible to choose  $R_2 \in \mathcal{O}(nR_1)$ such that this may happen at most  $\mathcal{O}(n)$  times in  $\mathcal{O}(n)$  time. Playing with constants, we can pick  $R_3 \in \mathcal{O}(n)$  maintaining that still a constant fraction of the times are "good" in the sense that  $R_3$ expiring at a non-faulty node will result in a good resynchronization point.

#### 3.4 Timeout Constraints

Condition 3.3 summarizes the constraints we require on the timeouts for the core routine and the resynchronization algorithm to act and interact as intended.

Condition 3.3 (Timeout Constraints). Define

$$\lambda := \sqrt{\frac{25\vartheta - 9}{25\vartheta}} \in \left(\frac{4}{5}, 1\right),\tag{1}$$

$\Delta_g := (\vartheta + 3)T_1, \ \Delta_s := T_2/\vartheta - 2T_1 - d, \ \delta_s := 2T_1 + 3d, \ and \ \tilde{\delta}_s := (\vartheta + 2 - 1/\vartheta)T_1 + 4d.$  The timeouts need to satisfy the constraints

$$T_1 \geq \vartheta 4d \tag{2}$$

$$T_2 \geq \vartheta \max\left\{T_1 + \Delta_g - (4\vartheta^2 + 16\vartheta + 5)d, \left(3\vartheta + 1 - \frac{1}{\vartheta}\right)T_1 + T_5\right\}$$

(3)

$$T_{3} \geq \max\{(\vartheta - 1)T_{2} + \vartheta(2T_{1} + (2\vartheta + 4)d), (2\vartheta^{2} + 3\vartheta - 1)T_{1} - T_{2} + \vartheta(T_{6} + 5d)\}$$

(4)

$$T_{4} \geq T_{3}$$

(5)

$$T_5 \geq \max \left\{ \vartheta(T_4 + 7d) - T_3 + (\vartheta - 1)T_2, (\vartheta^2 + \vartheta - 2)T_1 + \vartheta(T_2 + T_4 + 9d) - T_6 \right\}$$

(6)

$$T_{6} \geq \vartheta \left( \tilde{\delta}_{s} - \left( 1 - \frac{1}{\vartheta} \right) T_{1} + T_{2} + 2d \right) > \vartheta \Delta_{s}$$

$$(7)$$

$$T_7 \geq \vartheta (T_2 + T_4 + T_5 + \Delta_s + \tilde{\delta}_s - \Delta_g + d) + T_6 - 4d \tag{8}$$

$$R_1 \geq \vartheta \max\left\{T_7 + (4\vartheta + 8)d, \left(2\vartheta + 4 - \frac{3}{\vartheta}\right)T_1 + 2T_4 + T_5 - \Delta_s - \Delta_g + 17d\right\}$$

(9)

$$R_2 \geq \frac{2\vartheta(R_1 + (\vartheta + 2)T_1 + T_2/\vartheta + (8\vartheta + 9)d)(n - f)}{1 - \lambda}$$

(10)

$$R_{3} = uniformly \ distributed \ random \ variable \ on \ [\vartheta(R_{2}+3d), \vartheta(R_{2}+3d) + 8(1-\lambda)R_{2}] \ (11)$$

$$\lambda \leq \frac{\Delta_{s} - \Delta_{g} - \delta_{s}}{(12)}$$

$$\lambda \leq \frac{12}{\Delta_s}.$$

We need to show for which values of  $\vartheta$  this system can be solved. Furthermore, we would like

We need to show for which values of  $\vartheta$  this system can be solved. Furthermore, we would like to allow for the largest possible drift of DARTS clocks, which necessitates to maximize the ratio  $(T_2 + T_4)/(\vartheta(T_2 + T_3 + 4d))$ , that is, the minimal gap between pulses provided that the states of the DARTS signals are zero divided by the maximal time it takes nodes to observe themselves in state ready with  $T_3$  expired after a pulse (as then they will respond to DARTS<sub>i</sub> switching to one).

**Lemma 3.4.** Define  $\vartheta_{\max} \approx 1.247$  as the positive solution of  $2\vartheta + 1 = \vartheta^3 + \vartheta^2$ . Given that  $\vartheta < \vartheta_{\max}$ , Condition 3.3 can be satisfied with  $T_1, \ldots, T_7, R_1 \in \mathcal{O}(1)$  and  $R_2 \in \mathcal{O}(n)$ . The ratio

$$\frac{(T_2+T_4)/\vartheta}{T_2+T_3+4d}$$

can be made larger than any constant smaller than

$$\frac{\vartheta^3 + 2\vartheta + 1}{2\vartheta^4 + \vartheta^3}$$

*Proof.* First, we identify several redundant inequalities in the system. We have that

$$\begin{pmatrix} 2\vartheta + 2 - \frac{1}{\vartheta} \end{pmatrix} T_1 + T_5 \stackrel{(6)}{>} 3\vartheta T_1 + T_2 + T_4 - T_6 \stackrel{(4,5)}{>} 7\vartheta T_1 \\ > T_1 + \Delta_g - (4\vartheta^2 + 16\vartheta + 5)d_5$$

i.e., the left term in the maximum in Inequality (3) is redundant. The same holds true for the left terms in the maxima in Inequality (4) and Inequality (6), since

$$(2\vartheta^{2} + 3\vartheta - 1)T_{1} - T_{2} + \vartheta(T_{6} + 5d) \stackrel{(7)}{>} 3\vartheta T_{1} + (\vartheta - 1)T_{2} + 4d \stackrel{(2)}{>} (\vartheta - 1)T_{2} + \vartheta(2T_{1} + (2\vartheta + 4)d)$$

and

$$\vartheta(T_4 + 7d) - T_3 + (\vartheta - 1)T_2 \stackrel{(4)}{<} \vartheta(T_2 + T_4 - T_6 + 7d) < (\vartheta^2 + \vartheta - 2)T_1 + \vartheta(T_2 + T_4 + 9d) - T_6.$$

Finally, we can eliminate the right term in the maximum in Inequality (9) from the system, as

$$T_{7} + (4\vartheta + 8)d \stackrel{(8)}{>} T_{2} + T_{4} + T_{5} + T_{6} + 2\tilde{\delta}_{s} - \Delta_{g} + 13d$$

$$\stackrel{(3)}{>} \left(2\vartheta + 4 - \frac{3}{\vartheta}\right)T_{1} + T_{4} + 2T_{5} + T_{6} - \Delta_{g} + 17d$$

$$\stackrel{(6)}{>} \left(2\vartheta + 4 - \frac{3}{\vartheta}\right)T_{1} + T_{2} + 2T_{4} + T_{5} - \Delta_{g} + 17d.$$

Next, it is not difficult to see that the right hand sides of all inequalities are strictly increasing in  $T_1$  (except for Inequality (12), whose right hand side decreases with  $T_1$ ), implying that w.l.o.g. we may set  $T_1 := 4\vartheta d$ . Similarly, we demand that Inequality (8), Inequality (9), and Inequality (10) are satisfied with equality, i.e.,

$$T_7 = \vartheta(T_2 + T_4 + T_5) + T_6 - (4\vartheta^2 + 4)d$$

$$R_1 = \vartheta T_7 + (4\vartheta^2 + 8\vartheta)d$$

$$R_2 = \frac{2\vartheta(R_1 + T_2/\vartheta + (4\vartheta^2 + 16\vartheta + 9)d)(n - f)}{1 - \lambda}$$

$$R_3 = \text{uniformly distributed random variable on } [\vartheta(R_2 + 3d), \vartheta(R_2 + 3d) + 8(1 - \lambda)R_2].$$

We set  $T_4 := \alpha T_3$  for a parameter

$$\alpha \in \left[1, \frac{2\vartheta + 1}{\vartheta^3 + \vartheta^2}\right),\,$$

implying that Inequality (5) holds by definition. The remaining simpler system is as follows.

$$T_2 \geq (8\vartheta^3 + 8\vartheta^2 - 4\vartheta)d + \vartheta T_5 \tag{13}$$

$$T_3 \geq (8\vartheta^3 + 12\vartheta^2 + \vartheta)d - T_2 + \vartheta T_6 \tag{14}$$

$$T_5 \geq (4\vartheta^3 + 4\vartheta^2 + \vartheta)d + \vartheta(T_2 + \alpha T_3) - T_6$$

(15)

$$T_6 \geq (4\vartheta^2 + 6\vartheta - 4)d + T_2 \tag{16}$$

$$\sqrt{\frac{25\vartheta - 9}{25\vartheta}} \leq \frac{T_2/\vartheta - (4\vartheta^2 + 28\vartheta + 4)d}{T_2/\vartheta - (8\vartheta + 1)d}.$$

Note the above equalities do not affect this system and can be resolved iteratively once the other variables are fixed. We observe that the right hand side of Inequality (13) is increasing in  $T_5$ , the

right hand side of Inequality (15) is increasing in  $T_3$ , and neither  $T_3$  nor  $T_5$  are present in any further inequalities. Hence, we rule that Inequality (14) and Inequality (15) shall be satisfied with equality, i.e.,

$$T_3 = (8\vartheta^3 + 12\vartheta^2 + \vartheta)d - T_2 + \vartheta T_6$$

$$T_5 = (\alpha(8\vartheta^4 + 12\vartheta^3 + \vartheta^2) + (4\vartheta^3 + 4\vartheta^2 + \vartheta))d - (\vartheta\alpha - 1)T_2 + (\vartheta^2\alpha - 1)T_6$$

and arrive at the subsystem

$$T_{2} \geq \frac{(\alpha(8\vartheta^{5} + 12\vartheta^{4} + \vartheta^{3}) + (4\vartheta^{4} + 12\vartheta^{3} + 9\vartheta^{2} - 4\vartheta))d + (\vartheta^{3}\alpha - \vartheta)T_{6}}{1 + \vartheta - \vartheta^{2}\alpha}$$

$$T_{6} \geq (4\vartheta^{2} + 6\vartheta - 4)d + T_{2}$$

$$T_{2} \geq \frac{(4\vartheta^{3} + 20\vartheta^{2} + 3\vartheta)d}{1 - \sqrt{(25\vartheta - 9)/(25\vartheta)}},$$

$$(17)$$

where we used that  $1 + \vartheta - \vartheta^2 \alpha > 0$ . Now we can see that Inequality (17) is also increasing in  $T_6$ , set

$$T_6 := (4\vartheta^2 + 6\vartheta - 4)d + T_2$$

and obtain

$$T_2 \geq \frac{(\alpha(12\vartheta^5 + 18\vartheta^4 - 3\vartheta^3) + (4\vartheta^4 + 8\vartheta^3 + 3\vartheta^2))d}{1 + 2\vartheta - (\vartheta^3 + \vartheta^2)\alpha}$$

(18)

$$T_2 \geq \frac{25(1+\sqrt{(25\vartheta-9)/(25\vartheta)})(4\vartheta^4+20\vartheta^3+3\vartheta^2)d}{9},$$

(19)

exploiting that  $1 + 2\vartheta - (\vartheta^3 + \vartheta^2)\alpha > 0$ .

Since  $\alpha$  and thus  $\vartheta$  are constantly bounded (and we treat d as constant as well), we have a feasible solution for  $T_2 \in \mathcal{O}(1)$  (considering asymptotic with respect to n). Resolving the equalities we derived for the other variables, we see that  $T_1, \ldots, T_7, R_1 \in \mathcal{O}(1)$  and  $R_2 \in \mathcal{O}(n)$  as claimed.

It remains to determine the maximal ratio  $(T_2 + T_4)/(\vartheta(T_2 + T_3 + 4d)) = (T_2 + \alpha T_3)/(\vartheta(T_2 + T_3 + 4d))$  we can ensure. Obviously, for any value of  $\alpha$ , fixing either  $T_2$  or  $T_3$  implies that we want to minimize  $T_2$  or maximize  $T_3$ , respectively. Have a look at Inequalities (13)–(16) again. The solution we constructed minimized  $T_3$  and subsequently  $T_2$ , parametrized by feasible values of  $\alpha$ . Increase now  $T_3$  by  $x \in \mathbb{R}^+$  in Inequality (14). Consequently, we may increase  $T_6$  in Inequality (16) by  $x/\vartheta$  compared to our previous solution (where we minimized all inequalities). Hence, we need to increase  $T_5$  by  $(\vartheta \alpha - 1/\vartheta)x$  according to Inequality (15), and finally  $T_2$  by  $\vartheta(\vartheta \alpha - 1/\vartheta)x$ . Thus, for any feasible  $\alpha$  and any  $\varepsilon > 0$ , we can achieve that  $T_2 \leq (\vartheta^2 \alpha - 1 + \varepsilon)T_3$  if we just choose x large enough. We conclude that we can get arbitrarily close to the ratio

$$\frac{(\alpha + (\vartheta^2 \alpha - 1))T_3}{\vartheta(1 + (\vartheta^2 \alpha - 1))T_3} = \frac{\vartheta^2 \alpha + \alpha - 1}{\vartheta^3 \alpha}.$$

Inserting the supremum of admissible values for  $\alpha$ , this expression becomes

$$\frac{(2\vartheta+1)(\vartheta^2+1)-(\vartheta^3+\vartheta^2)}{\vartheta^3(2\vartheta+1)} = \frac{\vartheta^3+2\vartheta+1}{2\vartheta^4+\vartheta^3}.$$

This shows the last claim of the lemma, concluding the proof.

# 4 Analysis

In this section we derive skew bounds  $\Sigma$ , as well as accuracy bounds  $T^-, T^+$ , such that the presented protocol is a (W, E)-stabilizing pulse synchronization protocol, for proper choices of the set of nodes W and the set of channels E, with skew  $\Sigma$  and accuracy bounds  $T^-, T^+$  that stabilizes within time  $T(k) \in \mathcal{O}(kn)$  with probability  $1 - 1/2^{k(n-f)}$ , for any  $k \in \mathbb{N}$ .

To start our analysis, we need to define the basic requirements for stabilization. Essentially, we need that a majority of nodes is non-faulty and the channels between them are correct. However, the first part of the stabilization process is simply that nodes "forget" about past events that are captured by their timeouts. Therefore, we demand that these nodes indeed have been non-faulty for a time period that is sufficiently large to ensure that all timeouts have been reset at least once after the considered set of nodes became non-faulty.

**Definition 4.1** (Coherent States). The subset of nodes  $W \subseteq V$  is called coherent during the time interval  $[t^-, t^+]$ , iff during  $[t^- - (\vartheta(R_2 + 3d) + 8(1 - \lambda)R_2) - d, t^+]$  all nodes  $i \in W$  are non-faulty, and all channels  $S_{i,j}$ ,  $i, j \in W$ , are correct.

We will show that if a coherent set of at least n - f nodes fires a pulse, i.e., switches to *accept* in a tight synchrony, this set will generate pulses deterministically and with controlled frequency, as long the set remains coherent. This motivates the following definitions.

**Definition 4.2** (Stabilization Points). We call t a W-stabilization point (quasi-stabilization point) iff all nodes  $i \in W$  switch to accept during [t, t + 2d) ([t, t + 3d)).

Throughout this section, we assume the set of coherent nodes W with  $|W| \ge n-f$  to be fixed and consider all nodes in and channels originating from  $V \setminus W$  as (potentially) faulty. As all our statements refer to nodes in W, we will typically omit the word "non-faulty" when referring to the behaviour or states of nodes in W, and "all nodes" is short for "all nodes in W". Note, however, that we will still clearly distinguish between channels originating at faulty and non-faulty nodes, respectively, to nodes in W.

As a first step, we observe that at times when W is coherent, indeed all nodes reset their timeouts, basing the respective state transition on proper perception of nodes in W.

**Lemma 4.3.** If the system is coherent during the time interval  $[t^-, t^+]$ , any (randomized) timeout (T, s) of any node  $i \in W$  expiring at a time  $t \in [t^-, t^+]$  has been reset at least once since time  $t^- - (\vartheta(R_2 + 3d) + 8(1 - \lambda)R_2)$ . If t' denotes the time when such a reset occurred, for any  $j \in W$  it holds that  $S_{i,j}(t') = S_j(\tau_{j,i}^{-1}(t'))$ , i.e., at time t', i observes j in a state j attained when it was non-faulty.

Proof. According to Condition 3.3, the largest possible value of any (randomized) timeout is  $\vartheta(R_2 + 3d) + 8(1 - \lambda)R_2$ . Hence, any timeout that is in state 1 at a time smaller than  $t^- - (\vartheta(R_2 + 3d) + 8(1 - \lambda)R_2)$  expires before time  $t_1$  or is reset at least once. As by the definition of coherency all nodes in W are non-faulty and all channels between such nodes are correct during  $[t^- - (\vartheta(R_2 + 3d) + 8(1 - \lambda)R_2) - d, t^+]$ , this implies the statement of the lemma.

Phrased informally, any corruption of timeout and channel states eventually ceases, as correct timeouts expire and correct links remember no events that lie d or more time in the past. Proper cleaning of the memory flags is more complicated and will be explained further down the road.

Throughout this section, we will assume for the sake of simplicity that the system is coherent at all times and use this lemma implicitly, e.g. we will always assume that nodes from W will observe all other nodes from W in states that they indeed had less than d time ago, expiring of randomized timeouts at non-faulty nodes cannot be predicted accurately, etc. We will discuss more general settings in Section 5.

We proceed by showing that once all nodes in W switch to *accept* in a short period of time, i.e., a W-quasi-stabilization point is reached, the algorithm guarantees that synchronized pulses are generated deterministically with a frequency that is bounded both from above and below.

**Theorem 4.4.** Suppose t is a W-quasi-stabilization point. Then

- (i) all nodes in W switch to accept exactly once within [t, t + 3d), and do not leave accept until t + 4d, and

- (ii) there will be a W-stabilization point  $t' \in (t + (T_2 + T_3)/\vartheta, t + T_2 + T_4 + 5d)$  satisfying that no node in W switches to accept in the time interval [t + 3d, t') and that

- (iii) each node i's,  $i \in W$ , core state machine (Figure 1) is metastability-free during [t+4d, t'+4d).

*Proof.* Proof of (i): Due to Inequality (2), a node does not leave the state *accept* earlier than  $T_1/\vartheta \ge 4d$  time after switching to it. Thus, no node can switch to *accept* twice during [t, t+3d). By definition of a quasi-stabilization point, every node does switch to *accept* in the interval  $[t, t+3d) \subset [t, t+T_1/\vartheta)$ . This proves Statement (i).

Proof of (ii): For each  $i \in W$ , let  $t_i \in [t, t+3d)$  be the time when *i* switches to *accept*. By (i)  $t_i$  is well-defined. Further let  $t'_i$  be the infimum of times in  $(t_i, \infty)$  when *i* switches to *recover*, *join*, or *propose*.<sup>16</sup> In the following, denote by  $i \in W$  a node with minimal  $t'_i$ .

We will show that all nodes switch to propose via states sleep, sleep  $\rightarrow$  waking, waking, and ready in the presented order. By (i) nodes do not leave accept before t + 4d. Thus at time t + 4d, each node in W is in state accept and observes each other node in W in accept. Hence, each node in W memorizes each other node in W in accept at time t + 4d. For each node  $j \in W$ , let  $t_{j,s}$  be the time node j's timeout  $T_1$  expires first after  $t_j$ . Then  $t_{j,s} \in (t_j + T_1/\vartheta, t_j + T_1 + d)$ .<sup>17</sup> Since  $|W| \ge n - f$ , each node j switches to state sleep at time  $t_{j,s}$ . Hence, by time  $t + T_1 + 4d$ , no node will be observed in state accept anymore (until the time when it switches to accept again).

When a node  $j \in W$  switches to state waking at the minimal time  $t_w$  larger than  $t_j$ , it does not do so earlier than at time  $t + T_1/\vartheta + (1 + 1/\vartheta)T_1 = t + (1 + 2/\vartheta)T_1 > t + T_1 + 5d$ . This implies that all nodes in W have already left accept at least d time ago, since they switched to it at their respective times  $t_j < t + T_1 + 4d$ . Moreover, they cannot switch to accept again until  $t'_i$  as it is minimal and nodes need to switch to propose before switching to accept. Hence, nodes in W are not observed in state accept during  $(t + T_1 + 5d, t'_i]$ , in particular not by node j. Furthermore, nodes in W are not observed in state recover during  $(t_w - d, t'_i]$ . As it resets its accept and recover flags upon switching to waking, j will hence neither switch from waking to recover nor from trust to suspect during  $(t_w, t'_i]$ , and thus also not from ready to recover.

Now consider node *i*. By the previous observation, it will not switch from *waking* to *recover*, but to *ready*, following the basic cycle. Consequently, it must wait for timeout  $T_2$  to expire, i.e.,