Abstract

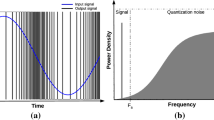

This paper addresses the problem of implementing narrow-band FIR filters using FPGAs. Rather than employing a conventional multiply-accumulate unit to compute the inner-product, an alternative method based on re-quantization of the input data stream using a sigma-delta modulator is presented. The re-quantization process preserves the dynamic range of the signal components contained in the bandwidth of the filter, while shifting the re-quantization noise to the spectral region to be rejected by the filter. The reduced bit length representation of the re-quantized input data samples removes the requirment for a full multiplier in the filter hardware. This makes the method very attractive for realization using FPGA technology. The filtering technique is described and implementation results using a Xilinx XC4010 FPGA are presented. A 200-tap filter implemented in a single FPGA achieves a computation rate of 415 MOPS and has a memory bandwidth of 1.66 Gbytes/s. An extension of the method using a quadrature re-quantizer and filter is also presented.

Similar content being viewed by others

References

J. Isoaho, “FPGA-implementable digital filters,”More FPGAs, W. Moore and W. Luk (Eds.),Abingdon EE&CS Books, Oxford, England, pp. 281–290, 1994.

S. Mohanakrishnan and J.B. Evans, “Automatic implementation of FIR filters on field programmable gate arrays,”IEEE Signal Processing Letters, Vol. 2, No. 3, pp. 51–53, March 1995.

Xilinx Inc.,The Programmable Logic Data Book, 1994.

J. Isoaho, J. Pasanen, and O. Vainio, “DSP system integration and prototyping with FPGAs,”Journal of VLSI Signal Processing, No. 6, pp. 155–172, 1993.

A.E. de la Serna and M.A. Soderstrand, “Trade-off between FPGA resource utilization and roundoff error in optimized CSD FIR digital filters,”Twenty-Eighth Asilomar Conference on Signals, Systems & Computers, IEEE Computer Society Press, Pacific Grove, California, pp. 120–127, Oct. 31–Nov. 2, 1994.

P.J. Graumann and L.E. Turner, “Implementing digital signal processing algorithms using pipelined bit-serial arthmetic and field programmable gate arrays,”Proceedings of FPGA 1992, pp. 123–128, 1992.

L. Mintzer, “FIR filters with field-programmable gate arrays,”Journal of VLSI Signal Processing, No. 6, pp. 120–127, 1993.

S.A. White, “Applications of distributed arithmetic to digital signal processing,”IEEE ASSP Magazine, Vol. 6, No. 3, pp. 4–19, July 1989.

A. Peled and B. Liu, “A new hardware realization of digital filters,”IEEE Trans. on Acoust., Speech, Signal Processing, Vol. ASSP-22, pp. 456–462, Dec. 1974.

G. Goslin and B. Newgard, “16-tap, 8-bit FIR filter applications guide,”Xilinx Application Note, pp. 25–28, Nov. 1994.

J.C. Candy and G.C. Temes, “Oversampling methods for A/D and D/A conversion,” inOversampling Delta-Sigma Data Converters—Theory Design and Simulation, IEEE Press, New York, 1992.

Xilinx Inc.XACT Libraries Guide, 0401098 01, April 1994.

Texas Instruments,Third generation TMS320 User's Guide, Texas Instruments, Austin Texas, 1988.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Dick, C., Harris, F. Narrow-band FIR filtering with FPGAs using sigma-delta modulation encoding. J VLSI Sign Process Syst Sign Image Video Technol 14, 265–282 (1996). https://doi.org/10.1007/BF00929620

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF00929620