Abstract

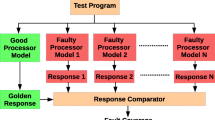

It has been shown that the hierarchy of large VLSI circuits can be exploited to speed up the test generation process. However, severe problems remain in most of the published literature which were based on a high level branch-and-bound approach. When the circuit module diagram is complex, it is very difficult to formalize the high level knowledge derived from the circuit hierarchy to make successful decisions in searching. Whenever a global path conflict or value conflict happens, it is unlikely that the backtracking scheme is able to solve this conflict through high level knowledge manipulation. In this article, a new architectural level test generation algorithm based on a nonlinear equation-solving methodology is proposed to solve conflicts and avoid making high level decisions when the tests are computed. For each pattern to be justified at a high level, an instruction sequence and the under-determined system of nonlinear equations are derived based on preprocessing information. The solution of the system of equations are calculated by a signal-driven discrete relaxation algorithm without making any high level decision. The test generation is performed by recursively assembling the instruction sequence and solving the system of equations. This new test generation approach has been implemented, and the tests of several microprocessors have been generated successfully. The results show that this approach is effective and promising.

Similar content being viewed by others

References

O. Ibarra and S. Sahni, “Polynomially complete fault detection problems,IEEE Trans. on Computers, vol. C 24, pp. 242–249, March 1975.

H.T. Ma, S. Devadas, A. Newton, and A. Sangiovanni-Vincentelli, “Test generation for sequential circuits,”Proc. IEEE Int. Conf. on Computer-Aided Design, pp. 1081–1093, October 1988.

W. Cheng, “The back algorithm for sequential test generation,”Proc. IEEE Int. Conf. on Computer Design, pp. 66–69, October 1988.

V. Agrawal, K. Cheng, and P. Agrawal, “Contest: A concurrent test generator for sequential circuits,”Proc. 25th Design Automation Conference, pp. 84–89, June 1988.

A. Ghosh, S. Devadas, and A. Newton, “Test generation for highly sequential circuits,”Proc. IEEE Int. Conf. on Computer-Aided Design, pp. 362–365, November 1989.

T. Niermann and J. Patel, “Hitec: A test generation package for sequential circuits,”Proc. IEEE European Design Automation Conference, pp. 214–218, February 1991.

B. Krishnamurthy, “Hierarchical test generation: Can AI help?”,Proc. Int. Test Conference, pp. 694–700, September 1987.

H. Hofestadt and M. Gerner, “Qualitative testability analysis and hierarchical test pattern generation a new approach to design for testability?,”Proc. Int. Test Conference, pp. 538–546, September 1987.

S. Chandra and J. Patel, “A hierarchical approach to test vector generation,”Proc. 24th Design Automation Conference, pp. 495–501, June 1987.

T. Sarfert, R. Markgraf, E. Trischler, and M. Schulz, “Hierarchical test pattern generation based on high-level primitives,”Proc. Int. Test Conference, pp. 470–479, September 1989.

J. Calhoun and F. Brglez, “A framework and method for hierarchical test generation,”Proc. Int. Test Conference, pp. 480–490, September 1989.

R. Kunda, P. Narain, J. Abraham, and B. Rathi, “Speedup of test generation using high-level primitives,”Proc. 27th ACM/IEEE Design Automation Conference, pp. 594–599, June 1990.

A. Ghosh, S. Devadas, and A. Newton, “Sequential test generation at the register-transfer and logic levels,”Proc. 27th ACM/IEEE Design Automation Conference, pp. 580–586, June 1990.

B. Murray and J. Hayes, “Hierarchical test generation using precomputed tests for modules,”Proc. Int. Test Conference, pp. 221–229, September 1988.

P. Anirudhan and P. Menon, “Symbolic test generation for hierarchically modeled digital systems,”Proc. Int. Test Conference, pp. 461–469, September 1989.

K. Roy and J. Abraham, “High level test generation using data flow descriptions,”Proc. IEEE European Design Automation Conference, pp. 480–484, 1990.

C. Wu, “Test generation for high level synthesis circuits,” Master thesis, Dept. of Computer Science at University of Illinois, 1991.

C. Chen, C. Wu, and D.G. Saab, “Beta: Behavioral testability analysis,”Proc. IEEE Int. Conf. on Computer-Aided Design, pp. 202–205, November 1991.

J. Lee and J. Patel, “An architectural level test generator for a hierarchical design environment,”Proc. 21th Symposium on Fault-Tolerant Computing, pp. 44–51, June 1991.

J. Lee and J. Patel, “Artest: An architectural level test generator for data path faults and control faults,”Proc. Int. Test Conference, pp. 729–738, October 1991.

R. S. Varga,Matrix Iterative Analysis. Prentice-Hall, Englewood Cliffs, New Jersey, 1962.

L. H. Goldstein, “Controllability/observability analysis of digital circuits,”IEEE Trans. on Circuits and Systems, vol. CAS 26, pp. 685–693, September 1979.

J. White and A. L. Sangiovanni-Vincentelli,Relaxation Techniques for the Simulation of VLSI Circuits. Kluwer Academic Publishers, Norwell, Massachusetts, 1986.

R.A. Saleh, J.E. Kleckner, and A.R. Newton, “Iterated timing analysis and splicel,”Proc. IEEE Int. Conf. on Computer-Aided Design, November 1983.

The Am2910, A Complete 12-bit Microprogram Sequence Controller. Sunnyvale, California: Advanced Micro Devices, AMD Data Book, 1978.

T. Niermann, W. Cheng, and J. Patel, “Proofs: A fast memory efficient fault simulator for sequential circuits,”Proc. 27th Design Automation Conference, pp. 535–540, June 1990.

J. Lee and J. Patel, “Hierarchical test generation under intensive global functional constraints,”Proc. 29th ACM/IEEE Design Automation Conference, pp. 261–266, June 1992.

Author information

Authors and Affiliations

Additional information

This research was supported by the Semiconductor Research Corporation under Contract SRC 91-DP-109. A preliminary version of this paper appeared in ICCAD-91.

Rights and permissions

About this article

Cite this article

Lee, J., Patel, J.H. An architectural level test generator based on nonlinear equation solving. J Electron Test 4, 137–150 (1993). https://doi.org/10.1007/BF00971643

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00971643