Abstract

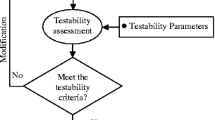

TIES is a knowledge based system that advises the ICs designer on the best modifications to perform on a circuit with testability problems, while satisfying design constraints defined by the user. The proposed approach differs from previous papers for three main reasons. The DfT techniques are applied only to critical areas of the circuit which are identified by means of a testability measure. A powerful description of design for testability techniques in the knowledge base is adopted. Moreover, a new decision scheme for the comparison among different implementations is proposed.

Similar content being viewed by others

References

M. Abramovici, M.A. Breuer, and A.D. Friedman,Digital System Testing and Testable Design, Computer Science Press, 1990.

Mentor Graphics,Autologic Optimization Guide v.8.1, 1992.

Racal-Redac,Silcsyn VHDL Synthesis User's Manual, 1993.

M.A. Breuer, R. Gupta, R. Gupta, K.J. Lee, and J.C. Lien, “Knowledge Based Systems for Test and Diagnosis,” inKnowledge Based Systems for Test and Diagnosis, G. Saucier, A. Ambler, M.A. Breuer eds., IFIP, North Holland, pp. 3–27, 1989.

P.W. Horstmann, “A Knowledge-Based System Using Design for Testability Rules,”Proc. 14th Fault Tolerant Computing Symposium, pp. 278–284, 1984.

K. Son, “Rule Based Testability Checker and Test Generator,”Proceedings International Test Conference, pp. 884–889, 1985.

P. Camurati, P. Gianoglio, R. Gianoglio, and P. Prinetto, “ESTA: An Expert System for DFT Rule Verification,”IEEE Transactions on Computer Aided Design, Vol 7, No. 11, pp. 1172–1179. Nov. 1988.

M.S. Abadir and M.A. Breuer, “A Knowledge Based System for Designing Testable VLSI Chips,”IEEE Design and Test of Computer, pp. 56–58, Aug. 1985.

M.A. Abadir, “TIGER: Testability Insertion Guidance Expert System,”Proceedings International Conference on Computer Aided Design, pp. 562–565, 1989.

I.D. Dear, C. Dislis, A.P. Ambler, and J. Dick, “Economic Effects in Design and Test,”IEEE Design & Test of Computer, Dec. 1991.

S. Bhawmik and P. Palchaudhuri, “An Expert System to Configure Global Design for Testability Structure in a VLSI Circuit,”Microprocessors and Microsystems, Vol. 13, No. 7, pp. 462–472, Sep. 1989.

S. Lin, C.A. Njinda, and M.A. Breuer, “A Systematic Approach for Designing Testable VLSI Circuits,”Proceedings International Conference on Computer Aided Design, pp. 496–499, 1991.

R. Gupta, R. Srinivasan, and m.A. Breuer, “Reorganizing Circuits to Aid Testability,”IEEE Design & Test of Computers, Sept. 1991.

S. Narayanan, C. Njinda, R. Gupta, and M. Breuer, “SIESTA: a Multi-Facet Scan Design System,”Proceedings International Test Conference, 1992.

D. Mukherjee, C. Njinda, and M.A. Breuer, “Synthesis of optimal 1-hot coded on-chip controllers for BIST hardware,”Proceedings International Conference on Computer Aided Design, pp. 236–239, April 1991.

I.C.H. Chen, C. Wu, and G. Saab, “BETA: Behavioral Testability Analysis,”Proceedings International Conference on Computer Aided Design, pp. 202–205, 1991.

M. Kraak and R.H.J.M. Otten, “Tackling Cost Optimization in Testable Design by Forward Inferencing,”IEEE Design & Test of Computers, pp. 252–257, Aug. 1992.

M. Bombana, G. Buonanno, P. Cavalloro, F. Ferrandi, D., Sciuto, and G. Zara, “ALADIN: A Multi-Level Testability Analyzer for VLSI System Design,”IEEE Transaction on VLSI Systems, Vol. 2, No. 2, pp. 157–171, 1994.

I.C.H. Chen, T. Karnik, and G. Saab, “Structural and Behavioral Synthesis for Testability Techniques,”IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, Vol. 13, No. 6, pp. 777–785, June 1994.

G. Buonanno, A. Burri, F. Fummi, and D. Sciuto, “An Approach to a Design for Testability Personal Consultant,” Journal of Microprocessing and Microprogramming No. 30,Proceeding Euromicro'90, Amsterdam, Aug. 1990.

Racal-Redac,Intelligen 2.0 Reference Manual, 1992.

“ESB-96 User Guide,” Simens Plessey Electronic System Limited, 1990.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Buonanno, G., Fummi, F. & Sciuto, D. TIES: A testability increase expert system for VLSI design. J Electron Test 6, 203–217 (1995). https://doi.org/10.1007/BF00993087

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00993087