Abstract

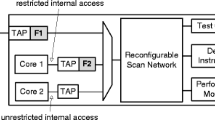

Register-transfer level designs that are derived from high-level synthesis systems generally consist of functional blocks and registers that are interconnected by multiplexers and buses to maximize resource sharing These multiplexer and bus structures have the unique ability to behave asswitches, i.e., to logically partition the circuit when their control inputs are manipulated in different ways. The presence of switches, the selection of scan registers can be influenced. This leads to an efficient partial scan methodology presented in this paper. Second, switches help set up data transfer paths calledI-paths. By employingI-paths to transport test data, the functional logic in the circuit can be separated from the switching logic for the purpose of test generation. This can lead to a reduction in test generation costs for a partial scan design. Thus the techniques presented in this paper help to minimize both testability overhead and test generation cost in bus-based circuits. This methodology is implemented in the SIESTA system for serial scan design.

Similar content being viewed by others

References

E.B. Eichelberger and T.W. Williams, “A logic design structure for LSI testability,”Proceedings 14th Design Automation Conference, pp. 462–467, June 1977.

M.J.Y. Williams and J.B. Angell, “Enhancing testability of LSI circuits via test points and additional logic,”IEEE Transactions on Computers, Vol. C-22, pp. 46–60, 1973.

J.H. Stewart, “Future testing of large LSI circuit cards,”Digest of Papers, IEEE Semiconductor Test Conference, pp. 6–15, October 1977.

S. Funatsu, N. Wakatsuki, and A. Yamada, “Designing digital circuits with easily testable consideration,”Digest of Papers, IEEE Semiconductor Test Conference, pp. 98–102, 1978.

M. Abramovici, M.A. Breuer, and A.D. Friedman,Digital Systems Testing and Testable Design. W.H. Freeman & Co., New York, 1990.

E. Trischler, “Design for testability using incomplete scan path and testability analysis,”Siemens Forsch.-u. Entwickl.-Ber., Vol. 13, No. 2, pp. 56–61, 1984.

H.-K.T. Ma, S. Devadas, A.R. Newton, and A. Sangiovanni-Vincentelli, “An incomplete scan design approach to test generation for sequential machines,”Proceedings IEEE International Test Conference, pp. 730–734, September 1988.

K.-T. Cheng and V.D. Agrawal, “An economical scan design for sequential logic test generation,”Proceedings Fault-Tolerant Computing Symposium (FTCS-19), pp. 28–35, June 1989.

R. Gupta, R. Gupta, and M.A. Breuer, “BALLAST: A methodology for partial scan design,” InProceedings Fault-Tolerant Computing Symposium (FTCS-19), pp. 118–125, June 1989.

A. Kunzmann. “Produktionstest synchroner Schaltwerke auf der Basis von Pipelinestrukturen,”Proceedings 18 Jahrestagung der Gesellschaft für Informatik, Hamburg, Informatik-Fachberichte 188, Springer-Verlag, pp. 92–105, 1988.

V. Chickermane and J.H. Patel, “An optimization based approach to the partial scan design problem,”Proceedings IEEE International Test Conference, pp. 377–386, September 1990.

R. Woudsma, F.P.M. Beenker, J.L. van Meerbergen, and C. Niessen, “PIRAMID: An architecture-driven silicon compiler for complex DSP applications,”Proceeding International Symposium on Circuits and Systems, pp. 2596–2600, May 1990.

R. Gupta, R. Gupta, and M.A. Breuer, “The BALLAST methodology for structured partial scan design,”IEEE Transactions on Computers, Vol. 39, No. 4, pp. 538–543, April 1990.

R. Gupta,Advanced Serial Scan Design for Testability, Ph.D. thesis, University of Southern California, Department of Electrical Engineering-Systems, 1991.

D.H. Lee and S.M. Reddy, “On determining scan flip-flops in partial scan designs,”Proceedings IEEE International Conference on Computer-Aided Design, pp. 322–325, November 1990.

S. Narayananan, C.A. Njinda, R. Gupta, and M.A. Breuer, “A multi-facet scan design system,”Proceedings, European Design Automation Conference, pp. 246–251, September 1992.

M.S. Abadir and M.A. Breuer, “A knowledge-based system for designing testable VLSI chips,”IEEE Design & Test of Computers, Vol. 2, No. 4, pp. 56–68, August 1985.

R. Gupta and M.A. Breuer, “Ordering storage elements in a single scan chain,”Proceedings International Conference on Computer-Aided Design, pp. 408–411, November 1991.

S. Narayanan, R. Gupta, and M.A. Breuer, “Optimal configuring of multiple scan chains,”IEEE Transactions on Computers, Vol. 42, No. 9, pp. 1121–1131, September 1993.

D. Ha,Automatic Test Pattern Generators and Fault Simulators for Combinational and Sequential Circuits, Technical Report, Virginia Polytechnic Institute, June 1992.

T.P. Kelsey, K.K. Saluja, and S.Y. Lee, “An efficient algorithm for sequential circuit test generation,”IEEE Transactions on Computers, Vol. 42, No. 11, pp. 1361–1371, November 1993.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Gupta, R., Breuer, M.A. Partial scan design of register-transfer level circuits. J Electron Test 7, 25–46 (1995). https://doi.org/10.1007/BF00993312

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00993312