Abstract

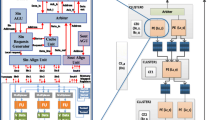

A processor with three concurrent and data-shared execution units is described in detail in this paper. The functionality, resources, and data sizes of the execution units, implemented with Xilinx FPGA chips, are user-configurable in order to best fit the application being run. A Harvard-type architecture allows a very large instruction word (128 bits) and, therefore, a real parallel utilization and control of resources. We also present the results of the implementation of two applications, the game of Life and the Abingdon Cross benchmark.

Similar content being viewed by others

References

Actel. 1994.FPGA Data Book and Design Guide. Actel Corp., Sunnyvale, Calif.

Altera. 1993.Data Book. Altera Corp., San Jose, Calif.

Arnold, J.M., Buell, D.A., and Davis, E.G. 1992. Splash 2. InProc., 4th Annual ACM Symp. on Parallel Algorithms and Architectures, pp. 316–322.

Athanas, P., and Silverman, H. 1993. Processor reconfiguration through instruction-set metamorphosis: Architecture and compiler.IEEE Comp., 26, 3: 11–18.

Berlekamp, E.R., Conway, J.H., and Guy, R.K. 1982.Winning Ways, vol. 2. Academic Press, London.

Bertin, P., Roncin, D., and Vuillemin, J. 1989. Introduction to programmable active memories. Tech. Rept. 3, DEC Paris Research Laboratory.

Cychosz, J.M. 1994. Efficient binary image thinning using neighborhood maps. InGraphics Gems IV (P. Heckbert, ed.), Academic Press, London.

Feldman, J.M., and Retter, C.T. 1994.Computer Architecture: A Designer's Text Based on a Generic RISC. McGrawHill, New York.

Guo, Z., and Hall, R.W. 1989. Parallel thinning with two-subiteration algorithms.CACM, 32, 3: 359–373.

Habib, S., ed. 1988.Microprogramming and Firmware Engineering Methods. Van Nostrand, New York.

IDT. 1992.Specialized Memories and Modules. Integrated Device Technology, Santa Clara, Calif.

Motorola. 1985.VMEbus Specification Manual, Revision C. Motorola.

Patterson, D.A., and Hennessy, J.L. 1994.Computer Organization & Design, The Hardware/Software Interface. Morgan Kaufmann, San Mateo, Calif.

Preston, K., Jr. 1989. The Abingdon Cross benchmark survey.IEEE Comp., 22, 7: 9–18.

Preston, K., Jr., and Duff, M.J.B. 1984.Modem Cellular Automata. Plenum Press, New York.

Rau, B.R., and Fisher, J.A. 1993. Instruction-level parallelism: History, overview, and perspectives. InInstruction Level Parallelism (B.R. Rau and J.A. Fisher, eds.), Kluwer Academic, Boston, pp. 9–50.

Sun Microsystems. 1987.The SPARC Architecture Manual. Sun Microsystems, Mountain View, Calif.

Toffoli, T., and Margolus, N. 1987.Cellular Automata Machines. The MIT Press, Cambridge, Mass.

Trimberger, S.M. 1994.Field-Programmable Gate Array Technology. Kluwer Academic, Boston.

Xilinx. 1991.The XACT4000 Design Implementation Reference Guide. Xilinx, San Jose, Calif.

Xilinx. 1993.The Programmable Logic Data Book. Xilinx, San Jose, Calif.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Iseli, C., Sanchez, E. Spyder: A SURE (SUperscalar and REconfigurable) processor. J Supercomput 9, 231–252 (1995). https://doi.org/10.1007/BF01212870

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/BF01212870