Abstract

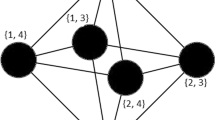

Line justification is a basic factor in affecting the efficiency of algorithms for test generation. The existence of reconvergent fanouts in the circuit under test results in backtracks in the process of line justification. In order to reduce the number of backtracks and shorten the processing time between backtracks, we present a new algorithm called DLJ (dynamic line justification) in which two techniques are employed.1. A cost function called “FOCOST” is proposed as heuristic information to represent the cost of justifying a certain line. When the relations among the lines being justified are “and”, the line having the highest FOCOST should be chosen. When the relations are “or”, the line having the lowest FOCOST should be chosen. The computing of the FOCOST of lines is very simple. 2. Disjoint justification cubes dynamically generated to perform backtracks make the backtrack number of the algorithm minimal. When the backtrace with cubeC 1 does not yield a solution, the next cube to be chosen isC 2 ′=C 2−{C 1,C 2}. Experimental results demonstrate that the combination of the two techniques effectively reduces the backtracks and accelerates the test generation.

Similar content being viewed by others

References

E. B. Eichelberger and T. W. Williams, A Logic Design Structure for LSI Testing. in Proc. 14th DAC, June 1977, 462–468.

S. Funatsu, N. Wakatsuki and T. Arima, Test Generation Systems in Japan. in Proc. 12th of DAC, June 1975, 114–122.

Zhu Chang-xian, The priority and testability of testing data for digital computing systems.Chinese Journal of Electronic Computing Technology, 1978, (1), 114–122 (in Chinese).

P. G. Kovijanic, Single Testability Figure of Merit. ITC. 1981, 521–529.

M. Abramoviciet al., Test Generation in LAMP 2: Concept and Algorithms, ITC. 1984, 49–56.

J. C. Wang and D. Z. Wei, A New Testability Measure for Digital Circuits. ITC, 1986, 506–512.

D. Z. Wei, An Algorithm for Test Pattern Generation of Functional Block Level Digital Circuits: The Principal Path Sensitization Method.Chinese Journal of Computers, 1982, 5 (2), 125–139 (in Chinese).

S. J. Chandra and J. H. Patel, Experimental Evaluation of Testability Measures for Test Generation.IEEE Trans. on CAD, 1989, 8 (1), 93–97.

R. S. Wei, New Front-End Line Justification Algorithm for Automatic Test Generation. ITC, 1986, 121–128.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Chen, Q., Wei, D. DLJ: A dynamic line-justification algorithm for test generation. J. of Comput. Sci. & Technol. 8, 87–91 (1993). https://doi.org/10.1007/BF02946589

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF02946589