# **Model Checking Transactional Memories**

Rachid Guerraoui Thomas A. Henzinger Barbara Jobstmann Vasu Singh

EPFL, Switzerland

#### **Abstract**

Model checking software transactional memories (STMs) is difficult because of the unbounded number, length, and delay of concurrent transactions and the unbounded size of the memory. We show that, under certain conditions, the verification problem can be reduced to a finite-state problem and we illustrate the use of the method by proving the correctness of several STMs, including two-phase locking, DSTM, TL2, and optimistic concurrency control. The safety properties we consider include strict serializability and abort consistency; the liveness properties include obstruction freedom, livelock freedom, and wait freedom.

Our main contribution lies in the structure of the proofs, which are largely automated and not restricted to the STMs mentioned above. In a first step we show that every STM that enjoys certain symmetry properties either violates a safety or liveness requirement on some program with 2 threads and 2 shared variables, or satisfies the requirement on all programs. In the second step we use a model checker to prove the requirement for the STM applied to a most general program with 2 threads and 2 variables. In the safety case, the model checker constructs a simulation relation between two carefully constructed finite-state transition systems, one representing the given STM applied to a most general program, and the other representing a most liberal STM applied to the same program. In the liveness case, the model checker analyzes fairness conditions on the given STM transition system.

## 1. Introduction

With the advent of multi-core processors, there is a new urgency for concurrent programming models that give the programmer the illusion of sequentiality and the compiler maximal flexibility. A model that has enjoyed particular recent success is software transactional memory (STM), which allows the programmer to think in coarse-grained code blocks that appear to be executed atomically but does not constrain the compiler by blocking memory access. Inspired by how databases manage concurrency, transactional memory was first introduced by Herlihy and Moss [HM93] in multi-processor design. Later Shavit and Touitou [ST95] introduced STM, a software-based variant of the concept, which enables a new way of looking at concurrent programming. An extensive overview of STM can be found in [LR07]. In this paper, we consider the following STM algorithms: two-phase locking, DSTM [HLMS03], TL2 [DSS06], and optimistic concurrency control [KR81].

Precisely because it encapsulates the difficulty of handling concurrency, the potential of subtle errors in STM implementations is enormous. This makes STM a ripe and important proving ground for formal verification. While there have been initial steps in this direction, the challenge remains daunting for several reasons.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

PLDI '08

Copyright © 2008 ACM [to be supplied]...\$5.00

First, there is no generally agreed upon formal notion of correctness for STM. Scott[Sco06] was the first to provide a formal semantics of STM. However, his weakest correctness criterion requires commit ordering to be preserved. Thus, the popular STM implementation TL2 [DSS06], which does not preserve the commit ordering, falls outside the semantic classification by Scott. Guerraoui and Kapalka [GK08] discussed various alternatives to precisely capture the safety aspect of STM and highlighted the subtle differences with database transactions.

Second, while model checking is the verification technique that is best equipped to find concurrency bugs, model checking is severely handicapped by several sources of unbounded state in STM: memory size, thread count, and transaction length cannot be bounded, and neither can the delay until a transaction commits nor the number of times that a transaction aborts. As with relaxed memory models, special care is needed in formulating a verification problem that is both relevant and solvable, as some problems about sequentializing concurrent systems are undecidable [AMP00].

Third, the specification of an STM universally quantifies over all possible application programs, requiring the desired safety and liveness conditions for all programs that are executed on the STM. In this sense, STM verification resembles the problem of checking that a processor implements an instruction set architecture, where the executed programs are also universally quantified. In both cases, the key is to define (and check) a suitable implementation relation [JD94]. While in processor verification, the implementation relation needs to handle pipelines and out-of-order execution, in STM, we need to handle aborted transactions.

We present in this paper a new technique for verifying STM safety and liveness properties. Our technique addresses the three issues above as follows.

First, the safety requirements we consider are strict serializability [Pap79] and abort consistency. (The latter is a single version read/write restriction of the notion of opacity introduced in [GK08].) Strict serializability preserves the order of conflicting operations by transactions, and the order of non-overlapping transactions. Abort consistency ensures, in addition, that aborting transactions do not see an inconsistent state of the memory, which can be disastrous in STMs (due to infinite loops, or exceptions). We study abort consistency, because it provides the programmer with the full sequentiality illusion and, to our knowledge, is satisfied by most STM protocols that claim that illusion [LR07]. Strict serializability is considered here for pedagogical reasons, as it is intuitive and captures the main technical difficulties behind verifying abort consistency. Our verification technique can be extended to the stronger notions of safety discussed by Scott [Sco06] by modifying the semantics of conflict. The liveness requirements we consider are the standard notions of obstruction freedom, livelock freedom, and wait freedom [HLM03, AKH03, Her91].

Second, we exploit the symmetries that are inherent in STM implementations to reduce the unbounded STM state verification to a problem that involves only a small number of threads and shared variables. Specifically, we show that every STM that enjoys certain symmetry properties either violates any of the considered safety and liveness requirements on some program with 2 threads and 2 shared variables, or satisfies the requirement on all programs. The symmetry properties, which expect all threads to be treated equally, are fulfilled by most transactional algorithms, including for in-

stance two-phase locking, DSTM, TL2, and optimistic concurrency control. Similar techniques for reducing unbounded instances of model-checking tasks to small, characteristic instances have been used for verifying protocols with an unbounded number of identical processes [BCG89] and cache-coherence protocols [HQR99].

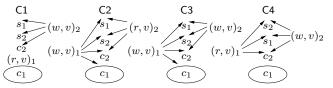

Third, and perhaps most importantly, we define two finite-state transition systems that generate exactly the strictly serializable (resp. abort consistent) executions of programs with 2 threads and 2 shared variables. These transition systems can be viewed as most liberal reference STM implementations guaranteeing strict serializability (resp. abort consistency). To our knowledge, the transition systems presented in this paper provide the first finite-state representation of the language of strictly serializable (resp. abort consistent) executions for transactions that may abort. The finite size of the transition systems is achieved by a careful choice of state, which encompasses for every thread a set of read variables (at most 2), a set of written variables (at most 2), a set of variables not allowed to be read (at most 2), a set of variables not allowed to be written (at most 2), and a set of threads with overlapping, preceding transactions (at most 1). We show that an STM implementation is strictly serializable (resp. abort consistent) iff for a specific, most general program with 2 threads and 2 variables, all executions are permitted by the reference STM implementation. Then, instead of checking language containment between a given STM implementation and the reference implementation, we check for the existence of a simulation relation between both transition systems. (The existence of a simulation relation is a commonly used, efficient sufficient condition for language containment.)

Putting all steps together, we reduce the problem of verifying the safety of an STM implementation, which is unbounded in many dimensions (memory size, thread count, transaction delay, etc.), to a simulation check between two finite-state systems. For two-phase locking, DSTM, TL2, and optimistic concurrency control, we obtain transition systems with up to 4,500 states, and a reference implementation has about 12,500 states. We implemented a simulation checker that automatically verifies strict serializability for optimistic concurrency control and abort consistency for two-phase locking, DSTM, and TL2 in less than 15 minutes. It should be noted that the methodology is applicable to any other STM implementations that fulfill the symmetry properties. Our simulation checker finds that correctness is not self-evident in many STM implementations. To illustrate this, we give an example where reversing two steps in TL2 renders the STM unsafe. In this case, the simulation check provides as counterexample an execution that is not strictly serializable (and thus not abort consistent). We therefore expect our verification tool to be useful to STM designers when they develop or modify STM implementations. Our tool also allows the comparison of different STMs according to whether one allows strictly more executions than another.

On the liveness side, we use again symmetry reduction theorems to check the desired liveness requirement on the finite-state transition system that results from a given STM implementation applied to a most general program with 2 threads and 2 variables. We extend our model checking tool to verify the different liveness properties. In the case of obstruction freedom, this amounts to checking a Streett condition and the check goes through for DSTM. For two-phase locking, TL2, and optimistic concurrency control, the model checker automatically generates counterexamples to obstruction freedom, as it does for DSTM and livelock freedom.

# 2. Safety in transactional memories

We introduce some notions to define the correctness of a TM. Let V be a set  $\{1,\ldots,k\}$  of k variables. Let  $C=\{\text{commit}\}\cup\{\text{read}\times V\}\cup\{\text{write}\times V\}$  be the set of commands on the variables V. Let  $T=\{1,\ldots,n\}$  be the set of threads. Let  $S=C\times T$  be the set of

statements. We define  $\hat{C} = C \cup \{\text{abort}\}$  and  $\hat{S} = \hat{C} \times T$ . A word  $w \in \hat{S}^*$  is a finite sequence of statements. Given a word  $w \in \hat{S}^*$ , we define the projection  $w|_t$  of w on thread  $t \in T$  as the longest subsequence w' of w such that every statement in w' is in  $\hat{C} \times \{t\}$ . Given a projection  $w|_t = s_0 s_1 \dots s_m$  of a word w, a statement  $s_i$  is finishing in  $w|_t$  if it is a commit or an abort or the last statement of  $w|_t$ . A statement  $s_i$  is initiating in  $w|_t$  if it is the first statement in  $w|_t$ , or the previous statement  $s_{i-1}$  is a finishing statement.

Given a projection  $w|_t$  of a word w on thread t, a consecutive subsequence  $x=s_0\dots s_m$  of  $w|_t$  is a transaction of thread t in w if  $s_0$  is initiating in  $w|_t$  and  $s_m$  is finishing in  $w|_t$ , and no other statement in x is finishing in  $w|_t$ . The transaction x is committing in w if  $s_m$  is a commit statement. The transaction x is aborting in w if  $s_m$  is an abort statement. Otherwise, the transaction x is pending in w. Given a word w and two transactions x and y in w (possibly of different threads), we say that x precedes y in w, written as  $x <_w y$ , if the finishing statement of x occurs before the initiating statement of y in w. A word w is sequential if for every pair (x,y) of transactions in w, either  $x <_w y$  or  $y <_w x$ .

We define a function  $com: \hat{S}^* \to S^*$  such that for all words  $w \in \hat{S}^*$ , the word com(w) is the longest subsequence w' of w such that every statement in w' is part of a committing transaction in w. Thus, com(w) consists of all statements of all committing transactions in w.

A transaction x of a thread t writes to a variable v if x contains a statement ((write, v), t). A statement s = ((read, v), t) in x is a global read of a variable v if there is no statement ((write, v), t) before s in the transaction x. A transaction x of a thread t globally reads a variable v if there exists a global read of variable v in transaction x. A word w is transaction equivalent to a word w' if for every thread  $t \in T$ , we have  $w|_t = w'|_t$ .

## 2.1 Safety criteria

Conflict serializability (cf. [EGLT76]) is a commonly used correctness criterion for concurrent systems and, in particular, for transactional systems. Conflict serializability allows us to omit the values of read and write commands, since the consistency of the values follows from preserving the order of conflicts. In the context of transactional memories, a stronger property, called strict serializability, is considered. Strict serializability preserves the order of non-overlapping transactions. We note that strict serializability does not state any restrictions on the operations of the aborting transactions. In the scope of STMs, a stronger notion of correctness, referred to as *abort consistency* has been suggested [GK08, HLMS03] to avoid unexpected side effects, like infinite loops, or array bound violations. Abort consistency requires that a word is strictly serializabile, and that the aborting transactions do not see read inconsistent values.

Now, we formalize these correctness criteria. We start with the notion of a conflict. Transactional memories use direct update semantics (every transaction modifies the shared variables in place and restores them upon abort), or deferred update semantics (every transaction modifies a local copy, and changes the shared copy upon a commit). We choose to define conflicts under the deferred update semantics. All our work can be similarly applied to TMs with direct update semantics, with a slight modification of definition of conflict. A statements  $s_1$  of transaction x and a statement  $s_2$  of transaction x and a statement x of transaction x and x and x are both commits, and x and x writes to x, or (ii) x and x are both commits, and x and x write to x.

A word  $w = s_0 \dots s_n$  is *conflict equivalent* to a word w' if (i) w is transaction equivalent to w', and (ii) for every pair  $s_i, s_j$  of statements in w, if  $s_i$  and  $s_j$  conflict and i < j, then  $s_i$  occurs before  $s_j$  in w'. A word  $w = s_0 \dots s_m$  is *strictly equivalent* to a

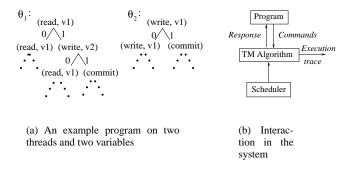

Figure 1. Our framework of transactional memory

word w' if (i) w is conflict equivalent to w' and (ii) for every pair x, y of transactions in w, if  $x <_w y$  then  $x <_{w'} y$ .

A word  $w \in \hat{S}^*$  is *strictly serializable* if there exists a sequential word w' such that w' is strictly equivalent to com(w). Furthermore, we define that a word w is *abort consistent* if there exists a sequential word w' such that w' is strictly equivalent to w. (Note that w may contain pending transactions.) We note that given a word w, if w is abort consistent, then w is strictly serializable.

**Example.** Consider  $w = ((\text{read}, v_1), t_1), ((\text{write}, v_1), t_2), ((\text{write}, v_2), t_2), (commit, t_2), ((\text{read}, v_2), t_1). w has two transactions: (i) a pending transaction (((\text{read}, v_1), t_1), (((\text{read}, v_2), t_1), \text{ and (ii) a committing transaction (((\text{write}, v_1), t_2), ((\text{write}, v_2), t_2), (\text{commit}, t_2). The following pairs of statements conflict: ((((\text{read}, v_1), t_1), (\text{commit}, t_2)) and ((((\text{read}, v_2), t_1), (\text{commit}, t_2)). The word w is strictly serializable because <math>com(w)$  consists only of ((write,  $v_1$ ),  $t_2$ ), ((write,  $v_2$ ),  $t_2$ ), and (commit,  $t_2$ ). On the other hand, w is not abort consistent since  $t_1$  reads the old value of  $v_1$  (before  $t_2$  commits) and the new value of  $v_2$  (committed by  $t_2$ ).

#### 2.2 Transactional memories

We consider a thread as our basic sequential unit of computation, and describe a program to be a collection of threads. Each thread consists of a sequence of transactions. In our formalism, we allow programs to retry a transaction, or start another transaction on an abort. Formally, an *unrolled thread*  $\theta$  on C is a function  $\theta: \mathbb{B}^* \to C$ . We write  $\Theta$  for the set of unrolled threads. Defining unrolled threads as infinite binary trees on commands makes the representation independent of specific control flow statements, such as exceptions for handling abort. For every command of the thread, we define two successor commands, one if the command is successfully executed, and another if the command fails due to an abort of the transaction.

Note that this definition allows us to capture easily different retry mechanisms of TMs, e.g., retry the same transaction until it succeeds or try other transaction after an abort. We define a program p on n threads and k variables as an n-tuple  $p = \langle \theta^1, \ldots, \theta^n \rangle$  of unrolled threads on C. Figure 1(a) shows an example program on two threads and two variables. Let  $P^{n,k}$  be the set of all programs on n threads and k variables. Let P be the set of all programs.

We define a transactional memory as an abstract function that takes as input a program, and produces a set of infinite words. Formally, a transactional memory is a function  $M:P\to 2^{\hat{S}^\omega}$ . A transactional memory M ensures strict serializability for all programs with n threads and k variables if for every program  $p\in P^{n,k}$ , for every word  $w\in M(p)$ , all finite prefixes of w are strictly serializable. Similarly, M ensures abort consistency for all programs with n threads and k variables if for every program  $p\in P^{n,k}$ , for every word  $w\in M(p)$ , all finite prefixes of w are abort consistent. We say that a transactional memory M

ensures strict serializability (resp. abort consistency) if it ensures strict serializability (resp. abort consistency) for all programs with arbitrary number n of threads and arbitrary number k of variables.

## 3. Transactional memory algorithms

We use state transition systems to define TMs. A TM algorithm is a family of TM transition systems, one for n threads and k variables, for every n and k. The TM transition system consists of a set of states, an initial state, a transition relation between the states, and an extended set of commands depending on the underlying TM. For example, a given TM may require that a thread locks a variable before writing to the variable, or that a thread validates the variables read in a transaction, before accessing a new variable.

A TM algorithm interacts with a program and a scheduler (see Fig. 1(b)). The scheduler chooses a thread and determines the next command of that thread to be executed. The TM transition system decides whether the command can be executed in a single atomic step, or in several atomic steps, or has to be aborted. Given a program, a scheduler, and a TM transition system, we get an execution trace. Projecting this trace to the set  $\hat{C}$  of commands, we get a word in  $\hat{S}^*$ . We describe the language of a TM transition system as the set of words on  $\hat{S}^*$  that it can produce.

Formally, a scheduler  $\sigma$  on T is a function  $\sigma: \mathbb{N} \to T$ . Let  $\Sigma$  be the set of schedulers. We define a  $\mathit{TM}$  algorithm A as a family of  $\mathit{TM}$  transition systems  $A^{n,k} = \langle Q, q_{init}, D, \delta \rangle$  for each n and k, where Q is a set of states,  $q_{init}$  is the initial state, D is the set of extended commands with  $C \subseteq D$ , and  $\delta \subseteq Q \times C \times \hat{S}_D \times Resp \times Q$  is the deterministic or non deterministic transition relation, where  $\hat{S}_D = (D \cup \{\text{abort}\}) \times T$  and  $Resp = \{0, 1, \bot\}$ . The transition relation  $\delta$  obeys the following rules:

- **1.** if there exists a transition  $(q,c,(d,t),r,q_1) \in \delta$  of thread t to state  $q_1 \in Q$  such that  $r = \bot$ , then for every transition  $(q_1,c_1,(d_1,t_1),r_1,q_2) \in \delta$  with  $t_1=t$ , we have  $c_1=c$ . In this case, we say that only command  $c_1$  is *enabled* in  $q_1$  for thread t.

- **2.** if for all transitions  $(q, c, (d, t), r, q_1) \in \delta$  of thread t to state  $q_1 \in Q$ ,  $r \neq \bot$  holds then there exists for every command  $c_1 \in C$  a transition  $(q_1, c_1, (d_1, t), r_1, q_2) \in \delta$ . In this case, we say that every command  $c_1 \in C$  is *enabled* in  $q_1$  for thread t.

- **3.** for all  $q\in Q$  and for all transitions  $(q,c,(d,t),r,q_1)\in \delta$  such that d= abort, we have r=0.

- **4.** for all  $q \in Q$  and  $(c,t) \in S$ , if c is not enabled in q for thread t then there exists a transition  $(q,c,(d,t),r,q_1) \in \delta$  with d= abort for some  $q_1 \in Q$ . In this case, we say that the command c is abort enabled in the state q for thread t.

Moreover, for a deterministic transition relation  $\delta$ , we have for all  $q \in Q$  and  $(c,t) \in S$ , if  $(q,c,(d_1,t),r_1,q_1) \in \delta$  and  $(q,c,(d_2,t),r_2,q_2) \in \delta$  then  $d_1=d_2,\,q_1=q_2,$  and  $r_1=r_2.$  Unless otherwise stated, TM transition systems have deterministic transition relations.

Let  $p = \langle \theta^1, \dots, \theta^n \rangle$  be a program in  $P^{n,k}$ . Let  $\sigma$  be a scheduler on n threads. A  $run \ \rho = \langle q_0, l_0 \rangle \langle q_1, l_1 \rangle \dots$  of  $A^{n,k}$  with scheduler  $\sigma$  on program p is an infinite sequence of states together with program locations, where  $l_j = \langle l_j^1, \dots, l_j^n \rangle \in (\mathbb{B}^*)^n$  for all  $j \geq 0$  and (i)  $q_0 = q_{init}$  and  $l_0 = \langle \epsilon, \dots, \epsilon \rangle$ , (ii) for all  $j \geq 0$  there exists a transition  $(q_j, c_j, (d_j, t_j), r_j, q_{j+1}) \in \delta$  such that  $t_j = \sigma(j)$  and  $c_j = \theta^{t_j}(l_j^{t_j})$  and for all  $t \in T$  if  $t \neq t_j$  or  $r_j = \bot$  then  $l_{j+1}^t = l_j^t$ , otherwise  $l_{j+1}^t = l_j^t \cdot r_j$ . We associate with  $\rho$  an execution trace  $s_0s_1 \dots$  in  $\hat{S}_D^\omega$  such that  $s_j = (d_j, t_j)$  for all  $j \geq 0$ . We define the language  $L(A^{n,k})$  of  $A^{n,k}$  as the set of all finite words  $w \in \hat{S}^*$  such that  $w = e|_{\hat{S}}$ , where e is a finite prefix of an execution trace of  $A^{n,k}$  for some program p on n threads and k variables, and some scheduler  $\sigma$  on n threads.

A TM algorithm A defines a transactional memory M such that for all n,k, for every program p in  $P^{n,k}$  and every word  $w \in \hat{S}^{\omega}$ , we have  $w \in M(p)$  iff there exists a scheduler  $\sigma$  on T such that  $w = e|_{\hat{S}}$ , where e is the execution trace of p and  $\sigma$  on the TM algorithm A. It follows that a TM M defined by a TM algorithm A ensures strict serializability (abort consistency) for all programs with n threads and k variables iff all words in  $L(A^{n,k})$  are strictly serializable (abort consistent).

In the following sections, we describe different transactional memories as TM algorithms. To simplify the description, we view a state q of the corresponding TM transition systems as an n-tuple  $\langle q^1 \dots q^n \rangle$ , where each component  $q^t$  corresponds to a thread t and is called *thread state* of t.

#### 3.1 The sequential TM

To keep our first example simple, we describe a sequential TM. The sequential TM executes the transactions sequentially (as ideally suited for a uniprocessor). We define the sequential TM  $M_{seq}$  using a sequential TM algorithm  $A_{seq}$ . The sequential TM transition system  $A_{seq}^{n,k}$  for n threads and k variables is given by the tuple  $\langle Q, q_{init}, D, \delta \rangle$ . The thread state  $q^t$  of thread t is  $\{0, 1\}$ . The initial state  $q_{init} = \langle 0, \dots, 0 \rangle$ . The set of extended commands is D = C. A transition  $(q_1, c, (d, t), r, q_2)$  is in  $\delta$  if c is enabled in  $q_1$  for thread t and one of the following holds:

- **1. Read/Write.** (i)  $c \in \{\text{read}, \text{write}\} \times V$  and d = c and r = 1, and (ii)  $q_1^u = 0$  for all  $u \neq t$  and  $q_2^t = 1$ , and (iii)  $q_2^u = q_1^u$  for all  $u \neq t$  (When a thread reads or writes a variable, the state of all other threads should be false. The state of t is set to true.)

- **2. Commit.** (i) c= commit and d=c and r=1, and (ii)  $q_1^u=0$  for all  $u\neq t$ , and (iii)  $q_2^t=0$  and  $q_2^u=q_1^u$  for all  $u\neq t$  (When a thread t commits, the state of all other threads should be false. The state of t is set to false.)

A transition  $(q_1,c,(\mathsf{abort},t),0,q_2)$  is in  $\delta$  if c is abort enabled in  $q_1$  for thread t and  $q_2=q_1$ .

## 3.2 The two-phase locking TM

Our second example of a TM algorithm is based on two phase locking (2PL) protocol, commonly used in database transactions. Every transaction locks the variables it reads or writes before accessing them, and releases all the acquired locks during the commit. We define the 2PL TM  $M_{2PL}$  using a 2PL TM algorithm  $A_{2PL}$ . The 2PL TM transition system  $A_{2PL}^{n,k}$  for n threads and k variables is given by the tuple  $\langle Q, q_{init}, D, \delta \rangle$ . The thread state  $q^t$  of thread t is a subset of V. It denotes the variables locked by the thread. The initial state  $q_{init} = \langle \emptyset, \dots, \emptyset \rangle$ . The set of extended commands is  $D = C \cup (\{ \text{lock} \} \times V)$ .  $\delta$  is the transition relation such that  $(q_1, c, (d, t), r, q_2) \in \delta$  if c is enabled in  $q_1$  for thread t and one of the following holds:

- **1. Read/Write.** (i)  $c \in \{\text{read, write}\} \times \{v\}$  and d = c and r = 1, and (ii)  $v \in q_1^t$ , and (iii)  $q_2 = q_1$  (When a thread has to read or write v and it already holds a lock on v, the read or write is executed by the TM.)

- **2. Lock.** (i)  $c \in \{\text{read}, \text{write}\} \times \{v\}$  and d = (lock, v) and  $r = \bot$ , and (ii)  $v \notin q_1^t$  and for all  $u \neq t$ , we have  $v \notin q_1^u$ , and (iii)  $q_2^t = q_1^t \cup \{v\}$ , and (iv)  $q_2^u = q_1^u$  for all  $u \neq t$  (When a thread has to read or write v, and it does not hold a lock on v, the thread first locks v.)

- **3. Commit.** (i) c= commit and d=c and r=1, and (ii)  $q_2^t=\emptyset$ , and (iii)  $q_2^u=q_1^u$  for all threads  $u\neq t$  (When a thread commits, it releases all the locks.)

A transition  $(q_1, c, (\mathsf{abort}, t), 0, q_2)$  is in  $\delta$  if c is abort enabled in  $q_1$  for thread t and  $q_2^t = \emptyset$  and  $q_2^u = q_1^u$  for all threads  $u \neq t$ .

#### 3.3 The dynamic software transactional memory

Dynamic software TM (DSTM) [HLMS03] is one of the most popular STM algorithms. The algorithm exists in many flavors. In this work, we focus on one of them, called invisible read DSTM, where the transactions require ownership of variables only for writing. The reads are not visible to the writers. Upon reading, the transactions validate their read set. In our work, we ignore optimizations like early release possible in DSTM. Our TM transition system does not directly allow one thread to abort another thread. So, we allow a thread to set an abort flag for another thread and change the state of the aborted thread appropriately, and also, require that a thread aborts whenever the abort flag is set for the thread. We define the DSTM TM  $M_{dstm}$  using a DSTM TM algorithm  $A_{dstm}$ . The DSTM TM transition system  $A_{dstm}^{n,k}$  for n threads and k variables is given by  $\langle Q, q_{init}, D, \delta \rangle$ . A thread state  $q^t$  of thread t is defined as a 3-tuple  $\langle status^t, rs^t, os^t \rangle$ , where  $status^t \in \{\text{aborted}, \text{valid}, \text{valid},$ invalid} is the status of thread  $i, rs^t \subseteq V$  is the read set of thread i, and  $os^t \subseteq V$  is the ownership set of thread i. For every thread, the initial thread state of thread t is  $q_{init}^t = \langle \mathsf{valid}, \emptyset, \emptyset \rangle$ . The set of extended commands is  $D = C \cup (\{own\} \times V)$ . A transition  $(q_1, c, (d, t), r, q_2)$  is in  $\delta$  if c is enabled in  $q_1$  for thread t and one of the following holds:

- **1. Local read.** (i) c=(read,v) and d=c and r=1, and (ii)  $v\in os_1^t$  and  $status_1^t\neq \mathsf{aborted}$ , and (iii)  $q_2=q_1$  (When a thread read v such that the read is not global, nothing changes)

- **2. Global read.** (i) c=(read,v) and d=c and r=1, and (ii)  $v\notin os_1^t$  and  $status_1^t=\text{valid}$ , and (iii)  $rs_2^t=rs_2^t\cup\{v\}$ , and  $os_2^t=os_1^t$  and  $status_2^t=\text{valid}$ , and (iv)  $q_2^u=q_1^u$  for all threads  $u\neq t$  (When a thread reads v globally, the status of the thread should be valid and v is added to the read set of the thread)

- **3. Own.** (i) c = (write, v) and d = (own, v) and  $r = \bot$ , and (ii)  $status_1^t \neq \text{aborted}$ , and (iii)  $rs_2^t = rs_1^t$  and  $os_2^t = os_1^t \cup \{v\}$  and  $status_2^t = status_1^t$ , and (iv) for all threads  $u \neq t$  if  $v \in os_1^u$  then  $status_2^u = \text{aborted}$ , and  $os_2^u = \emptyset$ , and  $rs_2^u = \emptyset$ , otherwise  $status_2^u = status_1^u$ ,  $os_2^u = os_1^u$ , and  $rs_2^u = rs_1^u$ . (When a thread writes to v, it should first own v, the status should not be aborted, the variable v is added to the owned set of the thread. If v was owned by some other thread earlier, the status of that thread is aborted and its read and own sets are set to empty).

- **4. Write.** (i) c = (write, v) and d = c and r = 1, and (ii)  $status_1^t \neq \text{aborted}$  and  $v \in os_1^t$ , and (iii)  $q_2^u = q_1^u$  for all  $u \in T$  (A thread can write to v if the status is not aborted and the variable v is in the own set of the thread).

- **5. Commit.** (i) c = commit and d = c and r = 1, and (ii)  $status_1^t = \text{valid}$ , and (iii)  $os_2^t = \emptyset$ , and  $rs_2^t = \emptyset$ , and (iv) for all threads  $u \neq t$ ,  $rs_2^u = rs_1^u$ ,  $os_2^u = os_1^u$ , and  $status_2^u = \text{invalid}$  if  $rs_1^u \cup os_1^t \neq \emptyset$  and  $status_2^u = status_1^u$  otherwise. (A thread t commits if the status is valid. The own and read sets of the thread are set to empty. The status of threads whose read set intersects with the own set of t is set to invalid.)

A transition  $(q_1,c,(\mathsf{abort},t),0,q_2)$  is in  $\delta$  if the command c is abort enabled in  $q_1$  for thread t, and  $status_2^t = \mathsf{valid},$  and  $rs_2^t = \emptyset$  and  $os_2^t = \emptyset$ , and  $q_2^u = q_1^u$  for all threads  $u \neq t$ .

## 3.4 The TL2 transactional memory

Transactional locking 2 (TL2) [DSS06] is a TM which works as follows. First, a transaction reads and writes locally to the variables. After the transaction has locally completed, the thread acquires locks for the variables it writes to. Then, the transaction is validated using version numbers. If for all the variables in the read set, the version is consistent, and no other thread owns the variable, then the transaction is allowed to commit. We note that TL2 uses locks for synchronization and version control to check validation. A version number is maintained for every variable, which is incremented

when the variable is written. Every transaction reads the variable along with the version number. A transaction successfully commits if all the variables that it reads have the same version number at the time of commit. TL2 uses version control to validate the read set efficiently in a distributed setting. To model TL2 using a finite state TM transition system, we replace the version control by invalidation. When a transaction commits, it invalidates the transactions whose read set intersects with the transaction's write set.

We define the TL2 TM  $M_{TL2}$  using the TL2 TM algorithm as  $A_{TL2}$ . The TL2 TM transition system  $A_{TL2}^{r,k}$  for n threads and k variables is given by the tuple  $\langle Q, q_{init}, D, \delta \rangle$ . A thread state  $q^t$  of thread t in the TL2 algorithm is defined as a 4-tuple  $\langle status^t, rs^t, ws^t, ls^t \rangle$ , where  $status^t \in \{\text{valid, invalid, validated, commitrdy}\}$   $rs^t \subseteq V$  is the read set,  $ws^t \subseteq V$  is the write set, and  $ls \subseteq V$  is the lock set. The initial thread state  $q_{init}^t = \{\text{valid, }\emptyset,\emptyset,\emptyset\}$  for all threads  $t \in T$ . The set of extended commands is  $D = C \cup \{\{\text{lock}\} \times V\} \cup \{\text{validate, chklock}\}$ . We express the transition relation informally. The formal transition relation can be obtained, as in the previous examples. A transition on a command c for a thread t in state q occurs if c is enabled in the state q for thread t, where the command is one of the following:

- **1. Local read.** A thread can read v if the read is local.

- **2. Global read.** When a thread reads v and the read is global, the status of the thread should be valid, the lock set should be empty, and the variable v is added to the read set.

- **3. Lock.** When a thread commits, the thread first locks every variable in the write set. The status should be valid or invalid. No other thread should hold the lock on the variable, and the variable is added to the lock set of the thread.

- **4. Write.** When a thread writes to v, the status should be valid or invalid. The lock set of the thread should be empty. The variable v is added to the write set of the thread.

- **5. Validate.** When a thread has to commit, it validates the read set after acquiring the locks on all the variables in the write set. The status of the thread should be valid, and it is set to validated.

- **6. Chklock.** When a thread has to commit, after validating the read set, it is checked that the read set of the thread does not intersect with the lock set of any other thread. If so, the status is set to committed, and the thread can now successfully commit.

- **7. Commit.** When a thread has to commit, if the status is commitrdy, the thread commits.

A thread t aborts on a command c in state q if c is abort enabled in state q for thread t. The read set, lock set, and the write set are changed to empty, and the status is set to valid.

## 3.5 The optimistic concurrency control TM

We now discuss a common concurrency protocol used in databases. It was proposed by Kung et al. [KR81] and called optimisitic concurrency control (OCC). The OCC TM executes the transactions of the threads without any synchronization. Before committing, every transaction chooses a sequence number and validates its read set. Transactions commit in the order of sequence numbers.

We define the OCC TM  $M_{occ}$  using an OCC TM algorithm  $A_{occ}$ . We refer to the OCC TM transition system with n threads and k variables as  $A_{occ}^{n,k}$ . The formal definition of the transition system can be obtained from the original algorithm, as we did in the previous examples.

Table 1 shows execution traces and words for the example program in Figure 1(a) and different schedulers with every transaction memory described above.

## 4. Reduction theorems for safety

We present two reduction theorems, corresponding to strict serializability and abort consistency. These theorems state that if a TM ensures strict serializability (abort consistency) for all programs on

**Table 1.** Examples of execution traces and words in the language of different TM algorithms. Notation: r = read, w = write, c = commit, a = abort, l = lock, o = own, v = validate, cl = chklock, s = serialize. Command (c, t) is written as  $c_t$ .

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | (0,0) =                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------|

| TM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Scheduler<br>output | $1^{\mathrm{st}}$ trace: Execution trace $e$ $2^{\mathrm{nd}}$ trace: $w=e _{\hat{S}}$ in $L(A)$ |

| seq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11122               | $(r,1)_1, (w,2)_1, c_1, (w,1)_2, c_2 \dots  (r,1)_1, (w,2)_1, c_1, (w,1)_2, c_2$                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 112122              | $(r,1)_1, (w,2)_1, a_2, c_1, (w,1)_2, c_2 \dots  (r,1)_1, (w,2)_1, a_2, c_1, (w,1)_2, c_2$       |

| 2PL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 111112              | $(l,1)_1, (r,1)_1, (l,2)_1, (w,2)_1, c_1, (l,2)_2 \dots  (r,1)_1, (w,2)_1, c_1$                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1211112             | $(l,1)_1, a_2, (r,1)_1, (l,2)_1, (w,1)_1, c_1, (l,2)_2 \dots$                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | $a_2, (r, 1)_1, (w, 2)_1, c_1$                                                                   |

| dstm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1221112             | $(r,1)_1,(o,1)_2,(w,1)_2,(o,2)_1,(w,2)_1,c_2,c_1\ldots$                                          |

| asom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     | $(r,1)_1,(w,1)_2,(w,2)_1,c_2,c_1$                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1222111             | $(r,1)_1, (o,1)_2, (w,1)_2, c_2, (o_2)_1, (w,2)_1, a_1 \dots$                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | $(r,1)_1,(w,1)_2,c_2,(w,2)_1,a_1$                                                                |

| $(r,1)_1, (v,1)_2, (r,1)_3, (v,1)_4, (v,1)_5, ($ |                     | $(r,1)_1, (w,2)_1, (w,1)_2, (l,2)_1, v_1, cl_1,$                                                 |

| TL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 212                 | $(l,1)_2, v_2, cl_2, c_1, c_2 \dots$                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 212                 | $(r,1)_1,(w,2)_1,(w,1)_2,c_1,c_2$                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11212112            | $(r,1)_1,(w,2)_1,(w,1)_2,(l,2)_1,(l,1)_2,$                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22                  | $v_1, a_1, v_2, cl_2, c_2 \dots$                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22                  | $(r,1)_1,(w,2)_1,(w,1)_2,a_1,c_2$                                                                |

| occ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1211212             | $(r,1)_1,(w,1)_2,(w,2)_1,s_1,s_2,c_1,c_2\dots$                                                   |

| occ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | $(r,1)_1,(w,1)_2,(w,2)_1,c_1,c_2$                                                                |