# Optimal Online Multiprocessor Scheduling of Sporadic Real-Time Tasks is Impossible

Nathan Fisher Wayne State University Joël Goossens Université Libre de Bruxelles

Sanjoy Baruah The University of North Carolina at Chapel Hill

#### **Abstract**

Optimal online scheduling algorithms are known for sporadic task systems scheduled upon a single processor. Additionally, optimal online scheduling algorithms are also known for restricted subclasses of sporadic task systems upon an identical multiprocessor platform. The research reported in this article addresses the question of existence of optimal online multiprocessor scheduling algorithms for general sporadic task systems. Our main result is a proof of the impossibility of optimal online scheduling for sporadic task systems upon a system comprised of two or more processors. The result is shown by finding a sporadic task system that is feasible on a multiprocessor platform that cannot be correctly scheduled by any possible online, deterministic scheduling algorithm. Since the sporadic task model is a subclass of many more general real-time task models, the nonexistence of optimal scheduling algorithms for the sporadic task systems implies nonexistence for any model which generalizes the sporadic task model.

**Keywords:** Real-time scheduling; Multiprocessor systems; Sporadic task model; Optimal scheduling algorithms.

#### 1 Introduction

The sporadic task model [18, 16] has received tremendous research attention over the years for its usefulness in modeling recurring processes for hard-real-time systems. A sporadic task  $\tau_i = (e_i, d_i, p_i)$  is characterized by a worst-case execution requirement  $e_i$ , a (relative) deadline  $d_i$ , and a minimum inter-arrival separation  $p_i$ , which is, for historical reasons, also referred to as the period of the task. Such a sporadic task generates a potentially infinite sequence of jobs, with successive job-arrivals separated by at least  $p_i$  time units. Each job has a worst-case execution requirement equal to  $e_i$  and a deadline that occurs  $d_i$  time units after its arrival time. A sporadic task system  $\tau$  is a collection of such sporadic tasks.

Two significant factors contribute to the popularity of the sporadic task model in real-time system design. One factor is the generality of the sporadic task model. The sporadic task model is an extension of an earlier task model known as the Liu and Layland (LL) task model [17]. An LL task,  $\tau_i$ , is only specified by an worst-case execution requirement  $e_i$  and a period  $p_i$ . The relative deadline is implicit in the period parameter (i.e., a job of an LL task has absolute deadline  $p_i$  time units after its arrival). The sporadic task model is, thus, a generalization of the LL task model, and, in fact, LL tasks are a subclass of sporadic task systems sometimes referred to as implicit-deadline sporadic task systems. Other subclasses of sporadic task systems include constrained-deadline sporadic task systems where each task has  $d_i \leq p_i$  and arbitrary-deadline sporadic task systems where no constraint is imposed upon the relationship between a task's deadline and period.

The development of effective and efficient scheduling algorithms and associated analytical techniques for single processor systems is another factor in the sporadic task model's popularity. For instance, the earliest-deadline-first (EDF) scheduling algorithm is known to be *optimal* for arbitrary collections of independent jobs scheduled upon uniprocessor platforms [8]. This optimality result holds for both sporadic task systems and LL task systems on uniprocessors. The notion of optimality for real-time systems is explained in the following: a task system  $\tau$  is said to be *feasible* on a processing platform, if, for any legal job arrival sequence of  $\tau$ , there exists a schedule for  $\tau$  on the processing platform in which each job successfully completes execution by its deadline. For any task system  $\tau$  that is feasible on a given processing platform, an optimal scheduling algorithm is guaranteed to generate a schedule for  $\tau$  which meets all deadlines. In addition to the existence of optimal scheduling algorithms for sporadic task systems, exact, pseudo-polynomial-time techniques are known for determining whether a given sporadic task system is feasible upon a preemptive single processor platform [7]. Such techniques are known as *feasibility analysis*. A related analysis technique, known as *schedulability analysis*, determines whether a given scheduling algorithm will correctly schedule a task system to meet all deadlines on a processing platform. Relatively efficient, exact schedulability tests have been developed for various scheduling algorithms on uniprocessor platforms.

The success of the sporadic task model for real-time system design on single processor systems has motivated research on scheduling algorithms and feasibility/schedulability analysis for sporadic task systems upon multiprocessor platforms. Unfortunately, most results from uniprocessor scheduling of sporadic task systems do not trivially extend to the multiprocessor setting. For instance, it is known that EDF is a suboptimal scheduling algorithm for even LL tasks on multiprocessor platforms [10]. However, optimal scheduling approaches for LL task systems have been developed [13, 6, 20].

Since LL tasks are a subclass of sporadic task systems, the non-optimality result for EDF [10] extends trivially to sporadic task systems on multiprocessor platforms. The question that this article addresses is: *does there exist an algorithm which is guaranteed to successfully schedule any feasible sporadic task system on a multiprocessor platform*? In other words, does there exist optimal scheduling algorithms for sporadic task model? For LL task systems, the answer to that question is "yes," due to the existence of optimal scheduling approaches (referred to in the preceding paragraph). For arbitrary collections of independent jobs where job arrival-times are not known *a priori*, Hong and Leung [12] and Dertouzos and Mok [9], independently, showed that the answer is "no"; i.e., optimal online scheduling of arbitrary collections of independent jobs is impossible. In terms of generality, the sporadic task model lies between the LL task model (any LL task system is also a sporadic task system) and the

arbitrary collections of independent jobs setting (any collection of jobs generated by a sporadic task system is also a legal collection of independent jobs). As we will illustrate later in this article, the multiprocessor optimality result for LL task systems and the non-optimality result do not directly apply to the sporadic task systems. Thus, the above question cannot be answered by application of prior results.

The main contribution of this article answers the above open question in the negative: *optimal online multiprocessor scheduling of sporadic task systems is impossible*. We, in fact, show a slightly stronger result that optimal online multiprocessor scheduling of constrained-deadline sporadic task systems is impossible. The impossibility result for constrained-deadline sporadic task systems immediately implies that optimal online scheduling of any task model that generalizes the constrained-deadline sporadic task model is impossible, as well. Therefore, even a slight amount of generalization from the LL task model (the sporadic task model simply adds a relative deadline parameter to the task specification) causes the existence of optimal scheduling algorithms to disappear.

This article is organized as follows. Section 2 presents the formal models and notation that we use for describing real-time work, task systems, processing platforms, and scheduling algorithms, Section 3 illustrates (via examples) the inapplicability of prior multiprocessor optimality results to the multiprocessor scheduling of sporadic task systems. Section 4 proves that optimal online multiprocessor scheduling of sporadic and more general task systems is impossible. The proof given in Section 4 relies upon an example task system that is assumed to be feasible upon a multiprocessor platform; Section 5 proves that this example task system is, in fact, feasible.

#### 2 Model and Notation

#### 2.1 Real-Time Instances

Throughout this article, we will characterize a real-time job  $J_i$  by a three-tuple  $(A_i, E_i, D_i)$ : an arrival time  $A_i$ , an execution requirement  $E_i$ , and a relative deadline  $D_i$ . The interpretation of these parameters is that  $J_i$  arrives  $A_i$  time units after system start-time (assumed to be zero) and must execute for  $E_i$  time units over the time interval  $[A_i, A_i + D_i)$ .  $A_i$  is assumed to be a non-negative real number while both  $E_i$  and  $D_i$  are positive real numbers. The interval  $[A_i, A_i + D_i)$  is referred to as  $J_i$ 's scheduling window. A job  $J_i$  is said to be current at time t if  $t \in [A_i, A_i + D_i)$ . A current job is active at time t, if it has not completed execution by time t.

We denote a real-time instance I as a finite or infinite collection of jobs  $I = \{J_1, J_2, \ldots\}$ .  $\mathcal{F}(I)$  denotes a real-time instance family with representative real-time instance I. For each job  $J'_i$  in real-time instance  $I' \in \mathcal{F}(I)$ , there is a job  $J_i$  in instance I with the same release time and deadline; however, the execution of  $J'_i$  cannot exceed the execution time of  $J_i$ . More formally,  $I' \in \mathcal{F}(I)$  if and only if

$$\forall J_i' \in I', \exists J_i \in I :: (A_i' = A_i) \land (D_i' = D_i) \land (E_i' \le E_i).$$

Informally,  $\mathcal{F}(I)$  represents a set of related real-time instances with I being the most "temporally constrained" of the set.

**Example 1** Consider a real-time instance  $I = \{(0,2,3), (5,4,5), (6,2,4)\}$ .  $\mathcal{F}(I)$  includes any instance  $I' = \{(0,x,3), (5,y,5), (6,z,4)\}$  such that  $0 \le x \le 2, 0 \le y \le 4$ , and  $0 \le z \le 2$ .

#### 2.2 Real-Time Task Models

In some simpler real-time systems, it may be possible to completely specify the real-time instance I prior to system run-time (i.e., the system designer has complete knowledge of each  $J_i \in I$ ). However, in systems with a large (or infinite) number of real-time jobs or systems that exhibit dynamic behavior, explicitly specifying each job, prior to system run-time, may be impossible or unreasonable. Fortunately, for systems where jobs may repeatedly

occur there is a more succinct representation of the repeating jobs via specification in some *recurrent task model*. A *task model* is the format and rules for specifying a task system. We may represent a set of repeating or related jobs by a recurrent task  $\tau_i$  specified according to the model M (e.g., the sporadic task model). For every execution of the system,  $\tau_i$  will generate a (possibly infinite) collection of real-time jobs.

Several recurrent tasks can be composed together into a recurrent task system  $\tau = \{\tau_1, \tau_2, \dots, \tau_n\}$ . The letter n will denote the number of tasks in a task system. Every system execution of task system  $\tau$  will result in the generation of a real-time instance I. We will denote the set of real-time instances that  $\tau$  can legally generate as  $\mathcal{I}^{\mathrm{M}}(\tau)$ . Based on the real-time instances that  $\tau$  generates, we can classify  $\tau$  as either *completely specified* or *partially-specified*. If the arrival-time and deadline parameters of each job  $J_i \in I$  can be determined prior to system run-time,  $\tau$  is a completely-specified task system. However, for many real-time systems, it is not possible to know beforehand what real-time instance will be generated by the system during run-time. Furthermore, completely-specified systems are incapable of handling changes in real-time workloads. To overcome the fragile and inflexible nature of completely-specified task systems, a designer may instead consider partially-specified tasks systems.\footnote{1}

Partially-specified task systems permit that different executions of the same system may result in different real-time instances (with different job arrival times) being generated. The specification for a partially-specified task system includes a set of constraints that any generated real-time instance must satisfy; in general, such a system may legally generate infinitely many different real-time instances, each of which satisfies the constraints placed upon their generation. Each such real-time instance may also have infinitely many jobs.

Let M and M' be task models. We say that task model M' generalizes task model M, if for every task system  $\tau$  specified in model M there exists a task system  $\tau'$  specified in model M' such that

$$I \in \mathcal{I}^{\mathrm{M}}(\tau) \Leftrightarrow I \in \mathcal{I}^{\mathrm{M}'}(\tau').$$

That is, for all task systems  $\tau$  that can be specified in task model M, there is a task system  $\tau'$  specified in task model M' that can generate exactly the same real-time instances as  $\tau$ . In the remainder of this subsection, we describe the Liu and Layland task model and sporadic task model in this more formal context.

§ Liu and Layland (LL) Task Model (Implicit-Deadline Sporadic Task Model). As mentioned in the introduction, the behavior of a LL task  $\tau_i$  can be characterized by a two-tuple  $(e_i, p_i)$ . As with the periodic task model,  $e_i$  indicates the worst-case execution time of any job generated by task  $\tau_i$ . The  $p_i$  parameter indicates the *minimum inter-arrival time* between successive jobs of  $\tau_i$  (note  $p_i$  denoted the *exact* inter-arrival time for periodic tasks). Let  $\mathcal{J}_{\text{WCET}}^{\text{LL}}(\tau_i)$  be a collection of real-time instances such that jobs of each real-time instance are generated by LL task  $\tau_i$  satisfying the minimum inter-arrival constraint and requiring the worst-case possible execution time; i.e.,  $I_{\tau_i}$  is a member of  $\mathcal{J}_{\text{WCET}}^{\text{LL}}(\tau_i)$  if and only if for all  $J_k \in I_{\tau_i}$  the following constraints are satisfied:

$$(E_k = e_i) \land (D_k = p_i) \land ((\exists J_{k+1} \in I_{\tau_i} \setminus \{J_k\} : A_{k+1} \ge A_k) \Rightarrow (A_{k+1} - A_k \ge p_i)). \tag{1}$$

The set of real-time instances that a LL task system  $\tau = \{\tau_1, \tau_2, \dots, \tau_n\}$  can generate (with worst-case possible execution time) is equal to

$$\mathcal{I}_{\text{WCET}}^{\text{LL}}(\tau) \stackrel{\text{def}}{=} \left\{ \bigcup_{i=1}^{n} I_{\tau_i} \mid (I_{\tau_1}, I_{\tau_2}, \dots, I_{\tau_n}) \in \prod_{i=1}^{n} \mathcal{J}_{\text{WCET}}^{\text{LL}}(\tau_i) \right\}.$$

(2)

Thus, the set of real-time instances generated by LL task system  $\tau$  is

$$\mathcal{I}^{\mathrm{LL}}(\tau) = \bigcup_{I_j \in \mathcal{I}_{\mathrm{WCET}}^{\mathrm{LL}}(\tau)} \mathcal{F}(I_j). \tag{3}$$

<sup>&</sup>lt;sup>1</sup>A partially-specified task system is sometimes referred to as non-concrete [14].

**Example 2** Consider the following LL task system:  $\tau = \{\tau_1 = (2,4), \tau_2 = (3,10)\}$ . Examples of sets of jobs in  $\mathcal{J}_{\text{WCET}}^{\text{LL}}(\tau_1)$  are  $\{(0,2,4),(4,2,4),(8,2,4),\ldots\}$ ,  $\{(0,2,4),(5,2,4),(9,2,4)\}$ , and  $\{(0,2,4),(6,2,4),(10,2,4),\ldots\}$ ; examples of sets of jobs in  $\mathcal{J}_{\text{WCET}}^{\text{LL}}(\tau_2)$  are  $\{(0,3,10),(10,3,10),(20,3,10),\ldots\}$ ,  $\{(1,3,10),(15,3,10),(25,3,10),\ldots\}$ .

§ **Sporadic Task Model.** The LL task model allows for flexibility in the job arrival times for a task  $\tau_i$ ; however, the model is still somewhat restrictive in forcing the deadline of each job generated by  $\tau_i$  to be equal to the minimum inter-arrival parameter  $p_i$ . It is easy to imagine scenarios where the deadline of a job is not correlated with the minimum inter-arrival: for example, in a car's brake system the minimum time between braking events may be considerably larger than the required braking-reaction time (i.e., deadline for halting the car). The sporadic task model generalizes the LL task model by adding a *relative deadline* parameter  $d_i$  to the specification for a task. Recall that a sporadic task  $\tau_i$  is specified by the three-tuple  $(e_i, d_i, p_i)$ . Let  $\mathcal{J}_{\text{WCET}}^{\text{S}}(\tau_i)$  be a collection of real-time instances that are jobs generated by sporadic task  $\tau_i$  satisfying the minimum inter-arrival constraint and requiring the worst-case possible execution time; i.e.,  $I_{\tau_i}$  is a member of  $\mathcal{J}_{\text{WCET}}^{\text{S}}(\tau_i)$  if and only if for all  $J_k \in I_{\tau_i}$

the following constraints are satisfied:

$$(E_k = e_i) \land (D_k = d_i) \land ((\exists J_{k+1} \in I_{\tau_i} \setminus \{J_k\} : A_{k+1} \ge A_k) \Rightarrow (A_{k+1} - A_k \ge p_i)). \tag{4}$$

(Note that the only difference from Equation 1 for LL jobs is that the  $D_k$  parameter for each job  $J_k$  is set to  $d_i$ ). The set of real-time instances that a sporadic task system  $\tau = \{\tau_1, \tau_2, \dots, \tau_n\}$  can generate (with worst-case possible execution times) is

$$\mathcal{I}_{\text{WCET}}^{\text{S}}(\tau) \stackrel{\text{def}}{=} \left\{ \bigcup_{i=1}^{n} I_{\tau_i} \mid (I_{\tau_1}, I_{\tau_2}, \dots, I_{\tau_n}) \in \prod_{i=1}^{n} \mathcal{J}_{\text{WCET}}^{\text{S}}(\tau_i) \right\}.$$

(5)

Thus, the set of real-time instances generated by sporadic task system  $\tau$  is

$$\mathcal{I}^{S}(\tau) = \bigcup_{I_{j} \in \mathcal{I}_{\text{WCET}}^{S}(\tau)} \mathcal{F}(I_{j}). \tag{6}$$

Observe that for any LL task system  $\tau = \{\tau_1 = (e_1, p_1), \dots, \tau_n = (e_n, p_n)\}$  we can represent the same task system in the sporadic model by the sporadic task system  $\tau' = \{\tau'_1 = (e_1, p_1, p_1), \dots, \tau_n = (e_n, p_n, p_n)\}$ . It is easy to see that  $\mathcal{I}^{\mathrm{LL}}(\tau) = \mathcal{I}^{\mathrm{S}}(\tau')$ ; therefore, the sporadic task model generalizes the LL task model.

§ More General Task Models. There are other known real-time task models more general than the sporadic task model. For example, the *generalized multiframe (GMF) task model* [5] allows for a task to generate sequence of jobs with heterogenous separation, relative deadlines, and worst-case execution parameters. Another general task model, known as the *recurring real-time task model* [4], allows for conditional generation of job sequences for a task. Both of these models generalize the sporadic task model. Thus, the impossibility of optimal online multiprocessor scheduling algorithms for sporadic task systems implies the impossibility of optimal scheduling algorithms for these more general task models, as well.

#### 2.3 Machine Model

This article focuses on the real-time scheduling upon multiprocessor platforms. More specifically, we will be concentrating on scheduling upon a class of multiprocessor platforms known as the *identical multiprocessors*. The identical multiprocessor model assumes that each processor in the platform has identical processing capabilities and speed. We denote the multiprocessor platform by  $\Pi$  and assume  $\Pi$  is comprised of m identical processors  $\pi_1$ ,  $\pi_2, \ldots, \pi_m \in \Pi$ . Recall from the beginning of this paper that each job corresponds to the execution of a sequential

segment of code by the processing platform. For each model introduced in the previous subsection, a real-time task has associated worst-case execution requirement parameter(s). These execution requirements represent the worst-case cumulative amount of execution time that a job generated by the task requires to execute to completion on the processing platform.

§ **Some Assumptions.** We will assume that each processor has unit-speed. We will assume that jobs are preemptable at arbitrary times with no additional cost. Furthermore, we allow scheduling algorithms which *migrate* jobs between processor; that is, a job may execute on different processors over its scheduling window; however, job-level parallelism is not permitted (i.e., a job may not execute concurrently with itself on two or more processors simultaneously). We will make the simplifying assumption that migration does not incur any additional penalty or execution. Throughout this article, we will also assume that tasks are *independent* of each other; that is, the execution of a job of one task is not contingent upon the status of a job of another task (e.g., blocking on shared resources is not permitted). Most of the above assumptions are not limiting; in fact, the nonexistence of optimal online multiprocessor scheduling algorithms for sporadic task systems under this simplified setting implies the non-existence of optimal scheduling algorithms when the assumptions on preemption, migration, and task independence are removed.

## 2.4 Real-Time Scheduling Algorithms

When executing a real-time application, the real-time scheduling algorithm must determine which current jobs are executing on the processing platform at every time instant. At an abstract level, the real-time scheduling algorithm determines the interleaving of execution for jobs of any real-time instance I on the processing platform  $\Pi$ . The interleaving of execution of I on  $\Pi$  is known as a *schedule*. The goal of a real-time scheduling algorithm is to produce a schedule that ensures that every job of I is allocated the processor (i.e., executes) for its execution requirement during its scheduling window. In this subsection, we give some formal definitions for real-time scheduling algorithm concepts.

We can formally define the schedule S for real-time instance I as a function of the processor and time.

**Definition 1 (Schedule Function)** Let  $S_I(\pi_k, t)$  be the job of I scheduled at time t on processor  $\pi_k \in \Pi$ ;  $S_I(\pi_k, t)$  is  $\bot$  if there is no task scheduled at time t (i.e.,  $S_I : \Pi \times \mathbb{R}^+ \mapsto I \cup \{\bot\}$ ). Let  $\mathbb{S}_{I,\Pi}$  be the set of all possible schedule functions over real-time instance I and platform  $\Pi$ .

It is sometimes useful to view the behavior of a single job of a real-time instance I in schedule  $S_I$ . The following definition allows us to characterize the schedule  $S_I$  with respect to task  $J_i$ .

**Definition 2 (Job-Schedule Function)**  $S_I(\pi_k, t, J_i)$  is an indicator function denoting whether  $J_i$  is scheduled at time t on processor  $\pi_k$  for schedule  $S_I$ . In other words,

$$S_I(\pi_k, t, J_i) \stackrel{\text{def}}{=} \begin{cases} 1, & \text{if } S_I(\pi_k, t) = J_i \\ 0, & \text{otherwise.} \end{cases}$$

(7)

A scheduling algorithm makes decisions about the order in which jobs of a real-time instance should execute. For systems that are partially-specified, an *online* algorithm is appropriate to handle dynamic job arrivals. For any time t, an online real-time scheduling algorithm decides the set of jobs that will be executed on  $\Pi$  at time t based on prior decisions and the status of jobs released at or prior to t. An online scheduling algorithm does not have specific information on the release of jobs after time t (i.e., future jobs arrival times are unknown). This article focuses on deterministic online, real-time multiprocessor scheduling algorithms.

At an abstract level, a real-time scheduling algorithm<sup>2</sup>  $\mathcal{A}$  (either static or offline) on platform  $\Pi$  is a higher-order function<sup>3</sup> from real-time instances to schedules over  $\Pi$  — i.e.,  $\mathcal{A}:\mathcal{I}^{\mathrm{M}}(\tau)\to\bigcup_{I\in\mathcal{I}}\mathbb{S}_{I,\Pi}$ . Let  $I_{\leq t}\stackrel{\mathrm{def}}{=}\{J_i\in I|A_i\leq t\}$ ; that is,  $I_{\leq t}$  is the set of jobs of I that arrive prior to or at time t. For an online scheduling algorithm  $\mathcal{A}$ ,  $I_{\leq t}$  represents the set of jobs that  $\mathcal{A}$  has knowledge of at time t (i.e.,  $\mathcal{A}$  knows the arrival time, execution requirement, and deadline parameters of the jobs of  $I_{\leq t}$ , but not other jobs of I). Up until time t, algorithm  $\mathcal{A}$  has made scheduling decisions without specific knowledge of jobs arriving after time t; furthermore, jobs arriving after t cannot have an effect on the schedule generated by  $\mathcal{A}$  from time zero to t. In other words, for an online scheduling algorithm future jobs cannot change past scheduling decisions.

**Definition 3 (Deterministic Online Scheduling Algorithm)** For any  $I \in \mathcal{I}^{\mathrm{M}}(\tau)$ , let  $S_{I}^{\mathcal{A}}$  be the schedule produced by algorithm  $\mathcal{A}$  for real-time instance I and platform  $\Pi$ . An online real-time scheduling algorithm must satisfy the following constraint: for all  $I, I' \in \mathcal{I}^{\mathrm{M}}(\tau)$  and for all t > 0,

$$(I_{\leq t} = I'_{\leq t}) \Rightarrow \left(\forall t'(0 \leq t' \leq t), \forall \pi_k \in \Pi :: S_I^{\mathcal{A}}(\pi_k, t') = S_{I'}^{\mathcal{A}}(\pi_k, t')\right). \tag{8}$$

Beyond restricting our attention to deterministic, online scheduling algorithms and algorithms that forbid job-level parallelism, we do not make any other restrictions on the scheduling algorithm.

## 2.5 Feasible Real-Time Task Systems

The definition of "optimal scheduling algorithm" makes use of the notion of a task system being feasible upon a processing platform: an optimal scheduling algorithm can correctly schedule any feasible task system. Thus, we need to formalize what we mean by "feasible task system." This subsection defines "feasible" and other related concepts.

When evaluating a real-time system, it is sometimes useful to describe the amount of "work" (execution) that a job does over a specified interval in a given schedule. The next definition defines the amount of "processor time" that a job receives over a given interval.

**Definition 4 (Work Function)**  $W(S_I, \pi_k, J_i, t_1, t_2)$  denotes the amount of processor time on  $\pi_k$  that  $J_i$  receives from schedule  $S_I$  over the interval  $[t_1, t_2)$ . In other words,<sup>4</sup>

$$W(S_I, \pi_k, J_i, t_1, t_2) \stackrel{\text{def}}{=} \int_{t_1}^{t_2} S_I(\pi_k, t, J_i) dt.$$

(9)

We can use a *system-work function* to describe the cumulative work done by all jobs of a real-time instance over a specified time interval in a given schedule.

**Definition 5 (System-Work Function)**  $W_I(S_I, t_1, t_2)$  denotes the amount of processor time (over all processors of  $\Pi$ ) received by all jobs of I in schedule  $S_I$  over the interval  $[t_1, t_2)$ .

$$W_I(S_I, t_1, t_2) \stackrel{\text{def}}{=} \sum_{\pi_k \in \Pi} \sum_{J_i \in I} W(S_I, \pi_k, J_i, t_1, t_2). \tag{10}$$

<sup>&</sup>lt;sup>2</sup>We will slightly abuse notation and use  $\mathcal{A}$  to refer to both the scheduling algorithm and the function.

<sup>&</sup>lt;sup>3</sup>A higher-order function has a function space as either the domain or range.

<sup>&</sup>lt;sup>4</sup>Since  $S_I(\pi_k, t, J_i)$  is potentially discontinuous at an infinite number of points,  $\int_{t_1}^{t_2} S_I(\pi_k, t, J_i) dt$  denotes a Lebesgue integral [15] and not a Riemann integral.

Not all functions from  $\Pi \times \mathbb{R}^+$  to I, for a given real-time instance I, represent valid executions of a real-time system that could generate the instance I. In particular, we must ensure the following: a job can only execute during its scheduling window, a job cannot execute concurrently with itself on two or more processors, and a job must execute for  $E_i$  time units in its scheduling window to meet its deadline. Using Definitions 1 through 5, we can now formally define a *valid* schedule  $S_I$  with respect to a real-time instance I:

**Definition 6 (Valid Schedule)**  $S_I \in \mathbb{S}_{I,\Pi}$  is valid (with respect to jobs of some real-time instance I and platform  $\Pi$ ) if and only if the following three conditions are satisfied:

- 1. For any  $J_i \in I$ , if  $t < A_i$  or  $t > A_i + D_i$  then  $S_I(\pi_k, t) \neq J_i$  for all  $\pi_k \in \Pi$  (i.e., a job cannot execute while it is outside its scheduling window). For this article, will assume that two different jobs of the same task may execute concurrently on different processors (i.e., intra-task parallelism is allowed, but intra-job parallelism is forbidden).

- 2. If  $S_I(\pi_i, t) \neq \bot$  and  $S_I(\pi_j, t) \neq \bot$  then  $S_I(\pi_i, t) \neq S_I(\pi_j, t)$  for all  $t \in \mathbb{R}^+$  and  $\pi_i \neq \pi_j \in \Pi$  (i.e., a job may not execute concurrently with itself).

- 3. For all  $J_i \in I$ ,  $W_I(S_I, J_i, A_i, A_i + D_i) = E_i$  (i.e., each job receives processing time on  $\Pi$  equal to its execution requirement between its release time and deadline).

Recall that a recurrent task system can potentially generate infinitely different distinct real-time instances over different executions of the system. Informally, a recurrent task system  $\tau$  is *feasible* on processing platform  $\Pi$  if and only if for every possible real-time instance there exists a way to meet all deadlines. If there is a way for a real-time instance I to meet all deadlines, we say that I is a *feasible instance* on processing platform  $\Pi$ .

**Definition 7 (Feasible Instance)** A real-time instance I is feasible on platform  $\Pi$  if and only if there exists  $S_I \in S_{I,\Pi}$  such that  $S_I$  is valid.

We may extend the definition of feasible real-time instances to recurrent task systems.

**Definition 8 (Feasible Task System)** Recurrent task system  $\tau$  in task model M is feasible on platform  $\Pi$  if and only if for all  $I \in \mathcal{I}^{\mathrm{M}}(\tau)$ , I is a feasible instance on  $\Pi$ .

# 3 Inapplicability of Prior Optimality Results for Multiprocessor Real-Time Scheduling

The nonexistence of optimal online multiprocessor real-time scheduling algorithms for arbitrary collection of jobs has been known since the late 1980s [12, 9]. However, as mentioned in the introduction, these results do not imply the nonexistence of optimal multiprocessor scheduling algorithms for sporadic task systems. In this section, we will briefly review the Dertouzos and Mok [9] proof of impossibility for optimal scheduling of arbitrary collection of real-time jobs and discuss why this result does not apply to sporadic task systems. We will omit a discussion of the Hong and Leung result [12], since a nearly identical argument will show that their results also do not apply to the sporadic task model setting. The following is a restatement of the main result from [9].

**Theorem 1 (from Dertouzos and Mok [9])** For two or more processors, no online scheduling algorithm can be optimal for arbitrary collections of real-time jobs without complete a priori knowledge of the absolute deadlines, execution time, and arrival time of each job.

Why does the above theorem not imply that sporadic task systems have no optimal multiprocessor scheduling algorithm? Intuitively, the reason is that for arbitrary real-time instances an optimal scheduling algorithm must be

able to correctly schedule any feasible real-time instances. While for sporadic task systems, an optimal scheduling algorithm must correctly schedule only feasible real-time instances that may be legally generated by a sporadic task system. To more clearly illustrate this point let us consider the following lemma from [9] used to prove Theorem 1.

**Lemma 1 (from Dertouzos and Mok [9])** For two or more processors, no online scheduling algorithm for arbitrary collections of real-time jobs without complete a priori knowledge of the arrival time of each job.

The above lemma is proven in [9] by finding a set of feasible real-time instances that are identical up until a some time t that would cause any deterministic online scheduling algorithm to miss a deadline after time t. Below is the example set of feasible real-time instances used by Dertouzos and Mok [9] to prove Lemma 1.

**Example 3** Define the following set of real-time instances.

$$I_{1} \stackrel{\text{def}}{=} \{J_{1} = (0, 2, 4), J_{2} = (0, 1, 1), J_{3} = (0, 1, 2)\},\$$

$$I_{2} \stackrel{\text{def}}{=} \{J_{4} = (1, 1, 1), J_{5} = (1, 1, 1)\},\$$

$$I_{3} \stackrel{\text{def}}{=} \{J_{6} = (1, 2, 2), J_{7} = (1, 2, 2)\},\$$

$$I_{A} \stackrel{\text{def}}{=} I_{1} \cup I_{2},\$$

$$I_{B} \stackrel{\text{def}}{=} I_{1} \cup I_{3}.$$

$$(11)$$

Consider how any online, deterministic scheduling algorithm  $\mathcal{A}$  would execute real-time instances  $I_A$  or  $I_B$  on platform  $\Pi = \{\pi_1, \pi_2\}$  comprised of two identical unit-speed processors. To simplify the presentation of the example, let us assume that  $\mathcal{A}$  only makes scheduling decisions at integer time instants (i.e., preemptions will not occur at non-integer time instants); the lemma holds even when we remove this simplifying assumption. If  $\mathcal{A}$  does not know the arrival times of each job prior to their arrival, at time zero algorithm  $\mathcal{A}$  can only make a scheduling decision based upon the knowledge of the set of jobs in  $I_1$  (for scheduling either  $I_A$  or  $I_B$ ). Real-time instances  $I_A$  and  $I_B$  appear to be identical to  $\mathcal{A}$  for all times in the interval [0,1). However,  $\mathcal{A}$  must make a decision about what set of jobs will execute over [0,1) on the two processors of  $\Pi$  without knowledge of the jobs that may arrive at time-instant one (i.e., at time zero,  $\mathcal{A}$  does not know whether it is executing  $I_A$  or  $I_B$ ). Obviously,  $\mathcal{A}$  must execute job  $I_B$  on some processor (w.l.o.g., assume  $I_B$ ) over the interval  $I_B$  for  $I_B$  to meet its deadline at time-instant one. The non-obvious choice is what should execute on  $I_B$  over  $I_B$  over  $I_B$ . There are three possible choices:

- 1.  $\mathcal{A}$  executes  $J_1$  on  $\pi_2$  over [0,1).

- 2.  $\mathcal{A}$  executes  $J_3$  on  $\pi_2$  over [0,1).

- 3. A executes no job on  $\pi_2$  over [0,1).

If  $\mathcal{A}$  executes  $J_1$  over [0,1), real-time instance  $I_A$  would miss a deadline at time-instant two; observe in this scenario  $J_3$ ,  $J_4$ , and  $J_5$  must execute exactly continuously over [1,2) to meet their deadline, but there are only two available processors. For a similar reason,  $I_A$  would also miss a deadline at time-instant two, if  $\mathcal{A}$  chose not to execute a job on  $\pi_2$  over [0,1). If  $\mathcal{A}$  instead executes  $J_3$  over [0,1), real-time instance  $I_B$  would miss a deadline at time-instant three, since  $J_1$ ,  $J_6$ , and  $J_7$  require continuous execution over [1,3). The reader should observe that  $I_A$  and  $I_B$  are both feasible on two processors (i.e., a valid schedule may be found for both instances). However, the above case analysis shows that for any choice made by  $\mathcal{A}$  at time zero (without knowledge of future job arrivals), there exist a feasible set of future job arrivals that will cause  $\mathcal{A}$  to miss a deadline. Thus, optimal online scheduling is impossible for arbitrary collections of real-time jobs on two processors. This example may easily be extended to an arbitrary number of processors.

For the above example to imply the non-existence of optimal online multiprocessor scheduling algorithms for sporadic task systems, we must show that  $I_A$  and  $I_B$  correspond to legal real-time instances generated by a sporadic task system  $\tau$  that is feasible on two processors. One possible sporadic task system that could generate both the real-time instances  $I_A$  and  $I_B$  is

$$\tau \stackrel{\text{def}}{=} \{ \tau_1 = (2, 4, \infty), \tau_2 = \tau_3 = \tau_4 = (1, 1, \infty), \tau_5 = (1, 2, \infty), \tau_6 = \tau_7 = (2, 2, \infty) \}. \tag{12}$$

The above task system allows each job of  $I_A \cup I_B$  to be generated by a different task. Real-time instances  $I_A$  and  $I_B$  satisfy the constraints of Equation 4 for task system  $\tau$ . However,  $\tau$  is not feasible on two processors since the real-time instance where each task of  $\tau$  generates a job at time-instant zero is also a legal real-time instance; such an instance requires that at least five jobs execute continuously over [0,1)! Other possible groupings of jobs to task also appear to result in a sporadic task system that is infeasible on two processors. The difficulty in finding a feasible task system that can generate both  $I_A$  and  $I_B$ , suggests that such a sporadic task system may not exist. Thus, Lemma 1 and Theorem 1 do not directly imply anything about the existence of an optimal online algorithm for sporadic task systems. A similar argument may be used to argue about the inapplicability of the results of Hong and Leung [12] to sporadic task systems. We should also point out that the main result of Section 4 (Theorem 3) implies the impossibility of optimal scheduling for arbitrary collections of real-time jobs without knowledge of future arrival times. Thus, our results can be considered a strengthening of the impossibility results of both Dertouzos and Mok [9] and Hong and Leung [12].

# 4 Impossibility of Optimal Online Multiprocessor Scheduling for Sporadic and More General Task Systems

We now present the main result of this article. Our method of proving that optimal online algorithms do not exist for sporadic task systems is as follows.

- 1. Find a potentially feasible sporadic task system  $\tau$  on some processing platform  $\Pi$ .

- 2. Prove that the task system is feasible a multiprocessor platform  $\Pi$ . This means that for any real-time instance generated by  $\tau$  on  $\Pi$  there exists a schedule on  $\Pi$  that will meet all deadlines.

- 3. For the feasible task system  $\tau$ , show there exists a set of real-time instances generated by  $\tau$  that are identical up to a time t (denoted by  $\mathcal{I}'(\tau)$ ); however, at time t they require any online scheduling algorithm  $\mathcal{A}$  to make a decision regarding which current jobs to schedule (i.e., there are more current jobs than processors at time t). Show that regardless of the choice made by  $\mathcal{A}$  at time t, there exists a real-time instance in  $\mathcal{I}'(\tau)$  that causes the choice made by  $\mathcal{A}$  at time t to result in a deadline miss.

In this brief section, we give the details of Steps 1 and 3. Step 3 especially gives insight into why optimal online scheduling of sporadic task systems is impossible. The proof of feasibility (Step 2), though very important to showing the nonexistence of optimal scheduling algorithms, is extremely complex and not necessary to understanding the main result of this paper; therefore, we have decided to defer the details of Step 2 until the next section (Section 5).

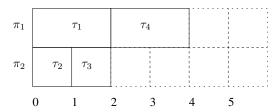

In accordance with Step 1 of the above approach, consider the following task system,  $\tau^{\text{example}}$ , comprised of six tasks (recall that a sporadic task is specified by three-tuple  $(e_i, d_i, p_i)$ ) and described by Figure 1a.

**Theorem 2**  $\tau^{\text{example}}$  is feasible on two processors.

**Proof:** Proved in Section 5. ■

|          | $e_i$ | $d_i$ | $p_i$ |

|----------|-------|-------|-------|

| $	au_1$  | 2     | 2     | 5     |

| $\tau_2$ | 1     | 1     | 5     |

| $	au_3$  | 1     | 2     | 6     |

| $\tau_4$ | 2     | 4     | 100   |

| $	au_5$  | 2     | 6     | 100   |

| $	au_6$  | 4     | 8     | 100   |

(a) Task system  $au^{\text{example}}$

(b) The times at which tasks  $\tau_1$ ,  $\tau_2$ ,  $\tau_3$ , and  $\tau_4$  must execute

Figure 1. System  $au^{\mathrm{example}}$  and Its Execution.

**Lemma 2** No optimal online algorithm exists for the multiprocessor scheduling real-time, constrained-deadline sporadic task systems on two processors.

**Proof:** The proof is by contradiction. Assume there exists an optimal online algorithm,  $\mathcal{A}$ , for scheduling constrained-deadline sporadic real-time tasks on two processors. Then, by Theorem 2,  $\mathcal{A}$  must find a valid schedule for  $\tau^{\text{example}}$  where no deadline is missed; more formally, for all  $I \in \mathcal{I}^{\text{S}}(\tau^{\text{example}})$ , the schedule  $\mathcal{A}(I)$  is valid (Definition 6). Figure 1a shows task system  $\tau^{\text{example}}$ .

Let each task of  $\tau^{\text{example}}$  release a job at time zero. Figure 1b shows the slots at which  $\mathcal{A}$  must execute  $\tau_1, \tau_2, \tau_3$ , and  $\tau_4$  (i.e., any other order would result in a deadline miss). Let  $\mathcal{I}_{\text{zero}}(\tau^{\text{example}})$  be the set of all real-time instances generated by  $\tau^{\text{example}}$  where each task generates a job at time instant zero and all jobs execute for their respective task's worst-case execution requirement; all real-time instances in  $\mathcal{I}_{\text{zero}}(\tau^{\text{example}})$  must include the following six jobs (recall a real-time job is specified by  $(A_i, E_i, D_i)$ ): (0, 2, 2), (0, 1, 1), (0, 1, 2), (0, 2, 4), (0, 2, 6), and (0, 4, 8). Note, that by the minimum separation parameter (period) of each task, the earliest the second job of any task may be generated is at time five. So, for all I and I' in  $\mathcal{I}_{\text{zero}}(\tau^{\text{example}}), I_{<5}$  and  $I'_{<5}$  are identical.

For any  $I \in \mathcal{I}_{zero}(\tau^{\text{example}})$ , there exist two possible choices that  $\mathcal{A}$  must make regarding the execution of  $\tau_5$ .

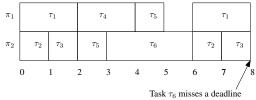

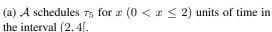

- 1. A schedules  $\tau_5$  for x (0 <  $x \le 2$ ) units of time in the interval (2, 4].

- 2.  $\mathcal{A}$  does not schedule  $\tau_5$  in the interval (2, 4].

Since  $\mathcal{A}$  is an online scheduling algorithm, by Definition 3, any  $I, I' \in \mathcal{I}_{zero}(\tau^{\text{example}})$  where  $I_{\leq 5} = I'_{\leq 5}$  implies that the schedule generated by  $\mathcal{A}$  for both I and I' is identical up to t=5. Thus, algorithm  $\mathcal{A}$  will make the same choice (either choice 1 or 2, above) for all instances in  $\mathcal{I}_{zero}(\tau^{\text{example}})$ . We will show that for either choice made by algorithm  $\mathcal{A}$  there exists an  $I_{miss} \in \mathcal{I}_{zero}(\tau^{\text{example}})$  that forces a deadline miss. Let us consider both cases.

1.  $\mathcal{A}$  schedules  $\tau_5$  for x ( $0 < x \le 2$ ) units of time in the interval (2,4]: Consider any real-time instance I in  $\mathcal{I}_{zero}(\tau^{\mathrm{example}})$  where, in addition to the six jobs that all real-time instances in  $\mathcal{I}_{zero}(\tau^{\mathrm{example}})$  must contain, I includes a job generated by  $\tau_1$ ,  $\tau_2$ , and  $\tau_3$  at t=6; that is, I must include the jobs: (6,2,2),(6,1,1), and (6,1,2). It is obvious that the two processors are fully utilized by  $\tau_1,\tau_2$ , and  $\tau_3$  over the interval (6,8]; therefore,  $\tau_6$  may not execute over the interval (6,8] (otherwise, either  $\tau_1,\tau_2$ , or  $\tau_3$  will miss a deadline). This implies that  $\tau_6$  must execute in the interval (2,6] given real-time instance I. However,  $\mathcal I$  chose to execute  $\tau_5$  in (2,4] for x time units, and  $\tau_4$  requires a processor to execute job (0,2,4) continuously. Thus, given the choice by  $\mathcal A$  and real-time instance I, there only exists 4-x units of time in which  $\tau_6$  may execute in the interval (2,4];  $\tau_6$  will miss a deadline at t=8. Figure 2a shows this scenario.

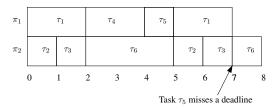

(b)  $\mathcal{A}$  does not schedule  $\tau_5$  in the interval (2,4[

Figure 2. Two Execution Scenarios for  $au^{ ext{example}}$ .

2.  $\mathcal{A}$  does not schedule  $\tau_5$  in the interval (2,4]: Consider any real-time instance I' in  $\mathcal{I}_{zero}(\tau^{\mathrm{example}})$  where, in addition to the six jobs that all real-time instances in  $\mathcal{I}_{zero}(\tau^{\mathrm{example}})$  must contain, I' includes a job generated by  $\tau_1$  and  $\tau_2$  at t=5; that is, I' must include the jobs (5,2,2) and (5,1,1). It is clear that the two processors are fully utilized by  $\tau_1$  and  $\tau_2$  over interval (5,6]. However, since  $\mathcal{A}$  chose not to execute  $\tau_5$  in the interval (2,4],  $\tau_5$  must continuously execute in the interval (4,8] to meet its deadline. In this scenario, three jobs must continuously execute in the interval (5,6]. Therefore, either  $\tau_1,\tau_2$ , or  $\tau_5$  will miss a deadline in the interval (5,6]. Figure 2b illustrates this scenario.

Since for any of the choices made by  $\mathcal{A}$  over the interval (2,4], there exists a real-time instance  $I \in \mathcal{I}_{zero}(\tau^{example})$  that causes  $\mathcal{A}$  to miss a deadline, this contradicts our assumption that there exists an optimal algorithm  $\mathcal{A}$ . Therefore, no optimal algorithm for scheduling sporadic real-time tasks upon a two-processor platform can exist.

We may easily generalize the above lemma to an arbitrary number of processors (m > 1).

**Theorem 3** No optimal online algorithm exists for the multiprocessor scheduling real-time, constrained-deadline sporadic task systems on two or more processors.

**Proof:** For any  $\Pi$  comprised of m>1 identical unit-speed processors, consider the task system  $\tau' \stackrel{\text{def}}{=} \tau^{\text{example}} \cup \{\tau'_1,\tau'_2,\ldots,\tau'_{m-2}\}$  where  $\tau'_i=(1,1,1)$  for all  $0< i\leq m-2$ . It is easy to see that  $\tau'$  is feasible on  $\Pi$ , as we can dedicate a processor to each of the tasks in  $\{\tau'_1,\tau'_2,\ldots,\tau'_{m-2}\}$  and by Theorem 2  $\tau^{\text{example}}$  is feasible on the remaining two processors. The argument of Lemma 2 holds in the case where each of  $\{\tau'_1,\tau'_2,\ldots,\tau'_{m-2}\}$  generate jobs at time zero and successive jobs as soon as legally allowable. Therefore, the jobs generated by  $\tau^{\text{example}}$  cannot use the additional processors, and the argument of the lemma is identical.

The above negative result immediately extends to any task model that generalizes the sporadic task model. The reason is that for any model M that generalizes the sporadic model, there exists a  $\tau'^{\mathrm{M}}$  specified in model M such that  $I \in \mathcal{I}^{\mathrm{M}}(\tau'^{\mathrm{M}})$  if and only if  $I \in \mathcal{I}^{\mathrm{S}}(\tau')$ . Therefore, the argument of Lemma 2 is unchanged for this more general task system (e.g., arbitrary-deadline sporadic task systems or GMF task systems).

**Corollary 1** No optimal online algorithm exists on two or more processors for the multiprocessor scheduling of real-time task systems in models that generalize the sporadic task model.

# 5 Feasibility of Sporadic Task System $au^{\mathrm{example}}$ on Two Processors

Section 4 introduced task system  $\tau^{\rm example}$  (given by Figure 1a) that is used to prove that optimal online multiprocessor scheduling of arbitrary and constrained task systems is impossible. In this section, we give a formal proof of Theorem 2; that is, task system  $\tau^{\rm example}$  is feasible on two processors.

In Section 5.1, we informally outline our proof. In Section 5.2, we introduce additional formal notation involved in  $\tau^{\text{example}}$ 's feasibility proof. In Section 5.3, we give the entire feasibility proof.

#### 5.1 Outline

The goal of Theorem 2 is to show that task system  $\tau^{\text{example}}$  is feasible on two processors. However, we are unaware of any existing, non-trivial, exact feasibility test for constrained-deadline task systems on a multiprocessor platform that could precisely determine whether  $\tau^{\text{example}}$  is feasible on two processors or not. For instance, the task system does not satisfy the sufficient feasibility condition [11]. The sufficient conditions for feasibility of sporadic task systems of Baker and Cirinei [2] only apply to single processors. Finally, the exact "brute-force" multiprocessor schedulability algorithm of Baker and Cirinei [3] does not trivially extend to multiprocessor feasibility. Furthermore, even if one could extend the brute-force result to multiprocessor feasibility, our approach does not assume integer arrival times and execution (as would be required by the current brute-force approach). Thus, since we may not validate the feasibility of  $\tau^{\text{example}}$  with previously-known techniques, we must tailor an argument specially for task system  $\tau^{\text{example}}$ . Specifically, we must show that for every legal real-time instance I generated by task system  $\tau^{\text{example}}$ , there exists a valid schedule in which no deadlines are missed (i.e.,  $\tau^{\text{example}}$  satisfies the definition of feasible task system according to Definition 8).

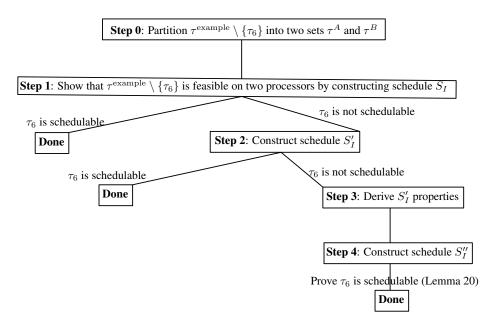

The approach that we take for proving Theorem 2 is to show, for any  $I \in \mathcal{I}_{\mathrm{WCET}}^{\mathrm{S}}(\tau^{\mathrm{example}})$ , that a valid schedule may be constructed for I on two processors<sup>5</sup>. It turns out that it is very easy to find a schedule on two processors for the set of tasks  $\tau^{\mathrm{example}} \setminus \{\tau_6\}$ ; so, we construct this schedule, denoted  $S_I$ , for the jobs of  $\tau^{\mathrm{example}} \setminus \{\tau_6\}$  in real-time instance I. If the jobs of  $\tau_6$  in instance I can execute completely during the processor idle times for  $S_I$  (i.e., when jobs of  $\tau^{\mathrm{example}} \setminus \{\tau_6\}$  are not executing in  $S_I$ ), then we have shown that a valid schedule exists for instance I. However, it is possible that there does not exist sufficient idle processor time to execute every job of  $\tau_6$  in  $S_I$ . Therefore, we may need to modify schedule  $S_I$  further. Our approach considers up to two additional modified schedules,  $S_I'$  and  $S_I''$  – defined separately for ease of presentation and clarity. Our final step is to show that if  $\tau_6$  could not complete in either  $S_I$  or  $S_I'$ , all jobs of  $\tau_6$  must complete in  $S_I''$ . The following steps informally explain our proof of showing that a valid schedule exists on two processors for any  $I \in \mathcal{I}_{\mathrm{WCET}}^{\mathrm{S}}(\tau^{\mathrm{example}})$ . Figure 3 gives a diagram of the steps of the proof.

**Step 0)** Partition  $\tau^{\text{example}} \setminus \{\tau_6\}$ : Consider a partition of  $\tau^{\text{example}} \setminus \{\tau_6\}$  into two sets:

$$\tau^A \stackrel{\text{def}}{=} \{ \tau_1, \tau_4 \}, \tag{13}$$

and

$$\tau^B \stackrel{\text{def}}{=} \{ \tau_2, \tau_3, \tau_5 \}. \tag{14}$$

- Step 1) Construct schedule  $S_I$  to show that  $\tau^{\text{example}} \setminus \{\tau_6\}$  is feasible on two processor: Using known uniprocessor scheduling algorithms, we show that  $\tau^A$  may be correctly scheduled on processor  $\pi_1$  and  $\tau^B$  may be scheduled on processor  $\pi_2$ .

- Step 2) Construct a modified schedule  $S'_I$ : If the jobs of  $\tau_6$  cannot completely execute by their deadlines on processor  $\pi_2$  (the less "loaded" of the two processors in  $S_I$ ) during the idle time instants in schedule  $S_I$ , we will construct a new schedule  $S'_I$ . For any real-time instance I,  $S'_I$  is a global schedule (i.e., non-partitioned) constructed by moving as much work as possible to the first processor  $\pi_1$  (with respect to idle times in  $S_I$  schedule for processor  $\pi_1$ ).

<sup>&</sup>lt;sup>5</sup>Please note that we only consider real-time instances in  $I \in \mathcal{I}_{\text{WCET}}^{\text{S}}(\tau^{\text{example}})$ ; the feasibility of any instance  $I' \in \mathcal{I}^{\text{S}}(\tau^{\text{example}})$  follows from the fact that there exists an  $I \in \mathcal{I}_{\text{WCET}}^{\text{S}}(\tau^{\text{example}})$  such that  $I' \in \mathcal{F}(I)$ . So, we only need to consider a valid schedule  $S_I''$  and it suffices to use the same schedule for I' (except the jobs of I' will potentially execute for less than the jobs of I).

Figure 3. Logical steps in proof of Theorem 2.

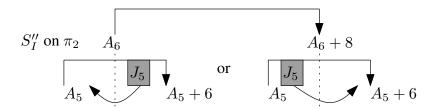

Step 3) Derive properties of schedule  $S'_I$  if  $\tau_6$  cannot complete execution: We will derive several properties in the event that  $\tau_6$  cannot complete during the idle instants in schedule  $S'_I$ . These properties will be useful in defining a second modified schedule  $S'_I$  in which  $\tau_6$  can complete execution.

Step 4) Construct a second modified schedule  $S_I''$  that leaves sufficient room for  $\tau_6$  to be completely assigned to the second processor: Again, if  $\tau_6$  cannot completely execute during the idle times instants on processor  $\pi_2$  in schedule  $S_I'$ , we construct a second modified schedule  $S_I''$ . The properties of the previous step will be used to show that a schedule  $S_I''$  can always be constructed that leaves the second processor idle for four units between the release and deadline of a any job of  $\tau_6$ . Obviously,  $\tau_6$  can be completely assigned to these idle times. Therefore,  $\tau^{\text{example}}$  is feasible on two unit-capacity processors (Theorem 2).

In the next section, we discuss some additional notation needed for our proof. In Section 5.3, we formally carry-out the steps outlined in this subsection.

#### 5.2 Notation

In this section, we present general notation for describing the scheduling and behavior of a sporadic task system  $\tau$ . The remainder of this section heavily relies on the notation presented in Sections 2.4 and 2.5. The notation defined for the remainder of this section will assume that  $\tau$  is a constrained-deadline system (i.e., for all  $\tau_i \in \tau$ ,  $d_i \leq p_i$ ). For each  $I \in \mathcal{I}^S_{WCET}(\tau)$ , let  $I(\tau_i) \subseteq I$  denote the jobs generated by  $\tau_i$  in instance I.

The next two functions give the "nearest" job release-time and deadline with respect to a given time t and real-time instance  $I(\tau_i)$ .

**Definition 9 (Job-Release Function)** If  $\tau_i$  is current at time t in real-time instance I then  $r_i(I,t)$  is the release time of the most recently released job of  $\tau_i$  (with respect to time t). Otherwise,  $r_i(I,t) = \infty$  if  $\tau_i$  is not in a scheduling window at time t. More formally,

$$r_{i}(I,t) \stackrel{\text{def}}{=} \left\{ \begin{array}{l} A_{k} , & \text{if } \exists J_{k} \in I(\tau_{i}) \text{ such that } A_{k} \leq t \leq A_{k} + D_{k} \\ \infty , & \text{otherwise.} \end{array} \right. \tag{15}$$

**Definition 10 (Job-Deadline Function)** If  $\tau_i$  is current at time t for real-time instance I then  $d_i(I,t)$  is the absolute deadline of the most recently released job of  $\tau_i$  (with respect to time t). Otherwise,  $d_i(I,t) = -\infty$  if  $\tau_i$  is not in a scheduling window at time t.

$$d_i(I,t) \stackrel{\text{def}}{=} \left\{ \begin{array}{l} A_k + D_k , & \text{if } \exists J_k \in I(\tau_i) \text{ such that } A_k \le t \le A_k + D_k \\ -\infty , & \text{otherwise.} \end{array} \right.$$

(16)

The following function is useful for identifying the current current job (if any) of task  $\tau_i$  at time t.

**Definition 11 (Current-Job Function)** If  $\tau_i$  is current at time t for real-time instance I,  $\varphi_i(I,t)$  is the current job at time t. Otherwise,  $\varphi_i(I,t) = \bot$ , if  $\tau_i$  is not in a scheduling window at time t.

$$\varphi_i(I,t) \stackrel{\text{def}}{=} \left\{ \begin{array}{l} J_k , & \text{if } \exists J_k \in I(\tau_i) \text{ such that } A_k \le t \le A_k + D_k \\ \bot , & \text{otherwise.} \end{array} \right.$$

(17)

Similar to Definition 2 which defined a schedule function with respect to jobs of a real-time instance, we can define the schedule S as a function with respect to task  $\tau_i$ .

**Definition 12 (Task-Schedule Function)**  $S_I(\pi_\ell, t, \tau_i)$  is an indicator function denoting whether task  $\tau_i$  is scheduled at time t for schedule  $S_I$ . In other words,

$$S_I(\pi_\ell, t, \tau_i) \stackrel{\text{def}}{=} \begin{cases} 1, & \text{if } \exists J_k \in I(\tau_i) :: S_I(\pi_\ell, t, J_i) = 1 \\ 0, & \text{otherwise.} \end{cases}$$

(18)

The next definition defines the work that task  $\tau_i$  receives on  $\pi_\ell$  over a given interval. The job work function (Definition 4) is used.

**Definition 13 (Task-Work Function)**  $W_i(S_I, \pi_\ell, t_1, t_2)$  denotes the amount of processor time that  $\tau_i$  receives from schedule  $S_I$  on processor  $\pi_\ell$  over the interval  $[t_1, t_2)$  for real-time instance I. In other words,

$$W_i(S_I, \pi_\ell, t_1, t_2) \stackrel{\text{def}}{=} \sum_{J_k \in I(\tau_i)} W(S_I, \pi_\ell, J_i, t_1, t_2). \tag{19}$$

**Definition 14 (Idle-Work Function)**  $W_{\perp}(S_I, \pi_{\ell}, t_1, t_2)$  denotes the total amount of processor time that schedule  $S_I$  idles processor  $\pi_{\ell}$  over the interval  $[t_1, t_2)$  for real-time instance I. In other words,

$$W_{\perp}(S_I, \pi_{\ell}, t_1, t_2) \stackrel{\text{def}}{=} W(S_I, \pi_{\ell}, \perp, t_1, t_2).$$

(20)

#### 5.3 Proof

In this section, we prove Theorem 2 by following the steps outlined in Section 5.1. Obviously, Step 0 has already been given in the proof outline of Section 5.1; thus, we begin with Step 1. Section 5.3.1 gives the construction for schedule  $S_I$  for Step 1. Section 5.3.2 describes the construction of schedule  $S_I'$  for Step 2. Section 5.3.3 proves several important properties about  $S_I'$ , if  $\tau_6$  cannot be scheduled during the idle times (Step 3). Finally, Section 5.3.4 defines schedule  $S_I''$  which can be shown to accommodate all jobs of task  $\tau_6$  on processor  $\tau_2$  (Step 4).

## **5.3.1** Step 1: Construction of Schedule $S_I$

The first step of the outline (Section 5.1) of the proof requires us to show that the partition  $\tau^A$  and  $\tau^B$  of  $\tau^{\text{example}} \setminus \{\tau_6\}$  is feasible on two processors and give a valid schedule for real-time instance  $I \in \mathcal{I}^{\text{S}}_{\text{WCET}}(\tau)$ . We can easily obtain feasibility of this task system by partitioning  $\tau^{\text{example}} \setminus \{\tau_6\}$  into two sets and scheduling each subset on its own processor using a uniprocessor scheduling algorithm called the *deadline-monotonic* (DM) scheduling algorithm. For each processor, DM executes at any time instant the active job of the task with the smallest relative deadline parameter (among the set of all tasks assigned to that processor with active jobs). For simplicity of analysis, we will use DM on each processor.

Audsley et al. [1] developed a test to determine whether each task in a *constrained-deadline* task system can be scheduled by DM on a single processor to always meet all deadlines. Let  $\mathbf{T}_{H_i}$  be the set of tasks with priority greater than or equal to task  $\tau_i$  under the DM priority assignment. The following theorem restates their result.

**Theorem 4 (from [1])** In a constrained-deadline, sporadic task system, task  $\tau_i$  always meets all deadlines using DM on a preemptive uniprocessor if and only if  $\exists t \in (0, d_i]$  such that

$$\left( CBF(\tau_i, t) \stackrel{\text{def}}{=} \sum_{\tau_j \in \mathbf{T}_{H_i}} RBF(\tau_j, t) + e_i \right) \le t.$$

(21)

Using this result, we obtain the following lemma which states that  $\tau^{\text{example}} \setminus \{\tau_6\}$  is feasible on the given two-processor platform:

**Lemma 3**  $\tau^{\text{example}} \setminus \{\tau_6\}$  is feasible on a multiprocessor platform composed of two unit-capacity processors.

**Proof:** For partition  $\tau^A$  and  $\tau^B$  of  $\tau^{\text{example}} \setminus \{\tau_6\}$  (Equations 13 and 14), assign  $\tau^A$  to  $\pi_1$  and  $\tau^B$  to  $\pi_2$ . It is easy to verify by Theorem 4 that  $\tau^A$  and  $\tau^B$  are feasible with respect to their assigned processors. First, we will show that  $\tau^A$  is feasible on processor  $\pi_1$ .  $\tau_1$  always meets all deadlines (according to Theorem 4) on  $\pi_1$  with respect to task system  $\tau^A$  because  $\text{CBF}(\tau_1, 2) = 2 \le 2$ . Similarly,  $\tau_4$  always meets all deadlines on  $\pi_1$  because  $\text{CBF}(\tau_4, 4) = 2 + 2 = 4 \le 4$ . Since both of these tasks always meet all deadlines using DM on  $\pi_1$  over all real-time instance  $I_A \in \mathcal{I}^S_{\text{WCET}}(\tau^A)$ ,  $\tau^A$  is feasible on  $\pi_1$  according to Definition 8.

Next, we will show that  $\tau^B$  is feasible on processor  $\pi_2$ .  $\tau_2$  always meets all deadlines on  $\pi_2$  because  $\mathrm{CBF}(\tau_2,1)=1\leq 1$ .  $\tau_3$  always meets all deadlines on  $\pi_2$  due to  $\mathrm{CBF}(\tau_3,2)=1+1=2\leq 2$ . Finally,  $\tau_5$  always meets all deadlines on  $\pi$  because  $\mathrm{CBF}(\tau_5,4)=1+1+2=4\leq 4$ . Since all three of these tasks always meet all deadlines using DM on  $\pi_2$  over all real-time instances  $I_B\in\mathcal{I}^\mathrm{S}_{\mathrm{WCET}}(\tau^B)$ ,  $\tau^B$  is feasible on  $\pi_2$  according to Definition 8. Combining the two uniprocessor schedules from DM, we get a valid multiprocessor schedule for  $\tau^{\mathrm{example}}\setminus\{\tau_6\}$ , and the lemma follows.  $\blacksquare$

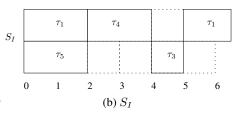

Let  $S_I$  be the schedule constructed by DM on each processor for task system  $\tau^{\text{example}} \setminus \{\tau_6\}$  with partitions  $\tau^A$  and  $\tau^B$ . From the previous argument,  $S_I$  is valid for I (with  $\tau_6$ 's jobs excluded).

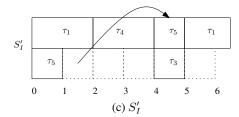

# **5.3.2** Step 2: Construction of Schedule $S'_I$

If the jobs generated by  $\tau_6$  in real-time instance I cannot complete by their deadlines in the idle times of  $S_I$ , we must proceed to Step 2 of our proof outline: construct a schedule  $S_I'$  that is globally (non-partitioned) feasible. The goal of this step is to move as much computation off processor  $\pi_2$  as possible. To accomplish this goal, for every idle instant on processor  $\pi_1$  in schedule  $S_I$ , we move a task in its scheduling window on  $\pi_2$  to  $\pi_1$  (if such a task exists). The construction "builds" schedule  $S_I'$  for processor  $\pi_1$ , first. After  $S_I'(\pi_1, t)$  is constructed, then  $S_I'$

|         | $e_i$ | $d_i$ | $p_i$ |

|---------|-------|-------|-------|

| $	au_1$ | 2     | 2     | 5     |

| $	au_3$ | 1     | 2     | 6     |

| $	au_4$ | 2     | 4     | 100   |

| $	au_5$ | 2     | 6     | 100   |

(a) replicates the legend for these tasks

Figure 4. Construction of Schedule  $S_I'$ . Note that the execution of  $\tau_5$  in the interval [1,2) is moved from the second processor to [4,5) on the first processor.

is constructed for  $\pi_2$ . Note that such a schedule could not be constructed online (i.e., it is an off-line constructed schedule), since  $S_I'(\pi_2,t)$  may require that  $S_I'(\pi_1,t')$  be known for some t'>t (i.e.,  $S_I'(\pi_2,t)$  requires knowledge of future events). Constructing an offline schedule is not a contradiction of Theorem 3 as feasibility requires us only to construct (by any means) a valid schedule for any real-time instance that may be generated by  $\tau^{\text{example}}$ .

In schedule  $S_I'(\pi_1,t)$ , tasks of set  $\tau^A$  (tasks  $\tau_1$  and  $\tau_4$ ) execute at exactly the same times as they did in schedule  $S_I(\pi_1,t)$  (i.e., the uniprocessor rate-monotonic schedule for  $\tau^A$  and  $\tau^B$ ). However, the tasks of set  $\tau^B$  move as much execution as possible (without disturbing tasks of  $\tau^A$ ) from processor  $\pi_2$  to processor  $\pi_1$ . Consider an arbitrary time t.  $S_I'(\pi_1,t)$  is constructed using the following rules:

- 1. If at time t processor  $\pi_1$  is busy executing a job from tasks of  $\tau^A$  in schedule  $S_I$ , then  $S_I'(\pi_1, t)$  equals  $S_I(\pi_1, t)$ .

- 2. If processor  $\pi_1$  is idle at time t in schedule  $S_I$ , then:

- (a) If task  $\tau_5$  is in its scheduling window (i.e.,  $r_5(I,t) < \infty$ ) and it has not already executed for more than  $e_5$  time units in  $S_I'$  on processor  $\pi_1$ , then  $S_I'$  at time t is set to the current job of  $\tau_5$  i.e  $S_I'(\pi_1,t) = \varphi_5(I,t)$ ;

- (b) else, if task  $\tau_2$  is in its scheduling window (i.e.,  $r_2(I,t) < \infty$ ) and it has not already executed for more than  $e_2$  time units in S' on processor  $\pi_1$ , then  $S'_I$  at time t is set to the current job of  $\tau_2$  i.e  $S'_I(\pi_1,t) = \varphi_2(I,t)$ ;

- (c) else, if task  $\tau_3$  is in its scheduling window (i.e.,  $r_3(I,t) < \infty$ ) and it has not already executed for more than  $e_3$  time units in S' on processor  $\pi_1$ , then  $S'_I$  at time t is set to the current job of  $\tau_3$  i.e  $S'_I(\pi_1,t) = \varphi_3(I,t)$ ;

- (d) *else*, leave processor  $\pi_1$  idle.

Note the above order that we move jobs of tasks (i.e., in order of  $\tau_5$ ,  $\tau_2$ , and  $\tau_3$ ) is significant.

The execution of jobs of tasks in  $\tau^B$  that could not be moved to processor  $\pi_1$  is executed on processor  $\pi_2$  (with the added constraint that a task does not execute in parallel with itself). For arbitrary time t,  $S_I'(\pi_2, t)$  is constructed using the following rule: if, at time instant t, a job  $J_k$  of task  $\tau_i \in \tau^B$  is executing on processor  $\pi_2$  in schedule  $S_I$  (i.e.,  $S_I(\pi_2, t, J_k) = 1$ ), then  $J_k$  will also execute on processor  $\pi_2$  at time instant t in schedule  $S_I'$  only if the following two conditions are true,

1.  $J_k$  is not executing on processor  $\pi_1$  at time t in schedule  $S_I'$  (i.e.,  $S_I'(\pi_2, t, J_k) = 0$ ), and

2. the total time that job  $J_k$  has executed on processor  $\pi_1$  between its arrival and its absolute deadline and on processor  $\pi_2$  between its arrival and time t in schedule  $S'_I$  is strictly less than  $e_i$ .

Figure 4 presents a visual example comparing schedules  $S_I$  and  $S_I'$ . The following construction is the inductive formal definition of the modified schedule for all  $I \in \mathcal{I}_{\mathrm{WCET}}^{\mathrm{S}}(\tau^{\mathrm{example}} \setminus \{\tau_6\})$  and  $t \geq 0$ . Please note that  $S_I'(\pi_1,t)$  is inductively constructed first for all  $t \geq 0$ .  $S_I'(\pi_2,t)$  is constructed after  $S_I'$  for processor  $\pi_1$ . Also, note that  $S_I'$  is not *work-conserving* in the sense that a processor may be idle at time t, even if there are active jobs with remaining execution.

$$S'_{I}(\pi_{1},t) \stackrel{\text{def}}{=} \begin{cases} S_{I}(\pi_{1},t) , & \text{if } S_{I}(\pi_{1},t) \neq \bot, \\ \varphi_{5}(I,t) , & \text{if } r_{5}(I,t) < \infty \text{ and } W_{5}(S'_{I},\pi_{1},r_{5}(I,t),t) < e_{5}, \\ \varphi_{2}(I,t) , & \text{if } r_{2}(I,t) < \infty \text{ and } W_{2}(S'_{I},\pi_{1},r_{2}(I,t),t) < e_{2}, \\ \varphi_{3}(I,t) , & \text{if } r_{3}(I,t) < \infty \text{ and } W_{3}(S'_{I},\pi_{1},r_{3}(I,t),t) < e_{3}, \\ \bot , & \text{otherwise} \end{cases}$$

$$S'_{I}(\pi_{2},t) \stackrel{\text{def}}{=} \begin{cases} \varphi_{2}(I,t) , & \text{if } (S_{I}(\pi_{2},t,\tau_{2}) = 1) \text{ and } (S'_{I}(\pi_{1},t,\tau_{2}) = 0) \text{ and } \\ (W_{2}(S'_{I},\pi_{1},r_{2}(I,t),d_{2}(I,t)) + W_{2}(S'_{I},\pi_{2},r_{2}(I,t),t) < e_{2}), \\ \varphi_{3}(I,t) , & \text{if } (S_{I}(\pi_{2},t,\tau_{3}) = 1) \text{ and } (S'_{I}(\pi_{1},t,\tau_{3}) = 0) \text{ and } \\ (W_{3}(S'_{I},\pi_{1},r_{3}(I,t),d_{3}(I,t)) + W_{3}(S'_{I},\pi_{2},r_{3}(I,t),t) < e_{3}), \\ \varphi_{5}(I,t) , & \text{if } (S_{I}(\pi_{2},t,\tau_{5}) = 1) \text{ and } (S'_{I}(\pi_{1},t,\tau_{5}) = 0) \text{ and } \\ (W_{5}(S'_{I},\pi_{1},r_{5}(I,t),d_{5}(I,t)) + W_{5}(S'_{I},\pi_{2},r_{5}(I,t),t) < e_{5}), \\ \bot , & \text{otherwise} \end{cases}$$

**Lemma 4**  $S_I'$  is valid on  $\Pi$  for any I with respect to jobs of  $\tau^{\mathrm{example}} \setminus \{\tau_6\}$ .

**Proof:** Schedule  $S_I'$  is obviously valid for the jobs generated by  $\tau^{\text{example}} \setminus \{\tau_6\}$  in instance I. Each job, by definition of  $S_I'$  above only executes within its scheduling window, does not execute concurrently with itself on both processors, and executes exactly for its execution requirement.

## 5.3.3 Step 3: Properties of Schedule $S_I'$

If  $S_I'$  does not have sufficient idle time to schedule  $\tau_6$  entirely on processor  $\pi_2$ , then there must exist a job  $J_6 \in I$  that does not meet its deadline, with respect to the idle time in schedule  $S_I'$ . In this section, we prove several lemmas which characterize the properties of schedule  $S_I'$  with respect to the  $J_6$ 's scheduling window. The main observation from these properties is that the jobs of I are constrained in how their scheduling windows intersect, if  $J_6$  cannot be scheduled in  $S_I'$ . We will exploit these intersection constraints on job in the next section (Step 4) when we define schedule  $S_I''$ .

Let  $A_6$  be the arrival of  $J_6$ . Since the relative deadline of  $\tau_6$  is  $d_6 = 8$ , the scheduling window of  $J_6$  is  $[A_6, A_6 + 8)$ . We will start by making an observation on the maximum possible amount that jobs of  $\tau^{\text{example}} \setminus \{\tau_6\}$  could execute in any schedule over an interval of length six, eight, and ten. These observations will be useful to reason about the amount of work that could occur over the scheduling windows of jobs of  $\tau_5$  and  $\tau_6$ .

**Observation 1** Table 1 presents upper-bounds on  $W_i(S, \pi_1, t, t + L) + W_i(S, \pi_2, t, t + L)$  for intervals of length  $L \in \{6, 8, 10\}$  for any valid schedule S, task  $\tau_i \in \tau^{\mathrm{example}} \setminus \{\tau_6\}$  and time-instant t. The upper bounds for L = 8 and L = 10 may easily be observed by noting that  $\tau_1$ ,  $\tau_2$ , and  $\tau_3$  have at most two jobs with scheduling windows that intersect with an interval [t, t + L) for  $8 \le L \le 10$ , and  $\tau_4$  and  $\tau_5$  can have at most one job with scheduling window intersecting [t, t + L). Similarly, for L = 6, at most two jobs of  $\tau_1$ ,  $\tau_2$ , and  $\tau_3$  and a single job of  $\tau_4$  and  $\tau_5$  may over lap with the interval [t, t + 6); however, the maximum intersection between the scheduling windows of  $\tau_1$ 's jobs and [t, t + 6) is three, due to the fact that  $p_1$  equals five. We also point out that upper bounds on  $W_i(S, \pi_1, t, t + L) + W_i(S, \pi_2, t, t + L)$  are monotonically non-decreasing with L.

| Task    | $\geq W_i(S, \pi_1, t, t + L) + W_i(S, \pi_2, t, t + L)$ |     |        |  |

|---------|----------------------------------------------------------|-----|--------|--|

|         | L=6                                                      | L=8 | L = 10 |  |

| $	au_1$ | 3                                                        | 4   | 4      |  |

| $	au_2$ | 2                                                        | 2   | 2      |  |

| $	au_3$ | 2                                                        | 2   | 2      |  |

| $	au_4$ | 2                                                        | 2   | 2      |  |

| $	au_5$ | 2                                                        | 2   | 2      |  |

Table 1. Upper bounds on the execution of tasks over intervals [t, t + L) for various values of L.

The first property we show for  $S_I'$  is in regard to the execution of jobs of  $\tau_5$  over the  $J_6$ 's scheduling window of  $[A_6, A_6 + 8)$ . If there was not sufficient idle time in  $S_I'$  to completely schedule  $J_6$ , a job of  $\tau_5$  must have its scheduling window intersect with  $[A_6, A_6 + 8)$ . Furthermore, a job of  $\tau_5$  must execute for a non-zero amount of time on processor  $\tau_2$  over  $[A_6, A_6 + 8)$ . The following lemma formally shows this property.

**Lemma 5** If  $S'_I$  does not have sufficient idle time over  $[A_6, A_6 + 8)$  to completely execute  $J_6$ , then there exists a single job  $J_5 \in I$  of  $\tau_5$  with scheduling window  $[A_5, A_5 + 6)$  where

$$[A_5, A_5 + 6) \cap [A_6, A_6 + 8) \neq \emptyset.$$

(23)

Furthermore, let  $\alpha$  equal the execution of  $J_5$  on processor  $\pi_2$  over  $[A_5, A_5+6)$  (i.e.,  $\alpha \stackrel{\text{def}}{=} W_5(S_I', \pi_2, A_5, A_5+6)$ ). It must be that

$$\alpha > 0. \tag{24}$$

and that  $J_5$  executes for some non-zero amount of time  $\leq \alpha$  on  $\pi_2$  over  $[A_6, A_6+8)$  (i.e.,  $W_5(S_I', \pi_2, A_6, A_6+8) \leq \alpha$ ).

**Proof:** First note, that since the period of  $\tau_5$ ,  $p_5$ , equals 100, at most one job of  $\tau_5$  could possibly have its scheduling window intersect with the interval  $[A_6, A_6 + 8)$ . We will now show (by contradiction) that exactly one job of  $\tau_5$  intersects  $J_6$ 's scheduling window and executes during this interval on processor  $\pi_2$ . Assume the lemma is false: a job of  $\tau_5$  does not execute on processor  $\pi_2$  over  $J_6$ 's scheduling window in valid schedule  $S_I'$ . Then, exactly one of the following three cases is true:

- **Case 1** there does not exist a job  $J_5 \in I$  with  $[A_5, A_5 + 6) \cap [A_6, A_6 + 8) \neq \emptyset$ .

- Case 2 there exists a job  $J_5 \in I$  of  $\tau_5$  with  $[A_5, A_5 + 6) \cap [A_6, A_6 + 8) \neq \emptyset$ , but  $J_5$  does not execute on processor  $\pi_2$  over the interval  $[A_5, A_5 + 6)$  (i.e.,  $\alpha = 0$ ); or,

- Case 3 there exists a job  $J_5 \in I$  of  $\tau_5$  with  $[A_5, A_5 + 6) \cap [A_6, A_6 + 8) \neq \emptyset$  and  $J_5$  executes on processor  $\pi_2$  for  $\alpha > 0$  over the interval  $[A_5, A_5 + 6)$ , but does not execute over  $[A_6, A_6 + 8)$ ;

By construction of  $S_I'$ , the only other tasks of  $\tau^{\text{example}} \setminus \{\tau_6\}$ , other than  $\tau_5$ , that are executed on  $\pi_2$  in  $S_I'$  are  $\tau_2$  or  $\tau_3$ . Since  $J_6$ 's execution requirement,  $E_6$ , is 4, the execution of  $\tau_2$  and  $\tau_3$  on processor  $\pi_2$  in schedule  $S_I'$  over the interval  $[A_6, A_6 + 8)$  must exceed four for  $J_6$  to be unable to execute completely on  $\pi_2$ . However, by Observation 1, the most that  $\tau_2$  and  $\tau_3$  could execute over  $[A_6, A_6 + 8)$  is four. Thus,  $\tau_5$  must have executed on  $\pi_2$  over  $[A_6, A_6 + 8)$  in  $S_I'$  for some non-zero amount of time in order for  $J_6$  not to complete which contradicts the assumption of Cases 1, 2, and 3; the lemma follows.

The next lemma gives an upper bound on the amount of time that  $J_5$  can execute on processor  $\pi_2$  in schedule  $S'_I$ .

**Lemma 6** If  $S'_I$  does not have sufficient idle time over  $[A_6, A_6 + 8)$  to completely execute  $J_6$ , then

$$\alpha \le 1. \tag{25}$$

**Proof:** If there is insufficient time in  $S_I'$  to execute  $J_6$ , Lemma 5 states that a unique job  $J_5$  of task  $\tau_5$  must exist with a scheduling window  $[A_5, A_5 + 6)$  that intersects  $[A_6, A_6 + 8)$ . Observation 1 implies that an upper bound on the execution of jobs of  $\tau^A$  in  $S_I'$  over the interval  $[A_5, A_5 + 6)$  is at most five. Thus, the total amount of time that processor  $\pi_1$  is idle over  $[A_5, A_5 + 6)$  in the original schedule  $S_I$  is at least one.  $J_5$  executes on processor  $\pi_1$  at most  $2 - \alpha$ , by Lemma 5. Assume that  $\alpha > 1$ . Then,  $J_5$  executes on the processor  $\pi_1$  for strictly less than one time unit in schedule  $S_I'$ . Thus, there exists  $t \in [A_5, A_5 + 6)$  where  $S_I'$  is executing a job not in task  $\tau^A \cup \{\tau_5\}$  on processor  $\pi_1$ . However, the existence of execution of  $J_5$  on processor  $\pi_2$  contradicts the construction of  $S_I'$  which moves as much of  $J_5$ 's to  $\pi_1$  at instances whenever jobs of  $\tau^A$  are not executing. Thus, our assumption that  $\alpha > 1$  must be false and the lemma follows.

The next two lemmas (Lemmas 7 and 8) exactly characterize the jobs of  $\tau_3$  and  $\tau_2$  that must execute over  $J_6$ 's scheduling window.

**Lemma 7** If  $S_I'$  does not have sufficient idle time over  $[A_6, A_6 + 8)$  to completely execute  $J_6$ , then there exists exactly two jobs of  $\tau_3$ ,  $J_3^1$ ,  $J_3^2 \in I$  (where  $A_3^1 + 6 \le A_3^2$ ), such that

$$([A_3^1, A_3^1 + 2) \cap [A_6, A_6 + 8) \neq \emptyset) \wedge ([A_3^2, A_3^2 + 2) \cap [A_6, A_6 + 8) \neq \emptyset).$$

(26)

Furthermore, both  $J_3^1$  and  $J_3^2$  execute for strictly more than  $2 - \alpha$  time units on  $\pi_2$  in  $S_I'$  over  $[A_6, A_6 + 8)$  (i.e.,  $W_3(S_I', \pi_2, A_6, A_6 + 8) > 2 - \alpha$ ).

**Proof:** Since  $J_6$  cannot complete during the idle times in  $S_I'$ , the execution on processor  $\pi_2$  over the  $J_6$ 's scheduling window  $[A_6, A_6 + 8)$  must exceed four time units; otherwise,  $J_6$  could complete entirely on processor  $\pi_2$ . By definition of  $S_I'$ , only jobs of  $\tau_2$ ,  $\tau_3$ , and  $\tau_5$  execute on processor  $\pi_2$ . Observation 1 implies that  $\tau_2$  can execute for at most two time units over  $[A_6, A_6 + 8)$ . By Lemma 5 and Lemma 6,  $J_5$  executes for amount of time at most  $\alpha \leq 1$  time units over  $J_6$ 's scheduling window on processor  $\pi_2$ . Thus,  $\tau_3$  must execute for strictly more than  $2 - \alpha$  time unit over  $[A_6, A_6 + 8)$  on  $\pi_2$  in  $S_I'$ . Since the execution requirement  $e_3$  is one, there must be at least two jobs of  $\tau_3$  that execute during  $[A_6, A_6 + 8)$ . The period and relative deadline parameter of  $\tau_3$  ( $p_3 = 6$  and  $d_3 = 2$ ) imply that at most two jobs of  $\tau_3$  can execute in  $[A_6, A_6 + 8)$ . Let  $J_3^1$  and  $J_3^2$  be the jobs of  $\tau_3$  that execute in  $[A_6, A_6 + 8)$  where  $A_3^2 - A_3^1 \geq 6$  (by the period parameter). The fact that  $J_3^1$  and  $J_3^2$ 's scheduling windows overlap with  $J_6$ 's scheduling window implies Equation 26.

**Lemma 8** If  $S_I'$  does not have sufficient idle time over  $[A_6, A_6 + 8)$  to completely execute  $J_6$ , then there exists exactly two jobs of  $\tau_2$ ,  $J_2^1$ ,  $J_2^2 \in I$  (where  $A_2^1 + 5 \le A_2^2$ ), such that

$$([A_2^1, A_2^1 + 1) \cap [A_6, A_6 + 8) \neq \emptyset) \wedge ([A_2^2, A_2^2 + 1) \cap [A_6, A_6 + 8) \neq \emptyset).$$

(27)

Furthermore, both  $J_2^1$  and  $J_2^2$  execute for strictly more than  $2-\alpha$  time units on  $\pi_2$  in  $S_I'$  over  $[A_6,A_6+8)$  (i.e.,  $W_2(S_I',\pi_2,A_6,A_6+8)>2-\alpha$ ).