Gui CY, Zheng L, He BS  $et\ al.$  A survey on graph processing accelerators: Challenges and opportunities. JOURNAL OF COMPUTER SCIENCE AND TECHNOLOGY

# A Survey on Graph Processing Accelerators: Challenges and Opportunities

Chuang-Yi Gui<sup>1</sup>, Student Member, CCF, Long Zheng<sup>1,\*</sup>, Member, CCF, ACM, IEEE

Bing-Sheng He<sup>3</sup>, Senior Member, IEEE, Member, ACM, Cheng Liu<sup>2,3</sup>, Xin-Yu Chen<sup>3</sup>

Xiao-Fei Liao<sup>1</sup>, Senior Member, CCF, Member, IEEE and Hai Jin<sup>1</sup>, Fellow, CCF, IEEE, Member, ACM

$E-mail: \{chygui, longzh\}@hust.edu.cn; hebs@comp.nus.edu.sg; liucheng@ict.ac.cn; xinyuc@comp.nus.edu.sg; \{xfliao, hjin\}@hust.edu.cn \} \\$

Received July xx, 2018; revised January xx, 2019.

Abstract Graph is a well known data structure to represent the associated relationships in a variety of applications, e.g., data science and machine learning. Despite a wealth of existing efforts on developing graph processing systems for improving the performance and/or energy efficiency on traditional architectures, dedicated hardware solutions, also referred to as graph processing accelerators, are essential and emerging to provide the benefits significantly beyond those pure software solutions can offer. In this paper, we conduct a systematical survey regarding the design and implementation of graph processing accelerator. Specifically, we review the relevant techniques in three core components toward a graph processing accelerator: preprocessing, parallel graph computation and runtime scheduling. We also examine the benchmarks and results in existing studies for evaluating a graph processing accelerator. Interestingly, we find that there is not an absolute winner for all three aspects in graph acceleration due to the diverse characteristics of graph processing and complexity of hardware configurations. We finially present to discuss several challenges in details, and to further explore the opportunities for the future research.

Keywords graph processing, domain-specific architecture, performance, energy efficiency

#### 1 Introduction

For a wide variety of applications, e.g., date science, machine learning, social networks, roadmap and genomics, graph is expressive to represent the inherent relationships between different entities. Therefore, graph processing has become a hot topic for solving many real-world problems in both academia and industry. With the growing development of Internet of

Things and cloud computing, the size and complexity of graphs are still expanding. This poses great challenges for modern graph processing eco-systems in both performance and energy efficiency.

There are a large number of studies that attempt to use software solutions to improve the performance and energy efficiency of graph processing. From distributed computing environment<sup>[1,2]</sup>, to single highend server<sup>[3]</sup>, to the commodity personal computer<sup>[4,5]</sup>,

<sup>&</sup>lt;sup>1</sup>National Engineering Research Center for Big Data Technology and System/Services Computing Technology and System Lab/Cluster and Grid Computing Lab, School of Computer Science and Technology, Huazhong University of Science and Technology, Wuhan, 430074, China

<sup>&</sup>lt;sup>2</sup>Institute of Computing Technology, Chinese Academy of Sciences, Beijing, 100190, China

<sup>&</sup>lt;sup>3</sup>School of Computing, National University of Singapore, 117418, Singapore

Survey Paper

This work is supported by the National Key Research and Development Program of China under Grant No. 2018YFB1003502, National Natural Science Foundation of China under Grant Nos. 61825202, 61832006, 61628204 and 61702201, and China Postdoctoral Science Foundation Grant Nos. 2018T110765 and 2018M630862.

<sup>\*</sup>Corresponding Author

<sup>©2019</sup> Springer Science + Business Media, LLC & Science Press, China

these systems basically make tremendous efforts on software optimizations for programmability, high performance and scalability under traditional architectures. In an effort to accelerate graph workloads, multicore CPUs and GPUs have been recently adopted to expose a high degree of parallelism for high perfromance graph iteration, e.g., Medusa<sup>[6]</sup>, Cusha<sup>[7]</sup>, GunRock<sup>[8]</sup>, Frog<sup>[9]</sup>, MapGraph<sup>[10]</sup> and Enterprise<sup>[11]</sup>.

Despite a large number of software solutions, the potentials of graph processing on performance and energy efficiency are still bounded to current hardware architectures. Real-world graphs often follow a power-law distribution in the sense that most of vertices are associated with a few edges, leading to the fact that prohibitive memory access overhead and low efficiency have occurred on general-purpose processors<sup>[12–15]</sup>. The irregularity in graph processing inherently fall short in exploiting memory- and instruction-level parallelism on traditional processors. It is also observed in the previous studies that a wealth of memory bandwidth is actually under-utilized for graph processing on existing commodity multi-core architectures<sup>[15–18]</sup>.

Though GPUs have demonstrated compelling performance on graph processing<sup>[6–8, 19]</sup>, they still suffer from key issues in terms of control and memory divergence, load imbalance and superfluous global memory accesses. More important is that CPUs and GPUs are known for relatively high energy consumption. With the end of Moore's law, using pure software solutions on traditional architectures is often extremely-difficult to fill the significant gap between the general-purpose architectures and the graph-specific computation for seeking the top performance of graph processing.

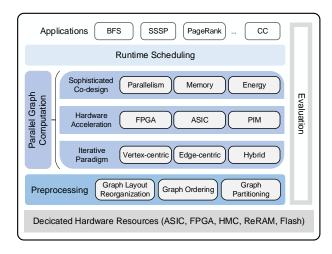

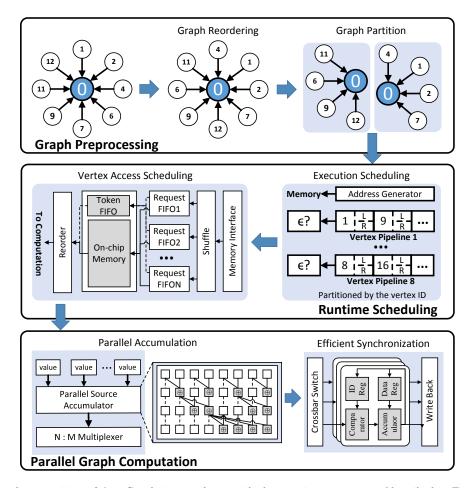

Fig.1. Building blocks for graph processing accelerators (with three major aspects: preprocessing, parallel graph computation and runtime scheduling)

For graph processing, architectural innovation is imperative. Hennessy and Patterson have also identified the importance, trend and opportunities of Domainspecific Architecture (DSA) in their recent technical report<sup>[20]</sup>. It is pointed out that open sourced architectural implementations<sup>®</sup> are the key for the innovations on hardware design<sup>[21]</sup>. The agile chip development can also shorten the development cycle for DSA prototypes<sup>[22]</sup>. These guidelines provide one of most effective means for driving the rapid development of graph processing-specific accelerators. At this point, hardware platform templates, e.g., Field Programmable Gate Array (FPGA) and Application-specific Integrated Circuit (AISC), are in line with the demand of the times. A large number of industries have already deployed their services on these beneficial hardware platforms for top performance and energy efficiency. For instance, FPGAs have been used in Microsoft datacenter for energy efficiency improvement<sup>[23]</sup>.

Specifically in terms of graph processing, it has been also witnessed that a large number of relevant studies build their graph processing accelerators based on  $FPGA^{[24-28]}$  and  $ASIC^{[16,29-31]}$ . Evaluation on these

<sup>&</sup>lt;sup>①</sup>http://www.riscv.org, Jan. 2019.

accelerators has also demonstrated the efficiency and effectiveness of DSA design $^{[16,28,32]}$ .

It is time to review the past and present of graph processing accelerators, and further look into their future development. In this paper, we conduct a systematic review on graph processing accelerators. It aims at exploring the key issues in the design and implementation of graph processing accelerators. As summarized in Fig.1, we have identified a complete set of core components for graph processing accelerator, which involves three major aspects: preprocessing, graph parallel computation and runtime scheduling.

- Preprocessing. Graph processing accelerator often has the limited storage resources. Graphs are needed to be partitioned. Preprocessing is an important component that operates on graph data for trying to make graph dataset fit into the memory capacity of graph accelerator. It is also the key to match a certain processing model and appropriate graph representation before the formal processing.

- Parallel Graph Computation. Parallel graph computation component serves as the main execution part of graph processing accelerator design. Iterative paradigm is often chosen to define a basic execution pattern for graph iteration that will be mapped to a pipelined hardware circuit. The implementation of this part generally relies on some hardware platform, e.g., FPGA, ASIC, and Processing-In-Memory (PIM). Different specifications have different concerns on hardware designs and sophisticated software co-designs for high throughput and energy efficiency.

- Runtime Scheduling. This part aims at how to schedule a large number of graph computational operations

on a finite set of hardware resources of graph processing accelerators. The basic metrics for runtime

scheduling are to guarantee the correctness and efficiency of graph iteration. The runtime scheduling component often involves data communication, execution mode and scheduling scheme.

Based on aforementioned three aspects, we carefully examine the benchmarks and results of existing studies. We find that there is not a clear winner for all these aspects in graph acceleration because of the diverse characteristics of graph processing and the complexity of hardware configureations. We therefore present and discuss several challenges in details, and to further explore the opportunities for the future research. One of the major challenges in the existing graph processing accelerators is that the programmability is an important issue for users to express their graph applications. Existing graph processing accelerators typically require labor-intensive efforts for hardware level modifications.

Great challenges come with great opportunities. Widespread graph applications have a strong demand for energy-efficient graph processing accelerators. Emerging memory devices, e.g., Hybrid Memory Cube (HMC)<sup>[33]</sup>, High Bandwidth Memory (HBM)<sup>[34]</sup>, Resistive Random Access Memory (ReRAM)<sup>[35]</sup> along with new processing devices, provide us with great opportunities to explore new schemes for graph processing. We believe that this survey summarizes those challenges and opportunities, which can help realize the accelerators with novel hardware-software co-designs.

The rest of this paper is organized as follows: Section 2 includes an introduction to basic components of graph processing, and briefly summarizes the recent progress on CPUs and GPUs. Section 3 presents some considerations in preprocessing phase. Design and implementation of parallel graph computation are reviewed in Section 4. Section 5 describes the runtime and scheduler part of graph accelerators. Emerging

graph accelerators are reviewed and compared in Section 6. Challenges and opportunities are given in Section 7. Finally, we conclude our work in Section 8.

#### 2 Preliminaries

In this section, we first give a brief introduction to the preliminaries of graph processing, including graph representation and several common graph algorithms. Next, we summarize some unique characteristics of graph processing, followed by the related work of graph processing on commodity general-purpose processors. The characteristics of graph processing and the related work further motivate our survey work on graph processing accelerators.

# 2.1 Graph Representation

Graph is a data structure consisting of vertices that are further associated with edges. A graph can be typically defined as G = (V, E) where V represents the vertex set and E indicates the edge set. For a directed graph, an edge can be represented as  $e = (v_i, v_j)$ , indicating that there is an edge pointing from  $v_i$  to  $v_j$ . In particular, vertex and edge can be also attributed with a single or multiple attributes. Real-world natural graphs, e.g., social networks, usually have the following three common features:

- Sparsity. The average number of vertex degrees is relatively small. The sparsity of graphs can result in poor locality for data accesses.

- Power-law Distribution. A few vertices have associated most of the edges. This can lead to severe work-load imbalance issue with a large number of date conflicts when high-degree vertices are being updated.

- Small-world Structure. Two arbitrary vertices in the graph can be connected with only a small number

of hops. The small-world feature will make it difficult for partitioning the graph efficiently (as will be discussed in Subsection 3.3).

#### 2.2 Graph Algorithms

We review several common graph algorithms with different requirements in computation, communication and memory access. These graph algorithms are also widely studied for the exprimental evaluation in the previous studies<sup>[12, 13, 17]</sup>.

Breadth-First Search (BFS) is a basic graph traversal algorithm, which is used as the kernel of Graph500 benchmarks. The neighboring vertices are iteratively accessed from the root vertex until all vertices of the graph are visited.

Single Source Shortest Path (SSSP) is another graph traversal algorithm that computes the shortest paths from a source vertex to other vertices. Different from BFS, it has less number of redundant computations in checking edges. Each vertex may be activated more than once. Therefore, it needs more memory space than BFS.

Betweenness Centrality (BC) is widely used to measure the importance of a vertex in a graph. The betweenness centrality value of a vertex is calculated by the ratio of shortest paths between any other two vertices. BC algorithm requires to compute the shortest paths between all pairs of vertices.

PageRank is one of the most popular algorithms, which calculates the scores of websites<sup>[36]</sup>. It maintains a PageRank value for each vertex. All the vertices are activated in each iteration. It often needs large memory bandwidth and float point computing ability.

Connected Components (CC) is widely used in image regions analysis and clustering applications. Each vertex maintains a label. If vertices are in the same connected region, their labels are set to the same. The

algorithm updates the labels of all vertices iteratively until converged.

Triangle Counting (TC) is used to measure the number of triangle cliques in the graphs. Each vertex maintains a list of neighbors, and iteratively checks if there are shared neighbors between each connected vertices pair. Number of triangles is calculated by the overlaps.

Graph Coloring (GC) is to assign colors to the vertices of a graph so that any two adjacent vertices have different colors. GC can be used in many areas, e.g., traffic scheduling, register allocation during compiling and pattern matching. Basic GC algorithm iteratively colors an active vertex with the color that has not been assigned on any of its neighbours.

Collaborative Filtering (CF) is an important machine learning algorithm used for recommendation. Given a bipartite graph where edge values represent the ratings and vertices correspond to the users and items, CF runs iteratively on the bipartite graph to find latent features for each vertex, with all the vertices active in each iteration.

K-core Decomposition (kCore) is widely used for structure analytics for large cloud networks. This algorithm iteratively removes all the vertices with degrees less than k such that k-core subgraphs in each all vertices have degree at least k are build.

Minimal Spanning Tree (MST) extracts a tree containing all the vertices from an edge-weighted graph with minimum weight. MST is popular in cable network construction, cluster analysis and circuit design. Prim's greedy MST algorithm iteratively chooses the minimum weight edge between vertices in and out of the spanning tree to construct the MST.

# 2.3 Unique Features of Graph Processing

As discussed previously, real-world graphs have the "power-law" distribution and "small-world" feature.

Besides, graph algorithms differ in computational and memory access requirements. Graph processing generally manifests the unique features as follow.

- Intensive Data Access. On the one hand, graph applications usually lead to a large number of data access requests. On the other hand, graph processing has a high data-access-to-computation ratio. That is, most of the operations in graph processing are related to data accesses.

- Irregular Computation. Due to the power-law distribution, computation workloads for different vertices may vary in a large scale. This will cause severe workload imbalance issue and communication overhead.

- Poor Locality. Data accesses of graph processing are usually random because each vertex may connect to any other random vertices. This feature often leads to heavy overhead of memory accesses.

- High Data Dependency. The data dependency is caused by the nature of connections of vertices in graph. Heavy dependencies make it difficult to explore the parallelism in graph processing. This may cause frequent data conflicts.

# 2.4 Brief Introduction to Graph Processing on Modern Commodity Processors

Many graph processing systems have been explored on modern commodity general-purpose processors, e.g., CPUs and GPUs. We briefly introduce the related work to motivate our study, and refer readers to recent surveys for more details<sup>[37–39]</sup>.

Graph Processing on CPUs. There is a large amount of work that aims at building an efficient system for graph applications on CPUs. Basically, they can be divided into two categories. The first kind is the distributed systems<sup>[40–45]</sup>, which leverage the clusters to support massive graph data. However, this

usually suffers from communication overhead, synchronization overhead, fault tolerance and load imbalance issues<sup>[46–49]</sup>. Emerging servers can hold most of the graph data in the large main memory. Thus, there is an amount of work that exploits the potential of single machine<sup>[3,50–52]</sup>. There are also many disk-based graph processing systems<sup>[4,5,53–56]</sup> which can avoid parts of the challenges in the distributed systems. Recently, Many Integrated Core (MIC) architecture based processors are also explored to improve the performance and efficiency of graph processing<sup>[57]</sup>.

Graph Processing on GPUs. GPU is adopted to pursue high performance of graph processing due to its data parallel capability. A number of graph processing systems with GPUs<sup>[6–8,58]</sup> have been proposed for high-performance graph processing. Enterprise<sup>[11]</sup> is developed to accelerate the performance for BFS algorithm only. There is also plenty of work on accelerating CC algorithm<sup>[59]</sup>, BC algorithm<sup>[60,61]</sup> and SSSP algorithms<sup>[62]</sup>. Domain-specific graph processing frameworks have been presented to provide high efficiency for the development on GPUs<sup>[63]</sup>. To support large-scale of graphs, hybrid CPU-GPU systems<sup>[64,65]</sup>, multi-GPUs systems<sup>[19,66]</sup> and out-of-memory systems<sup>[67,68]</sup> have been proposed.

Remarks. Despite a significant amount of effort in improving the graph processing performance on general-purpose processors, e.g., CPUs and GPUs, existing graph systems are still far from ideal to exploit the hardware potential of general-purpose processors<sup>[15, 16]</sup>. This is due to a significant gap between the general-purpose architectures and the unique features of graph processing. The graph processing accelerator is necessary as an alternative approach that might be able to fill this gap.

Nevertheless, existing studies on CPUs and GPUs have a wealth of experiences in designing graph accelerators (as discussed in the previous studies<sup>[28–30,32]</sup>). Various kinds of software graph processing models have been proposed to effectively express graph applications in a generic framework. Partitioning methods, out-of-memory processing and hybrid architectures schemes have been explored to support large-scale graphs.

We next illustrate three aspects of core components of graph accelerators, including preprocessing, parallel graph computation and runtime scheduling.

## 3 Graph Preprocessing

The data size of real-world graphs can easily exceed the on-chip/board memory capacity of graph processing accelerators which is a significant challenge for accelerators. This issue can cause large amounts of I/O and communication cost. In order to make data access efficient, preprocessing of graph data is often required to adapt the data structure onto the target graph accelerators. In this section, we will review the following major graph preprocessing methods used in the designs of graph processing accelerators.

- Graph Layout Reorganization. Graph layout is an

important factor to affect the graph processing efficiency. Most previous studies have attempted to

reorganize the layout to improve data accessing efficiency from many distinct aspects, e.g., data locality,

memory storage, and memory access patterns.

- Graph Ordering. Graph ordering aims to change the order of the vertices or the edges, such that data locality with less data conflicts can be obtained while the structure of the graph remains the same<sup>[27,69]</sup>.

- Graph Partitioning. Graph partitioning is to divide a large graph into multiple disjoint small subgraphs. It usually allows parallel processing of the sub graphs.

The processing on each sub graph has most of data

accesses on the corresponding graph partition. This is particularly useful for improving the cache locality or when the memory of the accelerator cannot hold the entire graph.

# 3.1 Graph Layout Reorganization

We will introduce the baseline graph layouts first. There are generally two widely-used categories of baseline graph layouts, i.e., edge array and compressed adjacency list. In graphs based on the edge array, each element of the array contains a pair of integers, i.e., source vertex index and destination vertex index. It is convenient to read the edges sequentially from memory. The edge array layout remains widely used in many graph processing systems, especially for the edge-centric processing systems. Another improved edge array layout is Coordinate List (COO). It has been widely adopted in graph accelerators<sup>[27,28,70]</sup>. It has the edge attributes that are stored along with the edges.

Compressed adjacency list graph originates from the adjacency matrix. It typically uses three arrays to store the graphs, i.e., the vertex property array of the graph, the edge array with the edges' outgoing/incoming vertex indices only, and the edge array starting indices of each vertex in the graph. Suppose outgoing edges are used in the edge array, We name this adjacency list format Compressed Sparse Row (CSR). If incoming edges are used in the edge array, this layout is called Compressed Sparse Column (CSC). The compressed adjacency list graph is relatively compact and beneficial to many graph accelerators<sup>[29,71]</sup>. Note that the edges of each vertex are stored sequentially.

Based on the baseline graph layouts, we have also many novel methods to compress the data size and optimize memory access further.

Combining Information. Existing work tends to combine multiple information in the same file of graph

data layout so that the data locality can be optimized, and random memory access can be reduced.

For instance, [72] proposes to associate the destination vertex property with the edge information such that the vertex property can be sequentially accessed to edges with a good locality. Authors in [25] opt to modify the row pointer array representation in a typical CSR format. They combine the vertex status (1 bit for BFS only) and the vertex's neighboring information in an element of the array. This method improves the memory access efficiency significantly.

Encoding Index. Using an encoding method can compress the graph layout to a small size. Thus, large graphs can be processed on a single accelerator. This is usually done for the index of vertices and edges.

For example, GraphH<sup>[73]</sup> proposes to squeeze the blank vertex indices by re-indexing the vertices of the graph when the number of vertices is smaller than the maximum vertex index. The index can also be compressed by grouping them with a coarsen id and using less bits to represent the same graph as presented in [16,28]. It is also possible to reduce the edge information with frequency-based encoding<sup>[74]</sup>.

Remarks. The baseline graph layouts are useful towards graph accelerators, but they can still be improved for different memory system designs in hardware accelerators. We still have the potential to explore the graph layouts at the aspects of data locality, memory access patterns, and memory footprint.

# 3.2 Graph Ordering

A number of graph ordering methods have been explored and demonstrated to be effective.

Index-aware Ordering. It typically targets at the edge array layout. The basic idea is to sort the edges based on either the source vertex indices or the destination vertex indices. Sorting the edges in an as-

cending manner generally improves the data locality because the neighboring vertex property can be prefetched and probably reused<sup>[73]</sup>. In the graph processing, source vertex property will be read and destination vertex property will be updated accordingly. Therefore, reading overhead can be reduced if the edges are sorted by source vertices. Similarly, the writing process can be more efficient if the edges are sorted by the destination vertices<sup>[27]</sup>. As demonstrated in [16, 26, 28], a hybrid index-aware sorting method that balances both the source vertices and destination vertices can outperform the methods that only consider the source vertex or the destination vertex.

Degree-aware Ordering. This method takes the vertex degree as the sorting metric. Sorting the vertices based on vertex degree in descending order brings multiple benefits<sup>[74]</sup>. As high-degree vertices are more likely to be accessed, good data locality can be observed if high-degree vertices are placed nearby. In addition, it balances the workloads as well<sup>[75]</sup> when the graph is processed in parallel. The degree-aware ordering method applies to both baseline graph layouts<sup>[76]</sup>, i.e., the edge array and the compressed adjacency list.

Conflict-aware Ordering. This method is to reduce the data access conflict during parallel graph processing. ForeGraph<sup>[28]</sup> proposes to interleave the edges such that memory level parallelism can be explored more efficiently. Different from the interleaving method, AccuGraph<sup>[15]</sup> reorders the edges of the whole graph such that the destination vertices of the edges read in each cache line are distributed evenly over the on-chip memory banks. In this case, the parallel destination vertex updating has fewer conflicts.

Remarks. Graph ordering methods focus on changing the order of the graph data organization. The reordered graph can be directly used by the graph accelerators without any modification. Nevertheless, the

graph ordering usually requires global sorting and the pre-processing overhead, which can be costly.

# 3.3 Graph Partitioning

Graph partition makes it possible to fit the graph into the limited on-chip memory of a graph accelerator. The major graph partition strategies in graph accelerator designs can be roughly divided into four categories as shown in Table 1.

Table 1. Partitioning Schemes of Graph Accelerators

| Partitioning Schemes | Graph Accelerators           |

|----------------------|------------------------------|

| Source-Oriented      | [15, 27, 69, 77–80]          |

| Destination-Oriented | [16, 26, 30, 73, 81]         |

| Grid                 | [28, 70, 82]                 |

| Heuristic            | [29, 31, 32, 75, 76, 83, 84] |

Source-oriented Partition. The source-oriented partition methods typically have disjoint source vertices in each partition. All outgoing edges are associated with the partition's source vertices. The destination vertices will be included in the corresponding partition. Particularly, the source vertex indices in each partition are usually continuous to ensure sequential memory accesses. With the source-oriented partition, it is convenient to determine the partitions that need the updated vertex property in the graph processing. Nevertheless, different partitions may be in conflict with destination vertex update. To address this problem, [27] proposes to synchronize through messages and resolve the data dependency through a specific computing unit.

Destination-oriented Partition. The destination-oriented partition is similar to the source-oriented partition. Basically the partitions have disjoint destination vertices. Therefore, each partition can be updated independently while reading the source vertex property for each partition is mostly random. Graphicionado<sup>[16]</sup>

adopts this partition method to ensure that each partition can be fitted to the small scratchpad memory. Low-latency high-bandwidth scratchpad memory can be fully utilized. GraphP<sup>[81]</sup> also applies this partition. They aim at reducing the communication between the partitions on different accelerators such that the communication among the HMC cubes can be improved.

Grid Partition. The grid partition of graph in graph processing systems was first introduced in GridGraph<sup>[55]</sup> which presented an efficient graph data layout and was widely absorbed into designs for graph processing accelerators<sup>[28,70]</sup>. Grid partition is essentially a two-dimensional partition method, which can be considered an extension of the one-dimensional partition, like source-oriented partition and destinationoriented partition<sup>[28,70]</sup>. First, it divides both the source vertices and the destination vertices into continuous segments. Then it forms a two-dimensional array of cubes. Each cube includes the source vertex set, the destination vertex set, and all the edges whose source vertex and destination vertex belong to the source vertex set and destination set, respectively. The grid partition produces finer grained partitions. The partitions have both sequential source vertices and destination vertices. ForeGraph<sup>[28]</sup> uses this method to make best use of the limited on-chip memory of FPGAs. In particular, it optimizes the read order of partitions such that the partition loading and processing can be overlapped. This method is also used in GraphR<sup>[70]</sup> and helps explore the ReRAM features for both high-performance low-power graph acceleration.

Heuristic Partition. Unlike the above partition methods, many heuristic graph partition methods have been intensively explored, especially for conventional CPU-based graph processing systems. These partition methods follow various heuristic metrics to reduce the communication, to improve locality, or to provide bet-

ter load balance. Some of them are also applied for the graph accelerator design. For example, a hash-based partition algorithm is used to achieve partitions with balanced vertices and edges in [29]. A clustering-based partition algorithm is adopted for better locality in [76]. A multi-level partitioning algorithm is adopted in FASTCF<sup>[75]</sup> and is also demonstrated to be efficient for stochastic-gradient-descent-based collaborative filtering.

**Remarks.** Graph partition brings multiple benefits to graph accelerator design. In particular, it allows the graph accelerator to explore the small yet low-latency high-bandwidth on-chip memory.

Graph preprocessing benefits the graph accelerator on many aspects including better data locality, more efficient memory access patterns, higher task-level parallelism, and even fewer memory accesses. In general, it is a critical step to improve the performance of the graph processing accelerators, and even affects the accelerator design choices. While some preprocessing approaches are extremely time-consuming, it is still an open problem on how to achieve a better balance between the overhead and performance benefits in many practical scenarios as pointed out in [13].

#### 4 Parallel Graph Computation

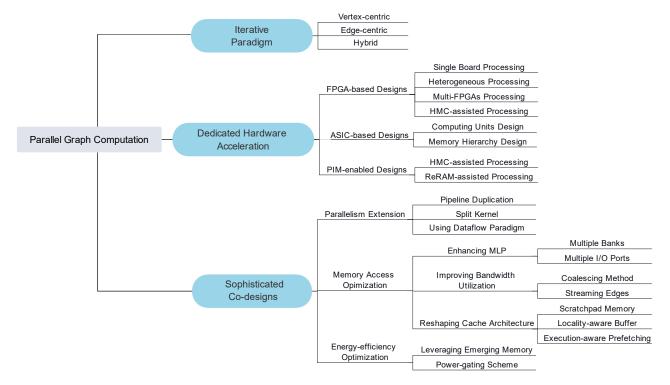

The core component of a graph processing accelerator is how to handle the preprocessed graph data in Section 3 with massive parallellism. Considering intertwined data dependencies of graphs, this often requires non-trivial technical innovation, involving matched parallel iterative paradigms, dedicated hardware acceleration and sophisticated co-codesigns. Fig.2 outlines the taxonomy of parallel graph computation.

• Iterative Paradigm. Iterative paradigm is used to express the process of how vertices and edges run. It

Fig.2. A taxonomy of parallel graph computation.

defines the basic data access and computational pattern of graph program. Typical iterative paradigms in existing graph accelerators can be categorized into three approaches: the vertex-centric approach, the edge-centric approach, and the hybrid approach. They decouple the associated dependencies within graphs as much as possible, and further explore the potential parallelism of graph processing.

- Dedicated Hardware Acceleration. Different kinds of dedicated hardware platforms can be used to accelerate graph analytics. Existing graph processing accelerators are basically built upon three types of hardware platforms: FPGA, ASIC, and PIM. These emerging architectures can be used to architect efficient memory hierarchy and computing units for higher performance and energy efficiency.

- Sophisticated Co-designs. Sophisticated co-designs usually combine the hardware and software optimizations to exploit the hardware potentials. They often

focus on three aspects: parallelism extension, memory access optimization, and energy efficiency optimization. Most of these co-designs can be commonly used on different kinds of hardware to achieve high performance and energy efficiency.

#### 4.1 Iterative Paradigm

Graph has complex data dependencies between vertices. Designing efficient iterative paradigms is important to decouple these associated dependencies as much as possible by exploring the common computational pattern surrounding vertices and/or edges. Existing iterative paradigms for graph processing can be basically divided into two subcategories: vertex-centric approach and the edge-centric approach. The vertex- and edge-centric approaches not only concern the expressiveness and abstraction of graph algorithms but also impact the design of graph data layout, preprocessing and computation. A few graph accelerators also have made a hybrid attempt for embracing the best worlds

of both modes. Table 2 summarizes the related work with different iterative paradigms.

Programming Model. Programming model is used for effectively express the graph algorithms. It abstracts the common operations in various graph algorithms and alleviates the effort for programmers to write their applications. According to the iterative paradigms, there are vertex-centric programming model and edge-centric programming model. These two models can be combined as the hybrid model to take advantages of both paradigms.

Table 2. Iterative Paradigms of Graph Accelerators

| Iterative Paradigm | Graph Accelerators                                                                       |

|--------------------|------------------------------------------------------------------------------------------|

| Vertex-Centric     | $\begin{bmatrix} 14 - 16, 25, 26, 29 - 32, 71, 74, 76, \\ 78, 81, 83 - 91 \end{bmatrix}$ |

| Edge-Centric       | [27, 28, 70, 72, 73, 75, 82, 92 – 94]                                                    |

| Hybrid             | [80]                                                                                     |

- Vertex-centric Programming Model. Graph algorithms expressed with this model handle the graphs by following "Think like a vertex" philosophy<sup>[1]</sup>. It describes a graph program for each vertex, including computational operations and data transmission between their neighbors via edges. Since each vertex is processed independently, parallelism can be therefore guaranteed by simultaneously scheduling these vertices without data dependencies.

- Edge-centric Programming Model. X-Stream<sup>[5]</sup> is the first work to use edge-centric programming model to handle graph edges. Unlike the vertex-centric model, this model describes a graph program for each edge. An edge is processed with three steps: 1) collect the information of its source vertices, 2) update its value, and 3) send this value to its destination vertices. It is clear that this model removes the random accesses to edges via sequential streaming of each edge to the chips.

• Hybrid Programming Model. Alternative is to use a hybrid method by switching between vertex- and edge-centric programming models for the purpose of taking advantages of both models<sup>[80]</sup>. The vertex-centric model is responsible for the situation when the active vertex ratio is relatively high. In contrast, the edge-centric model is intended to cope with the case that active vertex ratio is relatively low. Clearly, model switching decision can be made according to the active vertex ratio (among all vertices). The threshold can be decided by the ratio of bandwidth.

Data Layout Selection. Systems implemented in vertex-centric approach typically iterate over the active vertices and execute the vertex program on them at each iteration. For each given vertex, its neighbours are visited to complete the computation. This kind of implementation usually requires a fast scan for edges of given vertices. As a consequence, as presented in Section 3.1, the compressed adjacency lists (CSR/CSC) are suitable for vertex-centric model because the assoiated edges of a vertex can be found easily<sup>[4,29]</sup>.

Similarly for the edge-centric approach, which iterates over all the edges to implement the edge program for each of the edge, a fast sequential scan of edges is demanded. To process an edge, information of the end vertices also needs to be indexed directly. Therefore, the edge array presented in Section 3.1 is intuitively fit for systems in edge-centric approach<sup>[5, 27]</sup>.

Preprocessing Considerations. Initially, the graph data is usually stored in the disk as edge files where the edge is represented as a pair of corresponding source and destination vertices. During preprocessing phase, edge files are converted into the appropriate data layout according to programming models. As discussed in Section 3, preprocessing involves graph partitioning, reorganization and ordering. The complexity of preprocessing also varies for different data layouts.

For vertex-centric approach, the edge file is converted into the format of adjacency lists. Typically, the edges are sorted by source or destination vertex following by index creation that maintains the edge position in the edge array for each vertex. As for edge-centric approach, the edge array is usually loaded directly without specialized data formatting and conversion<sup>[5,27]</sup>. A detailed research about the cost on preprocessing is presented in [13]. Generally, the preprocessing cost on vertex-centric approach is higher than edge-centric one.

Computation Overhead. Vertex- and edge-centric approaches have different computation patterns as dissucssed before. In vertex-centric approach, the computation is executed for each vertex which iterates over the neighbors of a given vertex. In edge-centric approach, the edges are executed as a stream. At this point, the workload characteristics and cache (miss-rate) metrics are significantly different for two approaches<sup>[13]</sup>.

For workload analysis, vertex-centric approach supports selective scheduling on only a subset of vertices for each iteration while edge-centric approach requires a scan of the whole edges, which means that the edge-centric approach induces more computations than vertex-centric approach.

Cache behaviours are also different between these two approaches. In vertex-centric approach, the processed vertices can be (locally) cached while it introduces more random accesses by traversing the frontier. In edge-centric approach, edges can be prefetched for better use of cache, but it causes more random accesses to vertices. Their actual performance may be significantly different, and largely depends on the inherent topology of the graph and features of graph algorithms.

Generally, the vertex-centric approach introduces more random accesses to edges while the edge-centric approach causes more random accesses to vertices. To improve the cache behaviours, optimizations can be applied to these two models, e.g., organizing edge arrays into grids can improve the cache locality<sup>[55]</sup>.

**Discussions.** Table 3 compares different paradigms from multiple aspects. It is difficult to judge which approach is better because the performance is usually not the same case when different kinds of graph applications are introduced. The authors in [13] make a comprehensive comparison of these two approaches when different approaches and graph algorithms are included.

Vertex-centric paradigm has been widely used to drive many graph accelerators<sup>[16, 26, 29, 88]</sup>, because of its expressive potentials to easily represent various kinds of graph algorithms, and the high parallelism in the grain of vertex. However, in the vertex-centric paradigm, there can be random accesses to edges, resulting in potentially heavy memory access overhead.

Edge-centric paradigm is usually used by existing graph accelerators for improving the utilization of their limited memory bandwidth<sup>[27,28,75]</sup>. However, the point is that edge-centric paradigm is lack of flexible scheduling potential in contrast to the vertex-centric one. Almost all of edges have to be processed multiple times to complete the whole process. In addition, this paradigm may also lead to a large number of random accesses to vertices. Thus, additional optimizations are often cooperatively needed, e.g., fined grained partitioning and tailored vertex update strategies<sup>[28,70]</sup>.

For graph processing accelerators, the selection and design of iterative paradigm for graph processing accelerator must also ensure that: 1) programming is easy to use and understand for graph algorithm representation; 2) parallelism is easy to expose and exploit for high throughput and fast hardware development. It is also important to dedicate the accelerators according to the features of applications. Note that advantages can be combined by incorporating hybrid approaches into a

| Iterative Paradigm | Programming Model                       | Data Layout           | Preprocessing                                      | Computation Overhead                                              |  |  |

|--------------------|-----------------------------------------|-----------------------|----------------------------------------------------|-------------------------------------------------------------------|--|--|

| Vertex-centric     | Iterate over vertices                   | CSR/CSC               | Partitioning; Ordering;<br>Reindexing; Higher cost | frontier-based; random accesses to edges                          |  |  |

| Edge-centric       | Iterate over edges                      | Edge array/COO        | Partitioning; Ordering;<br>Lower cost              | All edges need to be<br>scanned; random ac-<br>cesses to vertices |  |  |

| Hybrid             | A mix of vertex- and edge-centric model | Mixed data structures | Sophisticated preprocessing                        | Model switch                                                      |  |  |

Table 3. Overview of Different Iterative Paradigms

design for better performance.

#### 4.2 Dedicated Hardware Acceleration

Existing graph processing accelerators can be built upon various kinds of hardware platforms. Typical hardware accelerators usually adopt only the traditional customized hardware platforms, i.e., FPGAs and ASICs, and have made few modifications on existing computing logic and memory architectures (e.g., DRAM). Some accelerators have re-built their architectures with in-situ computation without excessive data movement, e.g., HMC and ReRAM devices, which is also known as PIM-enabled accelerators. Different hardware configurations have different considerations for performance acceleration. We next review technical advances of these state-of-the-art graph processing accelerators.

#### 4.2.1 FPGA-based Designs

FPGA is an integrated circuit that enables designers to repeatedly configure digital logic in the fields after manufacturing, also called field-programmable. The configuration of FPGAs is generally specified via low-level hardware description languages, e.g., Verilog<sup>[95]</sup> and VHDL<sup>[96]</sup>. FPGAs are mostly adopted in graph processing accelerators.

Internal Characteristics of FPGAs. There are different kinds of programmable resources on FPGAs, e.g., programmable Logic Element (LE), Static Random Access Memory (SRAM), Flash and Block RAM (BRAM). However, the fact is that these resources are usually

limited to a small number. FPGA can offer high parallelism by architecting these resources with a pipelined Multiple Instructions Single Data (MISD) model. Multiple data can be processed simultaneously at different pipeline stages. Multiple pipelines can be easily duplicated for parallel processing.

Existing Efforts on FPGAs. A graph program is usually designed into a circuit kernel as the basic processing unit according to the programming model (as discussed in Section 4.1), which defines the execution pattern<sup>[75,87]</sup>. These kernels can be easily reconfigured on FPGAs for different algorithms. For building the efficient memory subsystem, a wide spectrum of previous studies make non-trival efforts for the efficient bandwidth utilization of on-chip BRAMs and the offchip memories. BRAMs provide high bandwidth and low memory latency for randomly accessed vertices. For improving the locality of vertices on the BRAM, fine grained partitioning and dedicated data placement strategies are needed to increase the reuse rate of vertices on the BRAM<sup>[26, 28, 74]</sup>. As for improving the utilization of off-chip bandwidth, edges can be streamed sequentially from the memory $^{[27]}$ .

A number of studies extend to integrate multiple FPGAs into a cluster so as to support large graphs<sup>[25,71]</sup>. FPGAs with integrated soft-cores are also presented, which can process the graphs in a distributed manner on a single FPGA board with high parallelism<sup>[84]</sup>. Heterogeneous architectures are also adopted where the FPGA and the CPU are connected

through cache-coherent interconnect. FPGA can access the host memory without the interruption of CPU. These two processors can easily cooperate with each other to process large graphs with higher parallelism than a single FPGA board<sup>[80]</sup>.

There are also a number of studies that aim at exploring the out-of-memory execution on FPGAs for large graphs. The data can be directly streamed from the disks or flashes to the processing units on the FPGA board in these scenarios<sup>[26, 28]</sup>. Recently, Near-Data Processing (NDP) is cooperatively used to enhance the power of FPGAs for graph processing by off-loading workloads to the integrated HMCs. This provides significantly high bandwidth and parallelism <sup>[71,76,97]</sup>.

# 4.2.2 ASIC-based Designs

ASIC is an integrated circuit composed of electrical components, e.g., resistors. It is usually fabricated on a wafer composed of silicon or other semiconductor materials that are customized for a particular use. ASICs are very compact, fast, and low power. Compared to FPGAs, their functions are hard-wired at the time of manufacture. It is not allowed to change the functionality of a small part of the circuit.

ASIC Designs for Graph Analytics. Due to the fixed circuit limitation, ASIC-based graph processing usually utilizes the expressive Gather-Apply-Scatter (GAS) model<sup>[40]</sup> to form the circuit<sup>[29,30]</sup>. Each phase is implemented as a hardware module, and runs in parallel with wires that connect different modules. In order to support various graph algorithms, a reconfigurable block can be integrated for users to define the update functions for flexibility.

As for the memory hierarchy, these graph accelerators commonly adopt the scratchpad memory to replace traditional cache. The scratchpad memory acts as a content addressable cache and can be controlled

manually. Graphicionado<sup>[16]</sup> uses the eDRAM as the scratchpad memory to store graph data that needs frequent random accesses, e.g., the destination vertices. Dedicated caches of different kinds of graph data are designed in [29] according to the access features. Since these memory resources can be tightly connected to the processing units in an efficient way, ASIC-based graph accelerators can achieve high throughput on the chip.

## 4.2.3 PIM-enabled Designs

Different from traditional hardware designs, research on PIM-enabled architectures usually adopts emerging paradigms for acheiving impressive performance results by integrating processing units into the memory. It can provide the extremely high bandwidth and low memory access latency with energy saving. The PIM-enabled acceleration is often implemented by leveraging emerging memory devices, e.g., HMC and ReRAM, both of which integrate the in-situ computation in the memory.

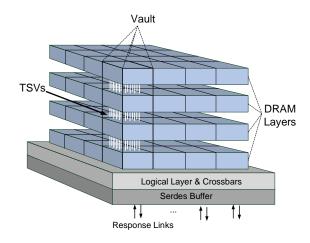

HMC-assisted Graph Processing. The HMC has multiple DRAM dies stacked on top of a logic layer that can provide the ability of computation with high memory access parallelism and sufficient instructions for supporting graph processing. As in Fig.3, the DRAM dies are connected via the Through-Silicon-Via (TSV). Storage space in HMC is organized as vaults. The vault is a vertically connected stack of multiple partitions from different DRAM layers. The logic layer is also distributed to different vaults. With multiple DRAM channels for each vault, HMC can provide significantly high memory-level parallelism. HMC can also be easily scaled to consist of a cluster topology of HMCs<sup>[98]</sup>.

Fig.3. An illustrative example of HMC architecture

The logic layer of each vault can work as a soft-core with sufficient instruction sets. For better supporting graph processing, instructions have to be reconstructed. Tesseract<sup>[32]</sup> integrates common instructions of graph algorithms and achieves high performance through multiple HMCs. GraphPIM<sup>[14]</sup> deigns specialized atomic instructions in HMCs. Besides, graphs are processed in a distributed manner between HMCs. Vertex-cut partitioning is also used to reduce the communication cost between HMCs<sup>[73,81]</sup>.

ReRAM-assisted Graph Processing. ReRAM is a kind of non-volatile RAM with the enabled computing ability by changing the resistance across a dielectric solid-state material<sup>[35]</sup>. A ReRAM cell is with high density, low read latency and high energy efficiency<sup>[99]</sup>. The ReRAM cells can be connected as a dense crossbar architecture to provide high parallelism and memory capacity. Generally, the graph can be represented as a matrix which can be naturally mapped to ReRAM cells. Each cell stores an edge or a vertex. When input voltages are applied to certain rows of the cells array, the stored values of each row will multiply the relevant input value. The stored values of each columns will be then added together. These features make it possible to realize efficient graph processing on ReRAM.

The potential of ReRAM for efficient computation and storage is still under-studied significantly. To our best knowledge, GraphR<sup>[70]</sup> is the first work to use ReRAM to speedup the graph computation. It transfers the vertex program or the edge program in graph processing to a Sparse Matrix-Vector Multiplication (SpMV) format. However, graph algorithms need to be manually justified for mapping the computational pattern of ReRAM. It is worth noting that there is also a tradeoff between the utilization and throughput due to the limited ReRAM cell size. An ideal situation is that every entity within a matrix is useful for computation for high parallelism. Nevertheless, due to the sparsity of graph data, in a ReRAM block there may be only a few useful edges that are non-zero, causing the fact that a large number of ReRAM cells are underutilized. Extra efforts are still needed to balance this tradeoff.

Summary. Considering the reconfigurable feature, FPGA-based designs can handle various kind of graph algorithms flexibly. FPGA can also provide sufficient interfaces to process large graphs for scale-out efficiency. Massive parallelism can be easily achieved when these resources are in good use. Unfortunately, the resources on FPGAs are limited for existing commodity FPGA boards. The frequency is also relatively low to maintain correctness of execution. These may influence the performance of graph processing.

ASIC designs can provide efficient hardware organizations without the limitation on types and numbers of hardware resources. ASICs can be designed in a relatively efficient way. For example, dedicated and accurate resources placement in ASCIs can be achieved while FPGAs usually have redundant and wasted resources on board. Besides, the ASIC can achieve a high frequency than FPGAs. High performance can be easily attained. However, once made, the ASIC chip is unable to be modified. It is usually difficult for ASICs

to handle various graph problems. It is also difficult for ASICs to scale out.

PIM-based accelerators can scale well in both of the bandwidth and memory capacity. This feature can benefit the graph processing when large graphs are handled. The emerging memories adopted in PIM-based accelerators usually have lower energy consumption than traditional DRAM. To handle generic graph analytics, the HMC provides the computing ability by special instruction sets executed in the logic layer. ReRAM processes the graphs in the SpMV format with corssbars. These supports usually need many manual efforts to realize. There is still a lot of research space for PIM-based graph accelerators. For example, the bandwidth can be underutilized due to the communication overhead in HMCs.

# 4.3 Large-Scale Graph Processing Accelera-

Real-world graph data size can easily exceed the on-chip/board memory capacity of graph processing accelerators. Most of existing accelerators only consider the case that the whole graph fits into the no-chip/board memory. However, how to deal with larger graphs on accelerators is a vital issue for practical applications. There is an amount of work that has taken this issue into account, and a series of solutions are further proposed [25, 26, 28, 32, 80, 94]. These solutions can be typically divided into three categories: the out-of-core solution, the multi-accelerators solution, and the heterogeneous solution.

#### 1) Out-of-Core Solution.

Unlike traditional CPU architectures that involve large main memory and often develop the out-of-core solutions based on the disks, graph accelerators typically have relatively small on-chip/board memory capacity. Therefore, toward graph accelerators, using any external storages or memories that can store large realworld graphs can be considered potentially-useful as their out-of-core solutions. Graph accelerators can use disks, flashes or other external storage devices to store extremely large scale graphs<sup>[4,5,26,55,94]</sup>. However, one of the most important issues for utilizing these devices is to reduce the transmission cost of I/Os between the disk and the DRAM since the bandwidths of these devices is often significantly lower than DRAM. Streamlined processing schemes<sup>[5,94]</sup> and sophisticated partitioning methods<sup>[26,55]</sup> can be explored to effectively reduce the overhead of memory accesses to these external devices. Recently, utilizing embedded processors or accelerators in SSDs has been proved to be another promising way to alleviate the overhead of data transmission and conversion $^{[100-102]}$ .

Compared to disk-based solutions, utilizing large host memory enables graph accelerators to process large-scale graphs with better bandwidth-efficiency<sup>[27,86,97]</sup>. Emerging computing platforms offer the great opportunity for graph accelerators to access the main memory conveniently via specialized interconnections<sup>[103]</sup>. However, it is also vital to optimize the I/Os between graph accelerator and main memory, since long memory latency for data movement often dominates the overall efficiency due to slow I/O interfaces and extra efforts on memory management<sup>[104]</sup>. Existing memory subsystems and their memory access parallelism are strongly in need of technological innovation.

There also have emerged some studies regarding graph processing accelerator designs for large-scale graph processing. FPGP<sup>[26]</sup> incorporates the disks to extend the storage of FPGA and designs a streamlined vertex-centric graph processing framework to improve the utilization of the sequential bandwidth of disks. A dedicated on-chip cache mechanism is used to re-

duce the accesses to disks. Then the large graph is specially partitioned in order to fit for the processing scheme. GraFBoost<sup>[94]</sup> adopts the flash to scale to much larger graphs and mainly focuses on optimizing the random accesses. The key component is a sort-reduce module that converts small random accesses into large block sequential accesses to the flash storage. It is mentioned that GraFBoost<sup>[94]</sup> embeds the accelerator into the flash for better scalability. Similar methods have been explored to accelerate the processing in database<sup>[105, 106]</sup>. ExtraV<sup>[97]</sup> further incorporates the main memory to improve the graph processing with SSDs. Note that host processors can be used together with its self-contained main memory in a heterogeneous solution to enhance the power of graph accelerators.

#### 2) Multiple Accelerators Extension.

The whole graph needs to be partitioned to distribute different on-chip/board memories of each graph processing accelerator. By considering the prohibitive communication overhead between graph accelerators, the multi-accelerator solution often needs the high-bandwidth connection between graph accelerators. The most important issue for this design is how to achieve a cost-efficient communication mechanism, and avoid data conflicts between graph accelerators. As a consequence, the appropriate graph partition methods are required and are important to reduce the communication overhead<sup>[28, 32, 81]</sup>. The inter-network design of graph accelerators is also vital to support the efficient cooperative computing<sup>[25, 73]</sup>.

CyGraph<sup>[25]</sup> runs BFS under a high performance reconfigurable computing platform, Convey HC-2, which constructs a platform with FPGAs connected through a full crossbar to multiple on-board memories. These memories are connected as a shared memory that provides large capacity and high total bandwidth. Cy-Graph optimizes the CSR representation to reduce the shared memory accesses and connects the FPGAs using a ring network to minimize the conflicts. ForeGraph<sup>[28]</sup> instead uses separated memories for each FPGA. Thus it avoids the memory access conflicts among accelerators. These FPGAs are connected via dedicated inter-connections. Grid-like partitioning<sup>[55]</sup> and dedicated on-chip data replacement schemes are adopted to achieve better locality for each FPGA board and thus reduce the communications.

As discussed in Section 4.2, emerging devices like HMCs not only provide the capability of processing in memory but also scale well. The cost on communications among different HMC cubes dominates the performance<sup>[32,73,81]</sup>. GraphP<sup>[81]</sup> utilizes a source-cut partitioning method to significantly reduce the communication overhead. Generally, multi-accelerator solutions is similar to distributed processing under traditional platforms such that many optimizations on distributed graph processing can be applied to accelerators. Meanwhile, the features of different architectures need to be considered to provide the best scenario.

#### 3) Heterogeneous Acceleration.

As the rapid development of memory integration technologies (e.g., 3D stacking), the host memory becomes large or even huge with trillions of capacity<sup>[3,50]</sup>. As a consequence, leveraging the host-side memory is alternative to support large-scale graph processing. An intuitive and important question is how graph processing accelerator can interact with the host machine conveniently and efficiently. At present, efficient heterogeneous solutions are still open questions. A few studies propose to use the coherent memory interconnect technology to accelerate graph workloads with CPU and FPGA<sup>[80]</sup>. For supporting efficient cooperation, the dedicated memory subsystem is needed to alleviate the transmission overhead between the host and the graph accelerator. As a result, the data organization of graphs

is the key to reduce the communication overhead. In order to avoid conflicts of computing devices, runtime scheduling schemes are also important for efficient task scheduling.

The authors in [80] propose to accelerate graph processing under a heterogeneous architecture with CPU and FPGA. Hybrid vertex- and edge-centric models are adopted in [80] as discussed in Section 4.1 to fully utilize the processing power of CPUs and FPGAs. Generally, CPU is better for fast sequential processing while FPGA can be used to explore massive parallelism. Hybrid model can flexibly assign workloads to these two devices according to the parallelism of vertices in each iteration. In order to support this scheme, an optimized graph data structure is designed. As for memory coherency, dedicated on-chip memory buffers are designed on FPGA and the accesses to the host memory is controlled by a master thread on the CPU. Despite that the heterogeneous solution can extend the power of accelerators, the overhead to maintain the memory coherency might limit the performance. There is still a lot of research space for heterogeneous solutions.

#### 4.4 Sophisticated Co-designs

Graph processing accelerators often require a series of optimizations for fully exploiting their hardware potentials. There also emerge a few co-optimization techniques at these aspects for high parallelism, lower memory access overhead, and better energy efficiency.

#### 4.4.1 Parallelism Extension

The processing units in either ASIC- or FPGAbased graph processing accelerators are often organized in the form of pipelines. The instructions of graph algorithms are pipelined to offer high parallelism. PIMbased graph accelerators integrate the processing units inside the memory. Their efficiency can be scaled by simply enlarging the memory capacity. For better scalability, three optimization solutions below can be considered useful potentially.

Pipeline Duplication. An intuitive method to increase the throughput is to duplicate multiple pipelines for the parallel processing on more vertices and edges. This simple method has been widely used in a wide spectrum of previous work<sup>[16,27,29,30,85,92,107]</sup>. Nevertheless, there still remain some potential problems that might prevent the scalable efficiency of multipipeline from expectation, which is significantly understudied. For instance, considerable communication between pipelines may lead to the additional overhead via crossbars and controllers<sup>[16,29]</sup>. In addition, there also exists workload balance issue that needs specialized data partitioning<sup>[16,28]</sup>.

Split Kernel. Alternative is to split a big, whole processing stream into many small kernels that can be then considered being executed in parallel. This is often done by decoupling the modules of data access and computation, and then making them executed in parallel. In this way the data access module is responsible for accessing graph data. The computation module uses the data to conduct user-defined computations. For example, by using GAS model, [25, 29, 30] create specialized execution circuits. Each module is thus enabled to process a large number of vertices and edges concurrently. The SpMV-based accelerator<sup>[107]</sup> also decouples the matrix access from the computation. This method explores the task-level parallelism but extra scheduling mechanism are needed to ensure the correctness.

Using Dataflow Paradigm. Vertex dependencies of graph can stall the pipelines and decrease the instruction level parallelism. How to reduce the impact arising from data dependencies remains an open problem for increasing the number of Instructions per Cycle (IPC). One viable solution for solving this problem

is to leverage the dataflow paradigm<sup>[72,91,108]</sup>, which forms a directed graph of the operations according to the data dependency between two adjacent operations. The output dependency and control dependency in graph processing can be then significantly eliminated<sup>[91]</sup>. GraphOps<sup>[72]</sup> uses dataflow model to form the data path of different processing blocks. Their overhead of controlling feedback can be therefore alleviated.

#### 4.4.2 Memory Access Optimization

For graph processing, memory accesses often dominate overall execution time. Designing an efficient memory subsystem is crucial for the graph processing accelerator, particularly for memory access efficiency<sup>[16,29]</sup>.

#### 1) Enhancing Memory-Level Parallelism (MLP).

The MLP can be represented as the number of outstanding memory requests supported at the same time. Higher MLP can reduce the total memory access time for data-intensive applications as graph processing. It usually needs the memory devices to support enough concurrent memory requests. There are two ways to enhance the MLP.

Multiple Banks. One method to increase the MLP is using multiple banks. DRAM is composed of many independent banks. Utilizing the parallelism of these banks can significantly improve the memory level parallelism<sup>[85–87]</sup>. The memory banks are connected to the processing units directly through crossbars. They can be accessed concurrently.

Multiple I/O Ports. Another method is to design multiple I/O ports for a memory block<sup>[27,88,92]</sup>. By increasing the I/O ports, multiple memory requests can run concurrently. Usually the number of ports can be manually organized on the scratchpad memory. High MLP can be attained when the number of ports are

equal to the number of processing units<sup>[16]</sup>. BRAMs on FPGAs can also be manually controlled to achieve this goal<sup>[27]</sup>. These BRAMs are usually combined together to form a memory block with multiple I/O ports.

#### 2) Improving Bandwidth Utilization.

The memory bandwidth utilization here means the valid values ratio per transfer. Random accesses in graph processing usually cause low ratio of valid values and result in much wasted bandwidth. Improving the memory bandwidth utilization can reduce the total number of memory accesses. There are mainly two effective methods for improving the bandwidth utilization.

Coalescing Method. Coalescing means combining multiple transfers of small items into fewer large ones. This method is widely adopted in graph accelerators<sup>[27,71,88,92,93]</sup>. For example, if the memory requests are adjacent in a vertex or edge list, these requests can be coalesced as one request for a block. Otherwise there may exist several random accesses that lead to the wasting of bandwidth<sup>[88]</sup>.

Streaming Edges. Streaming edges means that the edges are sequentially accessed from the memory to accelerator<sup>[27]</sup>. Random accesses of edges can be reduced. In a vertex-centric model, the edges of a vertex can be streamed to the chip<sup>[16]</sup>. This method can fully utilize the bandwidth in the edge-centric model. However, the edges may need to be reordered so as to run in a more efficient fashion<sup>[27,28]</sup>.

# 3) Reshaping Cache Hierarchy.

Poor locality of graph processing makes the current cache hierarchy lack of efficiency. High cache miss rate will increase the memory access latency, which would cause the under-utilization of computing resources. Reshaping the cache hierarchy means designing new cache architectures and mechanisms for graph processing features. Scratchpad Memory. Scratchpad memory is used as an addressable cache that can be explicitly controlled. The scratchpad memory is closed to the graph engines. It can provide high performance for data access<sup>[73,109,110]</sup>. Graphicionado<sup>[16]</sup> uses scratchpad memory to store the temporary vertex property array and edge offset to optimize the random data accesses. Similarly, [29] also designs different kind of caches for vertices, edges, and other graph information according to their access behaviors.

Locality-aware Buffer. Locality-aware buffer is a kind of specialized cache for graph data with relatively good locality, e.g., the high degree vertices. High degree vertices in a power-law graph have higher probability to be accessed many times. These vertices can be cached to improve performance<sup>[30]</sup>. FPGP<sup>[26]</sup> and ForeGraph<sup>[28]</sup> improve the locality of vertices using grid-like partitioning methods, and design special onchip buffers for vertex subsets, which can be thus accessed fast in reuse.

Execution-aware Prefetching. This method prefetches the graph data according to the execution requirements. It avoids the inefficiency of fixed traditional cache prefetching mechanism. For example, in vertex-centric model, the source vertex list and its corresponding edge list can be prefetched sequentially [32]. The key is to exploit the access patterns of different kinds of graph data during the execution, and further design appropriate prefeching mechanism to reduce the memory latency.

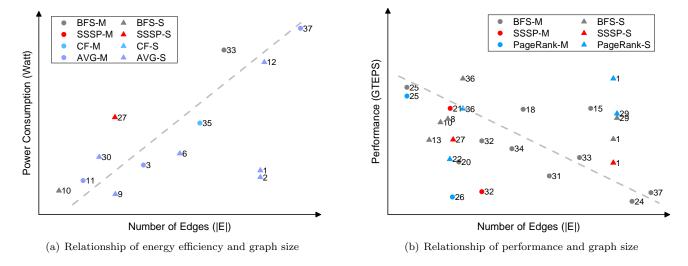

#### 4.4.3 Energy efficiency Optimization

The performance of graph accelerators can be measured as Traversed Edges per Second (TEPS). Energy efficiency can be further defined as TEPS per Watt (TEPS/W). Existing graph processing accelerators can provide significantly high performance by dedicated cir-

cuits with inherent low-energy consumption. However, most of graph programs have a high memory-access-to-computation ratio. For example, the energy results show that PageRank consumes over 60% energy on memory<sup>[111]</sup>. Optimizations on memory consumption can further improve the energy efficiency. Nowadays, there are two simple yet effective ways to improve the memory energy consumption.

Leveraging Emerging Memory Technologies. A number of emerging memory technologies integrate the computing logic inside the memory, e.g., HMC<sup>[14, 32, 73, 81]</sup> and ReRAM<sup>[70, 82]</sup> as described previously. This architectural reformation can conduct the in-situ computation along side the data. It naturally avoids the frequent data movement for energy saving. At this point, we can easily replace traditional DRAM by leveraging these emerging memory devices.

Power-gating Schemes. Power-gating is a widely used technology that powers off the idle logic circuits to save the energy. This scheme is suitable for memories that can be manually controlled<sup>[27,82]</sup>. For example, it can be applied to BRAMs on FPGAs, which are the key for improving the overall FPGA energy consumption in graph processing accelerators<sup>[27]</sup>. The BRAM is selectively activated and deactivated via the enabled ports. A BRAM module is only activated when the required data is stored. When the edges of a vertex are stored in the same BRAM module, BRAM only needs to be activated once to traverse these edges<sup>[27]</sup>. Similar strategies can be used for ReRAM<sup>[82]</sup> to save the energy for edge access by controlling the activation of ReRAM banks in a flexible way.

#### 5 Runtime Scheduling

As discussed in Section 4.2, customized hardware circuits for graph processing generally involve specialized designs. This often enforces to design the tai-

lored runtime scheduling to appropriately assign workloads and coordinate the processing units for providing the correct and efficient execution. Unlike existing runtime schedulers on traditional processors, the runtime scheduling for graph accelerators may be necessarily needed to be implemented in the form of hardware circuits. This process usually needs to be transparent to users. Runtime scheduling usually involve three aspects of core components: the communication models, the execution modes, and the scheduling schemes.

- Communication Model. Communications commonly

exist in graph processing accelerators among processing units. Communication models provides efficient

ways for these processing units to communicate and

cooperate with each other. Graph accelerators usually adopt two kinds of communication models: the

message-based pattern and the shared memory pattern. These models present different features and can

benefit from the optimization of information flows.

- Execution Mode. The execution mode determines the scheduling order of operations. There are two kinds of execution modes that have been widely used for existing graph processing accelerators: synchronous execution and asynchronous execution.

- Scheduling Schemes. Scheduling schemes defines the granularity and processing order of graph data. Existing work adopts three kinds of scheduling schemes: block-based scheduling, frontier-based scheduling, and priority-based scheduling. Flexibly using these scheduling schemes can help reduce the conflicts and improve the utilization of hardware resources.

#### 5.1 Runtime Considerations

For preserving the correctness and efficiency, runtime scheduling for graph processing accelerator needs to consider the following two major aspects.

- Data Conflicts. A specific vertex of a graph may be often associated with a large number of edges, particularly true for skewed graphs. There is the common case that some vertices may be updated in conflict by many vertices simultaneously. For preserving the correctness of vertex updating, the specialized mechanisms are presented to enforce the atomicity. For example, for a read-modify-write update of a destination vertex, [16,27] propose to use the Content Addressable Memory (CAM) like hardware structure to support finer-granularity memory access, but extra pipeline stalls occur. Similar conflicts can also exist between multiple pipelines. An effective runtime scheduling is expected to avoid these conflicts of vertex updating for high throughput.

- Workload Balance. Natural graphs in the real world often manifest the power-law distribution<sup>[112]</sup>. This can result in severe load imbalance issue in the sense that a few vertices have extremely high degrees. Workload imbalance may lead to the fact that the loads of some computational logic is overly assigned while other light processing units are stalled. More serious is that the loads of the graph computation are often difficult to predict due to the complex data dependencies. An effective runtime scheduling scheme for graph processing accelerators should be also expected to dynamically balance hardware resources with even loads for every processing unit as much as possible<sup>[29]</sup>.

# 5.2 Communication Model

The communication model is a well-known pattern that exists commonly to propagate the information between different processing units. We next survey several patterns that have been used in off-the-shelf graph accelerators. Message-based Pattern. Message-based communication model is widely used in distributed environments. In message-based communication model, communication is realized by sending messages among different processing units. These massages can carry the updated data or computation commands that will be execute locally. This model is widely used in HMC-assisted graph processing accelerators<sup>[32,81]</sup>. As mentioned previously, the vaults in HMCs communicate with each other via messages.

Tesseract<sup>[32]</sup> designs the remote function call mechanism via message passing to indicate the running of destination processing cores. The message passing can be used to avoid the cache coherence issues of the processing cores. It can also reduce the atomic operations for shared data. However, a large number of messages come with a high cost of communication time and bandwidth. Partitioning methods and coalescing methods are usually needed to reduce the number of messages<sup>[81]</sup>. Besides, extra memory copying operations and buffers are also needed.

Shared Memory-based Pattern. The shared memory model is suited for the communication between processing units on a single accelerator. The same location of a memory can be accessed and updated by multiple processing units simultaneously. When multiple accelerators are adopted, it is also possible to have a distributed shared memory.

FPGP<sup>[26]</sup> adopts this model based on FPGAs. It maintains a global shared vertex memory for multiple FPGA boards and each board keeps a vertex cache for multiple processing units. Synchronization between iterations is needed to maintain memory consistency. Constrained by limited bandwidth, the global shared vertex memory can limit the scalability of FP-GAs. ForeGraph<sup>[28]</sup> uses a distributed shared memory. Shared memory model can usually avoid the redundant

copies of graph data and extra storage space in message passing model. It is also easy to implement and design. However, there may exist many data races on the same memory location if some vertices are updated by many neighboring vertices.

#### 5.3 Execution Model