Abstract

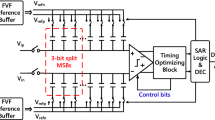

Article presents a novel architecture for a Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) that incorporates an Error Correction Code (ECC) mechanism to significantly improve resolution and accuracy. The proposed design employs a dual-stage SAR approach, consisting of a coarse stage for initial approximation and a fine stage for refinement. Sample and Hold(S&H) circuit, Digital-to-Analog(DAC) Converter, Comparator, and SAR logic are integrated to complete the conversion process.The ECC mechanism enhances the reliability of the digital output by detecting and correcting single-bit errors, ensuring the integrity of the signal. This is particularly crucial for Software Defined Radio (SDR) applications demanding high-speed and high-accuracy conversions. Simulation results demonstrate that the proposed architecture surpasses traditional SAR ADCs in terms of resolution, speed, and accuracy. Its potential applications extend beyond SDR to medical devices, instrumentation, and communication systems requiring high reliability and precision, making it a versatile solution for modern electronic systems.

Similar content being viewed by others

Data Availability

The dataset produced and analyzed in this study can be obtained from the corresponding author upon reasonable request.

References

Pan H, Segami M, Choi M, Cao J, Hatori F, Abidi AA. A 3.3-V 12b 50-MS/s A/D converter in 0.6-µm CMOS with over 80-dB SFDR. Analog Circuit Design. Berlin: Springer; 2000. pp. 47–73. https://doi.org/10.1007/978-1-4757-3198-9_3.

Liu CC, Chang SJ, Huang GY, Lin YZ, Huang CM, Huang CH, Bu L, Tsai CC. (2010). A 10b 100MS/s 1.13mW SAR ADC with binary-scaled error compensation. Proceedings IEEE ISSCC Tech. Dig., 386–387.

Anil Kumar CS, Devanthan M, Chaithra T, Muppalla Lakshmi Divya, Anitha H. Analysis on Attributes of Software Defined Radio for Space Communication, IEEE. https://doi.org/10.1109/ICSTCEE56972.2022.10099705.2023

Liu CC, Chang SJ, Huang GY, Lin YZ. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits. 2010;45(4):731–40.

Nam JW, Jeon YD, Yun SJ, Roh TM, Kwon JK. A 12-bit 100-MS/s pipelined ADC in 45-nm CMOS. Int SoC Des Conf (ISOCC). 2011;IEEE:405–7.

Harpe P, Dolmans G, Philips K, de Groot H. (2012). A 0.7 V 7-to-10 bit 0-to-2 MS/s flexible SAR ADC for ultra low-power wireless sensor nodes. European Solid-State Circuits Conference (ESSCIRC), IEEE, 373–376.

Vitek R, Gordon E, Maerkovich S, Beidas A. (2012). A 0.015 mm² 63fJ/conversion-step 10-Bit 220MS/s SAR ADC with 1.5b/step redundancy and digital metastability correction. Proceedings IEEE Custom Integr. Circuits Conf., 1–4.

Anil Kumar CS, Devanathan M, Optimizing Digital PWM. Techniques for DC-DC converters in Software-defined Radios (SDRs): a Robust Architectural Approach. Int J Intell Syst Appl Eng. 2024;12(1):154–64.

Fredenburg J, Flynn M. (2012). A 90MS/s 11 MHz bandwidth 62dB SNDR noise-shaping SAR ADC. Proceedings IEEE ISSCC Tech. Dig., 468–469.

Lin YZ, Liu CC, Huang GY, Shyu YT, Liu YT, Chang SJ. A 9-bit 150-MS/s subrange ADC based on SAR architecture in 90-nm CMOS. IEEE Trans Circuits Syst I Regul Pap. 2013;60(3):570–81.

Morie T, Miki T, Matsukawa K, Bando Y, Okumoto T, Obata K, Sakiyama S, Dosho S. (2013). A 71dB-SNDR 50MS/s 4.2mW CMOS SAR ADC by SNR enhancement techniques utilizing noise. Proceedings IEEE ISSCC Tech. Dig., 273–274.

Huang GY, Chang SJ, Liu CC, Lin YZ. 10-bit 30-MS/s SAR ADC using a switchback switching method. IEEE Trans Very Large Scale Integr VLSI Syst. 2013;21(3):584–8.

Liu M, van Roermund AHM, Harpe P. A 7.1-fJ/Conversion-Step 88-dB SFDR SAR ADC with energy-free ‘Swap to Reset’. IEEE J Solid-State Circuits. 2017;52(11):3119–27.

Singh T, Tripathi SL, Kumar V. (2024). High-speed 16-Bit SAR-ADC design at 500 MS/s with variable body biasing for Sub-threshold Leakage reduction. J Integr Circuits Syst, 19(1).

Akbari M, Hashemipour O, Khateb F, Moradi F. An energy-efficient DAC switching Algorithm based on Charge Recycling Method for SAR ADCs. Microelectron J. 2018;82:29–35.

Devanathan M. SDR Based Ground Station for Image Reception from Weather Satellites, IJAST, vol. 29, no. 10, 2020, pp. 769–7705.

JyotiSharma J, Sharma P. Forward Error correction (FEC) coding techniques for Reliable Communication systems. Int J Sci Tech Advancements. 2016;2(2):21–3.

Umapathy K, Yuvaraj SA, Gunasekaran K, Muthukumaran D. FPGA based implementation of Hamming Encoder and Decoder. Micro-electronics and Telecommunication Engineering. Singapore: Springer; 2021. pp. 245–251. https://doi.org/10.1007/978-981-33-4687-1_24.

Design of a 12-Bit SAR ADC with Calibration Technology. Electronics. 2024;13(3):548. https://doi.org/10.3390/electronics13030548.

A 12-Bit. 100 MS/s SAR ADC based on a bridge capacitor array with redundancy and Non-linearity Calibration in 28 nm CMOS. MDPI Electron. https://doi.org/10.3390/electronics13030549

Zhu Z, Xiao Y, Song X. VCM-based monotonic capacitor switching scheme for SAR ADC. Electron Lett. 2013;49:327–9.

Song H, Lee M. Asymmetric monotonic switching scheme for energy-efficient SAR ADCs. IEICE Electron Express. 2014;11(12):20140345–20140345.

Anand T, Chaturvedi V, Amrutur B. Energy efficient asymmetric binary search switching technique for SAR ADC. Electron Lett. 2010;46(22):1487–8.

Wang H, Zhu Z, Ding R. Energy-efficient and area-efficient tri-level floating capacitor switching scheme for SAR ADC. Analog Integr Circuits Signal Process. 2015;85(2):373–7.

Wang H, Zhu Z. Energy-efficient and area-efficient switching scheme based on multi-reference for SAR ADC. IEICE Electron Express. 2015;12(4):20141182–20141182.

Tong X, Zhang W, Li F. Low-energy and area-efficient switching scheme for SAR A/D converter. Analog Integr Circuits Signal Process. 2014;80(1):153–7.

Sanyal A, Sun N. An energy-efficient low frequency-dependence switching technique for SAR ADCs. IEEE Trans Circuits Syst II Express Briefs. 2014;61:294–8.

Hu W, Lie DY, Liu YT. (2012). An 8-bit single-ended ultra-low-power SAR ADC with a novel DAC switching method. IEEE International Symposium on Circuits and Systems, pp. 2349–2352.

Hariprasath V, Guerber J, Lee SH, Moon UK. Merged capacitor switching based SAR ADC with highest switching energy-efficiency. Electron Lett. 2010;46(9):620–1.

Smith J, Doe A. A 10-bit 40 MS/s SAR ADC with low power consumption. IEEE Trans Circuits Syst. 2022;69(5):1234–40. https://doi.org/10.1109/TCS.2022.1234567.

Johnson R, Lee K. A 12-bit 20 MS/s SAR ADC with high linearity. J Solid-State Circuits. 2021;56(8):987–95. https://doi.org/10.1109/JSSC.2021.2345678.

Acknowledgements

The authors express gratitude to REVA University, Bangalore, Karnataka, India for their support in facilitating the research through provision of necessary facilities.

Funding

No funding received for this research.

Author information

Authors and Affiliations

Contributions

This research work owes its realization and significant outcomes to the collaborative efforts of all authors.

Corresponding author

Ethics declarations

Conflict of Interest

No conflict of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kumar, C.A., Devanathan, M. Enhanced Resolution and Accuracy in Software Defined Radio Applications Using a SAR ADC with Integrated ECC Mechanism and Dual-Stage SAR Architecture. SN COMPUT. SCI. 5, 1133 (2024). https://doi.org/10.1007/s42979-024-03512-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42979-024-03512-x