Abstract

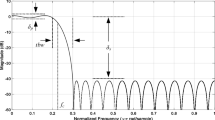

Finite impulse response (FIR) filtering is a ubiquitous operation in digital signal processing systems and is generally implemented in full custom circuits due to high-speed and low-power design requirements. The complexity of an FIR filter is dominated by the multiplication of a large number of filter coefficients by the filter input or its time-shifted versions. Over the years, many high-level synthesis algorithms and filter architectures have been introduced in order to design FIR filters efficiently. This article reviews how constant multiplications can be designed using shifts and adders/subtractors that are maximally shared through a high-level synthesis algorithm based on some optimization criteria. It also presents different forms of FIR filters, namely, direct, transposed, and hybrid and shows how constant multiplications in each filter form can be realized under a shift-adds architecture. More importantly, it explores the impact of the multiplierless realization of each filter form on area, delay, and power dissipation of both custom (ASIC) and reconfigurable (FPGA) circuits by carrying out experiments with different bitwidths of filter input, design libraries, reconfigurable target devices, and optimization criteria in high-level synthesis algorithms.

Similar content being viewed by others

Notes

An integer can be written in CSD using \(n\) digits as \(\sum _{i=0}^{n-1} d_i 2^{i}\), where \(d_i \in \{1, 0, \overline{1}\}\) and \(\overline{1}\) denotes \(-1\). The nonzero digits are not adjacent, and a constant is represented with minimum number of nonzero digits under CSD.

MSD differs from CSD in one property which allows the nonzero digits to be adjacent. Thus, a constant may have alternative representations in MSD, all including minimum number of nonzero digits.

The top signal path carrying the delayed filter input in Fig. 1a.

The bottom signal path including the adders that compute the filter output in Fig. 1a.

The adder that computes the filter output is always assumed to be connected to a register even this register is not synthesized in hardware.

The bitwidth of the filter output is computed as \(bwi + \lceil log_2\sum _{i=0}^{N-1}|h_i|\rceil \), where \(h_i\) is the \(i\mathrm{th}\) fixed-point filter coefficient with \(0 \le i \le N-1\).

The design library is available at www.nangate.com.

References

L. Aksoy, E. Costa, P. Flores, J. Monteiro, Exact and approximate algorithms for the optimization of area and delay in multiple constant multiplications. IEEE Trans. Comput.-Aided Des. Integr. Circuits 27(6), 1013–1026 (2008)

L. Aksoy, E. Costa, P. Flores, J. Monteiro, Design of low-power multiple constant multiplications using low-complexity minimum depth operations. in Proceedings of Great Lakes Symposium on VLSI (2011), pp. 79–84

L. Aksoy, E. Costa, P. Flores, J. Monteiro, Finding the optimal tradeoff between area and delay in multiple constant multiplications. Elsevier J. Microprocess. Microsyst. 35(8), 729–741 (2011)

L. Aksoy, E. Costa, P. Flores, J. Monteiro, Design of low-complexity digital finite impulse response filters on FPGAs. in Proceedings of Design, Automation and Test in Europe Conference (2012), pp. 1197–1202

L. Aksoy, E. Costa, P. Flores, J. Monteiro, Multiplierless design of linear DSP transforms. in VLSI-SoC: Advanced Research for Systems on Chip, Chap. 5 (Springer, 2012), pp. 73–93

L. Aksoy, E. Costa, P. Flores, J. Monteiro, Optimization algorithms for the multiplierless realization of linear transforms. ACM Trans. Des. Autom. Electron. Syst. 17(1), Art. No. 3 (2012). doi:10.1145/2071356.2071359

L. Aksoy, E. Gunes, P. Flores, Search algorithms for the multiple constant multiplications problem: exact and approximate. Elsevier J. Microproces. Microsyst. 34(5), 151–162 (2010)

M. Aktan, A. Yurdakul, G. Dnndar, An algorithm for the design of low-power hardware-efficient FIR filters. IEEE Trans. Circuits Syst. 55(6), 1536–1545 (2008)

A. Arfaee, A. Irturk, N. Laptev, F. Fallah, R. Kastner, Xquasher: a tool for efficient computation of multiple linear expressions. in Proceedings of Design Automation Conference (2009), pp. 254–257

N. Boullis, A. Tisserand, Some optimizations of hardware multiplication by constant matrices. IEEE Trans. Comput. 54(10), 1271–1282 (2005)

N. Brisebarre, F. de Dinechin, J.M. Muller, Integer and floating-point constant multipliers for FPGAs. in Proceedings of the International Conference on Application-Specific Systems, Architectures and Processors (2008), pp. 239–244

P. Cappello, K. Steiglitz, Some complexity Issues in digital signal processing. IEEE Trans. Acoust. Speech Signal Process. 32(5), 1037–1041 (1984)

J. Chen, C.H. Chang, H. Qian, New power index model for switching power analysis from adder graph of FIR filter. in Proceedings of IEEE International Symposium on Circuits and Systems (2009), pp. 2197–2200

S. Demirsoy, A. Dempster, I. Kale, Power analysis of multiplier blocks. in Proceedings of IEEE International Symposium on Circuits and Systems (2002), pp. 297–300

A. Dempster, Use of minimum-adder multiplier blocks in FIR digital filters. IEEE Trans. Circuits Syst. II 42(9), 569–577 (1995)

A. Dempster, S. Demirsoy, I. Kale, Designing multiplier blocks with low logic depth. in Proceedings of IEEE International Symposium on Circuits and Systems (2002), pp. 773–776

A. Dempster, M. Macleod, Constant integer multiplication using minimum adders. IEE Proc. Circuits Devices Syst. 141(5), 407–413 (1994)

A. Dempster, M. Macleod, Digital filter design using subexpression elimination and all signed-digit representations. in Proceedings of IEEE International Symposium on Circuits and Systems (2004), pp. 169–172

M. Ercegovac, T. Lang, Digital Arithmetic. (Morgan Kaufmann, 2003)

M. Faust, C.H. Chang, Optimization of structural adders in fixed coefficient transposed direct form FIR filters. in Proceedings of IEEE International Symposium on Circuits and Systems (2009), pp. 2185–2188

M. Faust, C.H. Chang, Minimal logic depth adder tree optimization for multiple constant multiplication. in Proceedings of IEEE International Symposium on Circuits and Systems (2010), pp. 457–460

M. Faust, C.H. Chang, Low error bit width reduction for structural adders of FIR filters. in Proceedings of IEEE European Conference on Circuit Theory and Design (2011), pp. 713–716

P. Flores, J. Monteiro, E. Costa, An exact algorithm for the maximal sharing of partial terms in multiple constant multiplications. in Proceedings of International Conference on Computer-Aided Design (2005), pp. 13–16

W. Gallagher, E. Swartzlander, High radix booth multipliers using reduced area adder trees. in Proceedings of Asilomar Conference on Signals, Systems and Computers (1994), pp. 545–549

R. Guo, L. Wang, L. DeBrunner, A novel FIR filter implementation using truncated MCM technique. in Proceedings of Asilomar Conference on Signals, Systems and Computers (2009), pp. 718–722

O. Gustafsson, A difference based adder graph heuristic for multiple constant multiplication problems. in Proceedings of IEEE International Symposium on Circuits and Systems (2007) pp. 1097–1100

O. Gustafsson, Lower bounds for constant multiplication problems. IEEE Trans. Circuits Syst. II 54(11), 974–978 (2007)

O. Gustafsson, J. Coleman, A. Dempster, M. Macleod, Low-complexity hybrid form FIR filters using matrix multiple constant multiplication. in Proceedings of Asilomar Conference on Signals, Systems and Computers (2004), pp. 77–80

O. Gustafsson, A. Dempster, L. Wanhammar, Extended results for minimum-adder constant integer multipliers. in Proceedings of IEEE International Symposium on Circuits and Systems (2002), pp. 73–76

O. Gustafsson, H. Ohlsson, L. Wanhammar, Low-complexity constant coefficient matrix multiplication using a minimum spanning tree. in Proceedings of Nordic Signal Processing Symposium (2004), pp. 141–144

O. Gustafsson, L. Wanhammar, ILP modelling of the common subexpression sharing problem. in Proceedings of International Conference on Electronics, Circuits and Systems (2002), pp. 1171–1174

R. Hartley, Subexpression sharing in filters using canonic signed digit multipliers. IEEE Trans. Circuits Syst. II 43(10), 677–688 (1996)

R. Hawley, B. Wong, T.J. Lin, J. Laskowski, H. Samueli, Design techniques for silicon compiler implementations of high-speed FIR digital filters. IEEE J. Solid-State Circuits 31(5), 656–667 (1996)

Y.H. Ho, C.U. Lei, H.K. Kwan, N. Wong, Global optimization of common subexpressions for multiplierless synthesis of multiple constant multiplications. in Proceedings of Asia and South Pacific Design Automation Conference (2008), pp. 119–124

A. Hosangadi, F. Fallah, R. Kastner, Reducing hardware complexity of linear DSP systems by iteratively eliminating two-term common subexpressions. in Proceedings of Asia and South Pacific Design Automation Conference (2005), pp. 523–528

A. Hosangadi, F. Fallah, R. Kastner, Simultaneous optimization of delay and number of operations in multiplierless implementation of linear systems. in Proceedings of International Workshop on Logic Synthesis (2005)

K. Johansson, O. Gustafsson, L. DeBrunner, L. Wanhammar, Minimum adder depth multiple constant multiplication algorithm for low power FIR filters. in Proceedings of IEEE International Symposium on Circuits and Systems (2011), pp. 1439–1442.

K. Johansson, O. Gustafsson, L. Wanhammar, A detailed complexity model for multiple constant multiplication and an algorithm to minimize the complexity. in Proceedings of IEEE European Conference on Circuit Theory and Design (2005), pp. 465–468

H.J. Kang, I.C. Park, FIR filter synthesis algorithms for minimizing the delay and the number of adders. IEEE Trans. Circuits Syst. II 48(8), 770–777 (2001)

K.Y. Khoo, Z. Yu, A. Willson, Design of optimal hybrid form FIR filter. in Proceedings of IEEE International Symposium on Circuits and Systems (2001), pp. 621–624

M. Kumm, P. Zipf, M. Faust, C.H. Chang, Pipelined adder graph optimization for high speed multiple constant multiplication. in Proceedings of IEEE International Symposium on Circuits and Systems (2012), pp. 49–52

V. Lefevre, Multiplication by an Integer Constant. Tech. rep., Institut National de Recherche en Informatique et en Automatique (2001)

M. Macleod, A. Dempster, A common subexpression elimination algorithm for low-cost multiplierless implementation of matrix multipliers. Electron. Lett. 40(11), 651–652 (2004)

K. Macpherson, R. Stewart, Rapid prototyping—area efficient FIR filters for high speed FPGA implementation. IEE Proc. Vision Image Signal Process. 153(6), 711–720 (2006)

J. McClellan, T. Parks, L. Rabiner, A computer program for designing optimal FIR linear phase digital filters. IEEE Trans. Audio Electroacoustics 21(6), 506–526 (1973)

U. Meyer-Baese, J. Chen, C.H. Chang, A. Dempster, A comparison of pipelined RAG-n and DA FPGA-based multiplierless filters. in Proceedings of IEEE Asian-Pacific Conference on Circuits and Systems (2006), pp. 1555–1558

K. Muhammad, K. Roy, A graph theoretic approach for synthesizing very low-complexity high-speed digital filters. IEEE Trans. Comput.-Aided Des. Integr. Circuits 21(2), 204–216 (2002)

H. Nguyen, A. Chatterjee, Number-splitting with shift-and-add decomposition for power and hardware optimization in linear DSP synthesis. IEEE Trans. VLSI 8(4), 419–424 (2000)

I.C. Park, H.J. Kang, Digital filter synthesis based on minimal signed digit representation. in Proceedings of Design Automation Conference (2001), pp. 468–473

M. Potkonjak, M. Srivastava, A. Chandrakasan, Multiple constant multiplications: efficient and versatile framework and algorithms for exploring common subexpression elimination. IEEE Trans. Comput.-Aided Des. Integr. Circuits 15(2), 151–165 (1996)

F. Qureshi, O. Gustafsson, Low-complexity reconfigurable complex constant multiplication for FFTs. in Proceedings of IEEE International Symposium on Circuits and Systems (2009), pp. 24–27

D. Shi, Y.J. Yu, Design of linear phase FIR filters with high probability of achieving minimum number of adders. IEEE Trans. Circuits Syst. 58(1), 126–136 (2011)

J. Thong, N. Nicolici, A novel optimal single constant multiplication algorithm. in Proceedings of Design Automation Conference (2010), pp. 613–616

Y. Voronenko, M. Püschel, Multiplierless multiple constant multiplication. ACM Trans. Algorithms 3(2), Art. No. 11 (2007). doi:10.1145/1240233.1240234

C. Wallace, A suggestion for a fast multiplier. IEEE Trans. Electron. Comput. 13(1), 14–17 (1964)

E. Walters III, Design Tradeoffs Using Truncated Multipliers in FIR Filter Implementations. Master’s thesis, Lehigh University (2002)

F. Xu, C.H. Chang, C.C. Jong, Contention resolution algorithm for common subexpression elimination in digital filter design. IEEE Trans. Circuits Syst. II: Express Briefs 52(10), 695–700 (2005)

S.H. Yoon, J.W. Chong, C.H. Lin, An area optimization method for digital filter design. ETRI J. 26(6), 545–554 (2004)

A. Yurdakul, G. Dündar, Multiplierless realization of linear DSP transforms by using common two-term expressions. J. VLSI Signal Process. 22(3), 163–172 (1999)

Acknowledgments

This work was supported by the national funds through FCT, Fundação para a Ciência e a Tecnologia, under Project PEst-OE/EEI/LA0021/2013.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Aksoy, L., Flores, P. & Monteiro, J. A Tutorial on Multiplierless Design of FIR Filters: Algorithms and Architectures. Circuits Syst Signal Process 33, 1689–1719 (2014). https://doi.org/10.1007/s00034-013-9727-8

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-013-9727-8