Abstract

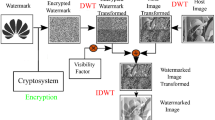

The paper focuses on the VLSI-based digital design and implementation of reversible image watermarking (RIW) architecture using difference expansion (DE). Mathematical simplicity of using a set of linear transformations leads to the choice of DE-based technique for developing hardware design. Moreover, its high performance gain in terms of payload capacity and the visual quality of the watermarked images would make this hardware architecture useful for real-time application on security purpose of medical and military images. High-level synthesis approach with resource-constraint design makes the architecture novel that needs only single adder, subtractor, multiplier, and divider along with 20 registers and 14 multiplexers for embedding. The number of resource required is same for watermark decoding with a modified schedule, which is the specialty of this design. The results obtained after implementation of the architecture on Xilinx Virtex-7 Field Programmable Gate Array (FPGA), Zynq-7000 programmable System-on-Chip (SoC) show the viability of low cost, high speed and real-time use. To process an image block \((8 \times 8)\), the latency is 226.733 ns for 150 MHz clock with throughput 35.284 Mbps and the critical path for single cycle is 5.674 ns. The obtained structural similarity (SSIM) performance quality metric of the RIW algorithm from MATLAB simulation is compared with the SSIM obtained from hardware, and excellent agreements between them are observed.

Similar content being viewed by others

Change history

12 November 2018

The original version of the article unfortunately contained error in author group. Four authors were not submitted and published in the original version.

References

A.M. Alattar, Reversible watermark using the difference expansion of a generalized integer transform. IEEE Trans. Image Process. 13, 1147–1156 (2004)

A.M. Alattar, Reversible watermark using difference expansion of quads. IEEE Proc. Int. Conf. Acoust. Speech Signal Process. 3, 377–380 (2004)

A.M. Alattar, Reversible watermark using difference expansion of triplet. IEEE Proc. Int. Conf. Image Process. 1, 501–504 (2003)

M. Celik, G. Sharma, A.M. Tekalp, E. Saber, Lossless generalized-LSB data embedding. IEEE Trans. Image Process. 14, 253–266 (2005)

H.N. Choi, J.W. Kim, J.W. Choi, H.I. Kim, Reversible watermarking in JPEG compression domain. J. Korea Instit Inf Secur Cryptol 17, 121–130 (2007)

D. Coltuc, J.M. Chassery, Very fast watermarking by reversible contrast mapping. IEEE Signal Process. Lett. 14, 255–258 (2007)

I. Cox, M. Miller, B. Jeffrey, Digital watermarking: Principles and Practice (Morgan Kaufmann, Burlington, 2002)

C. Dragoi, D. Coltuc, Improved rhombus interpolation for reversible watermarking by difference expansion, in IEEE EUSIPCO, 1688–1692 (2012)

J. Fridrich, M. Goljan, R. Du, Invertible authentication watermark for JPEG images, in IEEE Proceedings of International Conference on Information Technology, 223–227 (2001)

A. Garimella, M. Satyanarayan, R.S. Kumar, P.S. Murugesh, U.C. Niranjan, VLSI implementation of online digital watermarking techniques with difference encoding for the 8-bit gray scale images, in Proceedings of International Conferrnce on VLSI Design, 283–288 (2003)

A. Gerimella, M.V.V. Satyanarayana, P.S. Murugesh, U.C. Niranjan, ASIC for digital color image watermarking. in IEEE Proceedings of 11th Digital Signal Processing Workshop and IEEE Signal Processing Education Workshop, 292–295 (2004)

S. Ghosh, S. Talapatra, N. Chatterjee, S.P. Maity, H. Rahaman, FPGA based implementation of embedding and decoding architecture for binary water-mark by spread spectrum scheme in spatial domain. Bonfring Int. J. Adv. Image Process. 2, 01–08 (2012)

K.S. Kim, M.J. Lee, H.Y. Lee, H.K. Lee, Reversible data hiding exploiting spatial correlation between sub-sampled images. Pattern Recognit. 42, 3083–3096 (2009)

E. Kougianos, S.P. Mohanty, R.N. Mahapatra, Hardware assisted watermarking for multimedia. Comput. Electr. Eng. 35, 339–358 (2009)

S. Lee, C.D. Yoo, T. Kalker, Reversible image watermarking based on integer to integer wavelet transform. IEEE Trans. Inf. Forensics Secur. 2, 321–330 (2007)

Y.C. Li, C.M. Yeh, C.C. Chang, Data hiding based on the similarity between neighboring pixels with reversibility. Digit. Signal Process. 20, 1116–1128 (2010)

S.L. Lin, C.F. Huang, M.H. Liou, C.Y. Chen, Improving histogram-based reversible information hiding by an optimal weight-based prediction scheme. J. Inf. Hiding Multimed. Signal Process. 4, 19–33 (2013)

H.K. Maity, S.P. Maity, C. Delpha, A modified RCM for reversible watermarking with FPGA implementation, in Proceedings of 4th European Workshop on Visual Information Processing, 100–105 (2013)

H.K. Maity, S.P. Maity, FPGA implementation of reversible watermarking in digital images using reversible contrast mapping. J. Syst. Softw. 96, 93–104 (2014)

S.P. Maity, M.K. Kundu, S. Maity, Dual purpose FWT domain spread spectrum image watermarking in real time. Comput. Electr. Eng. 35, 415–433 (2009)

S.P. Mohanty, E. Kougianos, N. Ranganathan, VLSI architecture and chip for combined invisible robust and fragile watermarking. IET Comput. Digit. Tech. 1, 600–611 (2007)

S.P. Mohanty, R. Kumara, S. Nayak, FPGA based implementation of an invisible-robust image watermarking encoder. Lect. Notes in Comput. Sci. 3356, 344–353 (2004)

S.P. Mohanty, N. Ranganathan, R.K. Namballa, VLSI implementation of invisible digital watermarking algorithms towards the development of a secure JPEG encoder, in IEEE Proceedings of Workshop on Signal Processing Systems, 183–188 (2003)

S.P. Mohanty, N. Ranganathan, R.K. Namballa, VLSI implementation of visible watermarking for a secure digital still camera design, in Proceedings of the 17th International Conference on VLSI Design, 1063–1068 (2004)

S.P. Mohanty, N. Ranganathan, R.K. Namballa, A VLSI architecture for visible watermarking in a secure still digital camera (S2DC) design. IEEE Trans. VLSI Syst. 13, 1002–1012 (2005)

G.R. Nelson, G.A. Jullien, O.Y. Pecht, CMOS image sensor with water-marking capabilities, in IEEE Proceedings of Conference on Circuits and Systems, 5326–5329 (2005)

Z. Ni, Y.Q. Shi, N. Ansari, W. Su, Reversible data hiding. IEEE Trans. Circuits Syst. Video Technol. 16, 354–362 (2006)

J. Seitz, Digital watermarking for digital media (University of Cooperative Education Heidenheim, Stuttgart, 2005)

Y.H. Seo, D.W. Kim, Real-time blind watermarking algorithm and its hard-ware implementation for motion JPEG2000 image codec, in Proceedings of 1st Workshop on Embedded Systems for Real Time Multimedia, (2003)

D.M. Thodi, J.J. Rodrguez, Expansion embedding techniques for reversible watermarking. IEEE Trans. Image Process. 16, 721–730 (2007)

J. Tian, Reversible data embedding using a difference expansion. IEEE Trans. Circuits Syst Video Technol. 13, 890–896 (2003)

T.H. Tsai, C.Y. Lu, A system level design for embedded digital watermark technique using in DSC system, in IEEE Proceedings of International Workshop on Intelligent Signal Processing and Communication Systems, (2001)

A. Van Leest, M. Van der Veen, F. Bruekers, Reversible image watermarking, in IEEE Proceedings of International Conferrence on Image Processing II, 731–734 (2003)

C.D. Vleeschouwer, J.E. Delaigle, B. Macq, Circular interpretation of histogram for reversible watermarking, in IEEE Proceedings of 4th Workshop on Multimedia Signal Processing, 345–350 (2001)

S. Weng, J.S. Pan, X. Gao, Reversible watermark combining pre-processing operation and histogram shifting. J. Inf. Hiding Multimed. Signal Process. 3, 320–326 (2012)

B. Yang, M. Schmucker, X. Niu, C. Busch, S. Sun, Reversible image watermarking by histogram modification for integer DCT coefficients, in IEEE Proceedings of 6th Workshop on Multimedia Signal Processing, 143–146 (2004)

D.G. Yeo, H.Y. Lee, B.M. Kim, High capacity reversible watermarking using differential histogram shifting and predicted error compensation. J. Electron. Imaging 20, 013001-1-12 (2011)

D.G. Yeo, H.Y. Lee, Block-based image authentication algorithm using differential histogram-based reversible watermarking. The Korea Inf. Process. Soc. Trans. Part B 18B, 355–364 (2011)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Das, S., Maity, R. & Maity, N.P. VLSI-Based Pipeline Architecture for Reversible Image Watermarking by Difference Expansion with High-Level Synthesis Approach. Circuits Syst Signal Process 37, 1575–1593 (2018). https://doi.org/10.1007/s00034-017-0609-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-017-0609-3