Abstract

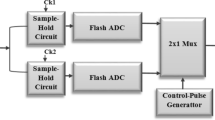

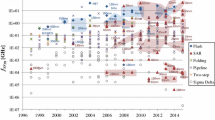

A 15-bit, 85 MS/s hybrid flash-SAR ADC is presented. The proposed design combines modified tri-level switching technique with split capacitor technique to improve the power efficiency and sampling rate of the SAR block. The sampling switch was designed to achieve reduced settling time for DAC. Modified encoder block was used in flash ADC block and PMOS resistive ladder was used for better matching and linearity. To overcome high-frequency noise jitters in resistive ladder, parallel capacitors were added which act as low-pass filter. At 85 MS/s device consumes 650 uW and achieved an SNDR of 74.3 dB, ENOB of 12.06 with SFDR of 89 dBc. The proposed ADC is implemented in 1P-9M low K 90-nm CMOS process technology and occupies a chip area of 720 um \(\times \) 195 um.

Similar content being viewed by others

References

T.O. Anderson, Optimum control logic for successive approximation analog-to-digital converters. Deep Space Network Progress Report 13, 168–176 (1972)

A. Arian, M. Saberi, S. Hosseini-Khayat, R. Lotfi, Y. Leblebici, A 10-bit 50-MS/s redundant SAR ADC with split capacitive-array DAC. Analog Integr. Circuits Signal Process. 71(3), 583–589 (2012). doi:10.1007/s10470-011-9812-5

S. Brenna, A. Bonfanti, A. Abba, F. Caponio, A.L. Lacaita, Analysis and optimization of a SAR ADC with attenuation capacitor, in 37th International Convention on Information and Communication Technology, Electronics and Microelectronics, MIPRO 2014-Proceedings (April 2016) (2014) pp. 68–73. doi:10.1109/MIPRO.2014.6859535

M. Chahardori, M. Sharifkhani, S. Sadughi, A 4-bit, 1.6 GS/s low power flash ADC, based on offset calibration and segmentation. IEEE Trans. Circuits Syst. I Regul Pap 60(9), 2285–2297 (2013). doi:10.1109/TCSI.2013.2246206

Y. Chen, S. Tsukamoto, T. Kuroda, A 9b 100 MS/s 1.46 mW SAR ADC in 65 nm CMOS, in Proceedings of Technical Papers-2009 IEEE Asian Solid-State Circuits Conference, A-SSCC 2009 (IEEE, 2009), pp. 145–148. doi:10.1109/ASSCC.2009.5357199

D. De Venuto, D.T. Castro, Y. Ponomarev, E. Stikvoort, 0.8 uw 12-bit SAR ADC sensors interface for RFID applications. Microelectron. J. 41(11), 746–751 (2010). doi:10.1016/j.mejo.2010.06.019

H. Fan, X. Han, Q. Wei, H. Yang, A 12-bit self-calibrating SAR ADC achieving a Nyquist 90.4-dB SFDR. Analog Integr. Circuits Signal Process. 74(1), 239–254 (2013). doi:10.1007/s10470-012-9977-6

M. Goswami, D. Varma, B. Singh, Reduced comparator high speed low power ADC using 90 nm CMOS technology. Analog Integr. Circuits Signal Process. 74(1), 267–278 (2013). doi:10.1007/s10470-012-9959-8

P. Harikumar, J.J. Wikner, A 10-bit 50MS/s SAR ADC in 65nm CMOS with on chip reference voltage buffer. Integr. VLSI J. 50, 28–38 (2015). doi:10.1016/j.vlsi.2015.01.002

G.Y. Huang, S.J. Chang, C.C. Liu, Y.Z. Lin, 10-bit 30-MS/s SAR ADC using a switchback switching method. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 21(3), 584–588 (2013). doi:10.1109/TVLSI.2012.2190117

R. Kapusta, J. Shen, S. Decker, H. Li, E. Ibaragi, H. Zhu, A 14b 80 MS/s SAR ADC With 73.6 dB SNDR in 65 nm CMOS. IEEE J. Solid State Circuits 48(12), 3059–3066 (2013). doi:10.1109/JSSC.2013.2274113

J.I. Kim, B.R.S. Sung, W. Kim, S.T. Ryu, A 6-b 4.1-GS/s flash ADC with time domain latch interpolation in 90-nm CMOS. IEEE J. Solid State Circuits 48(6), 1429–1441 (2013). doi:10.1109/JSSC.2013.2252516

A. Larsson, J. Silva-Martinez, E.G. Soenen, A 360 fJ/conversion-step, 14-bit, 100 MS/s, digitally background calibrated pipelined ADC in 130-nm CMOS. Analog Integr. Circuits Signal Process. 81(1), 153–164 (2014). doi:10.1007/s10470-014-0376-z

S. Lee, A.P. Chandrakasan, H.S. Lee, A 1 GS/s 10b 18.9 mW time-interleaved SAR ADC with background timing skew calibration. IEEE J. Solid State Circuits 49(12), 2846–2856 (2014). doi:10.1109/JSSC.2014.2362851. http://ieeexplore.ieee.org/document/6936944/

J.S. Lee, I.C. Park, Capacitor array structure and switch control for energy-efficient SAR analog-to-digital converters, in Proceedings—IEEE International Symposium on Circuits and Systems (IEEE, 2008), pp. 236–239. doi:10.1109/ISCAS.2008.4541398

Y.Z. Lin, C.C. Liu, G.Y. Huang, Y.T. Shyu, Y.T. Liu, S.J. Chang, A 9-bit 150 MS/s subrange ADC based on SAR architecture in 90-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 60(3), 570–581 (2013). doi:10.1109/TCSI.2012.2215756

J. McCreary, P. Gray, All-MOS charge redistribution analog-to-digital conversion techniques I. IEEE J. Solid State Circuits 10(6), 371–379 (1975). doi:10.1109/JSSC.1975.1050629

G.G. Oh, C.K. Lee, S.T. Ryu, A 10-bit 40-MS/s pipelined ADC with a wide range operating temperature for WAVE applications. IEEE Trans. Circuits Syst. II Express Br. 61(1), 6–10 (2014). doi:10.1109/TCSII.2013.2290910

A. Sanyal, N. Sun, An energy efficient low frequency-dependence switching technique for SAR ADCs. IEEE Trans. Circuits Syst. II Express Br. 61(5), 294–298 (2014). doi:10.1109/TCSII.2014.2304890

D. Schinkel, E. Mensink, E. Klumperink, E. van Tuijl, B. Nauta, A double-tail latch-type voltage sense amplifier with 18ps setup+hold time, in 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers (IEEE, 2007), pp. 314–605. doi:10.1109/ISSCC.2007.373420

M. Taherzadeh-Sani, R. Lotfi, F. Nabki, A 10-bit 110 kS/s 1.16 uW SA-ADC with a hybrid differential/single-ended DAC in 180-nm CMOS for multichannel biomedical applications. IEEE Trans. Circuits Syst. II Express Br. 61(8), 584–588 (2014). doi:10.1109/TCSII.2014.2327373

C.J. Tseng, Y.C. Hsieh, C.H. Yang, H.S. Chen, A 10-bit 200 MS/s capacitor-sharing pipeline ADC. IEEE Trans. Circuits Syst. I Regul. Pap. 60(11), 2902–2910 (2013). doi:10.1109/TCSI.2013.2256212

M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. Klumperink, B. Nauta, A 1.9 uW 4.4 fJ/conversion-step 10 bit 1 MS/s charge-redistribution ADC, in 2008 IEEE International Solid-State Circuits Conference—Digest of Technical Papers (IEEE, 2008), pp. 244–610. doi:10.1109/ISSCC.2008.4523148

Y. Wu, X. Cheng, X. Zeng, A 960 uw 10-bit 70-MS/s SAR ADC with an energy efficient capacitor-switching scheme. Microelectron. J. 44(12), 1260–1267 (2013). doi:10.1016/j.mejo.2013.08.012

F. Ye, L. Cheng, K. Lin, J. Ren, An 80-MS/s 14-bit pipelined ADC featuring 83 dB SFDR. Analog Integr. Circuits Signal Process. 63(3), 503–508 (2010). doi:10.1007/s10470-009-9451-2

Y. Yee, L. Terman, L. Heller, A two-stage weighted capacitor network for D/A-A/D conversion. IEEE J. Solid State Circuits 14(4), 778–781 (1979). doi:10.1109/JSSC.1979.1051264

M. Yip, A.P. Chandrakasan, A resolution-reconfigurable 5-to-10-Bit 0.4-to-1 V power scalable SAR ADC for sensor applications. IEEE J. Solid State Circuits 48(6), 1453–1464 (2013). doi:10.1109/JSSC.2013.2254551

C. Yuan, Y.Y.H. Lam, A 281-nW 43.3 fJ/conversion-step 8-ENOB 25-kS/s asynchronous SAR ADC in 65 nm CMOS for biomedical applications, in Proceedings IEEE International Symposium on Circuits and Systems (IEEE, 2013), pp. 622–625. doi:10.1109/ISCAS.2013.6571919

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48(9), 482 (2012). doi:10.1049/el.2011.4001

Z. Zhu, Y. Xiao, W. Wang, Y. Guan, L. Liu, Y. Yang, A 1.33 uW 10-bit 200 KS/s SAR ADC with a tri-level based capacitor switching procedure. Microelectron. J. 44(12), 1132–1137 (2013). doi:10.1016/j.mejo.2013.06.018

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Razzaq, A., Chaudhry, S.M. A 15-Bit 85 MS/s Hybrid Flash-SAR ADC in 90-nm CMOS. Circuits Syst Signal Process 37, 1452–1478 (2018). https://doi.org/10.1007/s00034-017-0629-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-017-0629-z