Abstract

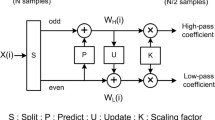

Data-access scheme affects the complexity of parallel architectures performing computation of multi-level two-dimensional (2-D) discrete wavelet transform (DWT). In this paper, we made a study on the data-access schemes considered in the existing parallel 2-D DWT architectures. Based on this study, a novel data-access scheme is proposed to avoid data multiplexing, which is common in the existing parallel architectures. Further, a block formulation is presented for vector computation of multi-level lifting 2-D DWT. A generic design of processing unit for computing one-level 2-D DWT is derived using the proposed block formulation. The proposed generic design resizes by a single parameter, i.e., the input-vector size. A regular and modular parallel architecture is derived using the generic processing unit design. The proposed parallel architecture easily scalable for higher block sizes as well as higher DWT levels without sacrificing its circuit regularity and modularity. This is an important feature of the proposed architecture. Comparison result shows that the proposed architecture for three-level DWT and block size 64 offers a saving in 24% area–delay–product (ADP) and 10% power consumption, and higher saving for higher block sizes than the best available similar structure without any overhead memory unlike the existing structure.

Similar content being viewed by others

References

C. Cheng, K.K. Parhi, High-speed VLSI implementation of 2-D discrete wavelet transform. IEEE Trans. Signal Process. 56(1), 393–403 (2008)

Y. Hu, C.C. Jong, A memory-efficient high-throughput architecture for lifting-based multi-level 2-D DWT. IEEE Trans. Signal Process. 61(20), 4975–4987 (2013)

W. Jiang, A. Ortega, Lifting factorization-based discrete wavelet transform architecture design. IEEE Trans. Circuits Syst. Video Technol. 11(5), 651–657 (2001)

Y.K. Lai, L.F. Lien, Y.C. Shih, A high-performance and memory-efficient VLSI architecture with parallel scanning method for 2-D lifting-based discrete wavelet transform. IEEE Trans. Consum. Electron. 55(2), 400–407 (2009)

H.Y. Liao, M.K. Mandal, B.F. Cockburn, Efficient architectures for 1-D and 2-D lifting-based wavelet transforms. IEEE Trans. Signal Process. 52(5), 1315–1326 (2004)

Y. Meyer, Wavelets: Algorithms and Applications (Society for Industrial and Applied Mathematics, Philadelphia, 1993)

P.K. Meher, B.K. Mohanty, J.C. Patra, Hardware-efficient systolic-like modular design for two-dimensional discrete wavelet transform. IEEE Trans. Circuits Syst. II Express Briefs 55(2), 151–155 (2008)

B.K. Mohanty, P.K. Meher, Memory efficient modular VLSI architecture for high throughput and low-latency implementation of multilevel lifting 2-D DWT. IEEE Trans. Signal Process. 59(5), 2072–2084 (2011)

B.K. Mohanty, P.K. Meher, Memory-efficient high-speed convolution-based generic structure for multilevel 2-D DWT. IEEE Trans. Circuits Syst. Video Technol. 23(2), 353–363 (2012)

B.K. Mohanty, A. Mahajan, P.K. Meher, Area and power-efficient architecture for high-throughput implementation of lifting 2-D DWT. IEEE Trans. Circuits Syst. II Express Briefs 59(7), 434–438 (2012)

B.K. Mohanty, P.K. Meher, T. Srikanthan, Critical-path optimization for efficient hardware realization of lifting and flipping DWTs, in IEEE International Symposium on Circuits and Systems (ISCAS, Portugal, 2015), pp. 1186–1189

B.K. Mohanty, A. Choubey, Efficient design for Radix-8 booth multiplier and its application in lifting 2-D DWT. Circuits Syst. Signal Process. (CSSP) 36, 1129–1149 (2017)

A. Skodars, C. Christopoulos, T.E. brahimi, The JPEG 2000 still image compression standard. IEEE Signal Process. Mag. 18(5), 36–58 (2001)

W. Sweldens, The lifting scheme: a custom-designed construction of bi-orthogonal wavelets. Appl. Comput. Harmon. Anal. 3(2), 186–200 (1996)

X. Tian, L. Wu, Y.-H. Tan, J.-W. Tian, Efficient multi-input/multi-output VLSI architecture for two-dimensional lifting-based discrete wavelet transform. IEEE Trans. Comput. 60(8), 1207–1211 (2011)

M. Vishwanath, The recursive pyramid algorithm for the discrete wavelet transform. IEEE Trans. Signal Process. 42(3), 673–676 (1994)

P.C. Wu, L.G. Chen, An efficient architecture for two-dimensional discrete wavelet transform. IEEE Trans. Circuits Syst. Video Technol. 11(4), 536–545 (2001)

C.Y. Xiong, J. Tian, J. Liu, Efficient architectures for two-dimensional discrete wavelet transform using lifting scheme. IEEE Trans. Image Process. 16(3), 607–614 (2007)

C. Zhang, C. Wang, M.O. Ahmad, A pipeline VLSI architecture for fast computation of the 2-D discrete wavelet transform. IEEE Trans. Circuits Syst. I Regul. Pap. 59(8), 1775–1785 (2012)

W. Zhang, Z. Jiang, Z. Gao, Y. Liu, An efficient VLSI architecture for lifting-based discrete wavelet transform. IEEE Trans. Circuits Syst. II Express Briefs 59(3), 158–162 (2012)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Choubey, A., Mohanty, B.K. Novel Data-Access Scheme and Efficient Parallel Architecture for Multi-level Lifting 2-D DWT. Circuits Syst Signal Process 37, 4482–4503 (2018). https://doi.org/10.1007/s00034-018-0775-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0775-y