Abstract

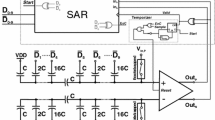

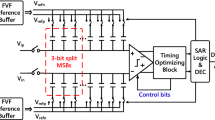

The required silicon die area of successive approximation analog-to-digital converters (SA-ADCs) increases rapidly with ADC resolution. In particular, a main design challenge for SA-ADCs is the number of unit capacitors required for the internal charge distribution capacitive-array digital-to-analog converter (DAC), which increases exponentially with a monotonic increase in the number of the output bits. Therefore, the overall performance of the final design is affected by the huge die area and, in turn, the switching energy of the capacitive-array DAC. In this article, a tiny-size MOSFET-only SA-ADC topology is proposed for those applications which require a low-resolution and moderate to high sampling-rate analog-to-digital converters prior to digital processing units. To this end, the widely used metal–insulator–metal (MIM) capacitors of mixed-signal CMOS technologies are replaced with area-efficient MOS capacitors available in every technology. The effectiveness of this implementation is validated through successful simulation of a 5-bit 20 MS/s MOSFET-only SA-ADC in a low-cost 0.18-µm digital CMOS technology. The ADC consumes a total power of 76.88 µW from a 1.2-V voltage supply, while it occupies a die size of only 190 µm2. This area is roughly 40% lower than 310 µm2, the die area of an equivalent design based on MIM capacitors.

Similar content being viewed by others

References

A.M. Abo, P.R. Gray, A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter. IEEE J. Solid-State Circuits 34, 599–606 (1999)

E. Alpman, H. Lakdawala, L.R. Carley, K. Soumyanath, A 1.1 V 50 mW 2.5 GS/s 7 b time-interleaved C-2C SAR ADC in 45 nm LP digital CMOS, in IEEE ISSCC Digest. Technical papers (2009), pp. 76–77

H. Aminzadeh, MOSFET-only pipelined analogue-to-digital converters: non-linearity compensation by digital calibration. Int. J. Electron. 101, 158–173 (2014)

H. Aminzadeh, MOSFET-only two-stage operational amplifiers with Miller compensation: design and fabrication in nano-scale CMOS. J. Circuits Syst. Comput. 22, 135006501–135006513 (2013)

H. Aminzadeh, R. Lotfi, K. Mafinezhad, Design of low-power single-stage operational amplifiers based on an optimized settling model. Analog Integr. Circuits Signal Process. 58, 153–160 (2009)

S.U. Ay, A sub-1 Volt 10-bit supply boosted SAR ADC design in standard CMOS. Analog Integr. Circuits Signal Process. 66, 213–221 (2011)

T.C. Carusone, D.A. Johns, K.W. Martin, Analog Integrated Circuit Design (Wiley, Hoboken, 2011)

Y. Chang, C.S. Wang C.K. Wang, A 8-bit 500-KS/s low power SAR ADC for bio-medical applications, in IEEE ASSCC Digest. Technical papers (2007), pp. 228–231

S.W.M. Chen, R.W. Brodersen, A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13-µm CMOS, in IEEE ISSCC Digest. Technical papers (2006), pp. 574–575

L. Chen, A. Sanyal, J. Ma, N. Sun, A 24-uW 11-bit 1-MS/s SAR ADC with a bidirectional single-side switching technique, in IEEE European Solid-State Circuits Conference (2014), pp. 219–222

R. Ding, H. Liang, S. Liu, A novel switching scheme and area-saving architecture for SAR ADC. Analog Integr. Circuits Signal Process. 91, 149–154 (2017)

Z. Fazel, S. Saeedi, M. Atarodi, Pipelining method for low-power and high-speed SAR ADC design. Analog Integr. Circuits Signal Process. 87, 353–368 (2016)

A.R. Ghasemi, M. Saberi, R. Lotfi, A low-power capacitor switching scheme with low common-mode voltage variation for successive approximation ADC. Microelectron. J. 61(12), 15–20 (2017)

B.P. Ginsburg, A.P. Chandrakasan, Dual time-interleaved successive approximation register ADCs for an ultra-wideband receiver. IEEE J. Solid-State Circuits 42, 247–257 (2007)

H.C. Hong, G.M. Lee, A 65-fJ/conversion-step 0.9-V 200 kS/s rail-to-rail 8-bit successive-approximation ADC. IEEE J. Solid-State Circuits 42, 2161–2168 (2007)

C.C. Liu, S.J. Chang, G.Y. Huang, Y.Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45, 731–740 (2010)

F. Maloberti, Data Converters (Springer, New York, 2007)

R. Ozgun, J. Lin, F. Tejada, P. Pouliquen, A.G. Andreou, A low-power 8-bit SAR ADC for a QCIF image sensor, in IEEE International Symposium on Circuits and Systems (2011), pp. 841–844

B. Razavi, Design of Analog CMOS Integrated Circuits (McGraw-Hill, New York City, 2001)

T. Tille, J. Sauerbrey, M. Mauthe, D. Schmitt-landsiedel, Design of low-voltage MOSFET only sigma-delta modulators in standard digital CMOS technology. IEEE Trans. Circuits Syst. I Regul. Pap. 51, 96–109 (2004)

T. Tille, J. Sauerbrey, D. Schmitt-Landsiedel, A 1.8-V MOSFET-only Σ∆ modulator using substrate biased depletion-mode MOS capacitors in series compensation. IEEE J. Solid-State Circuits 36, 1041–1047 (2001)

X.Y. Tong, Z.M. Zhu, Y.T. Yang, L.X. Liu, D/A conversion networks for high-resolution SAR A/D converters. Electron. Lett. 47, 169–171 (2011)

X. Wang, H. Huang, Q. Li, Design considerations of ultralow-voltage self-calibrated SAR ADC. IEEE Trans. Circuits Syst. II Express Briefs 62, 337–341 (2015)

A. Wu, J. Wu, J. Huang, Energy-efficient switching scheme for ultra-low voltage SAR ADC. Analog Integr. Circuits Signal Process. 90, 507–511 (2017)

L. Xie, G. Wen, J. Liu, Y. Wang, Energy-efficient hybrid capacitor switching scheme for SAR ADC. Electron. Lett. 50, 22–23 (2014)

H. Yoshizawa, Y. Huang, P.F. Ferguson, G.C. Temes, MOSFET-only switched-capacitor circuits in digital CMOS technology. IEEE J. Solid-State Circuits 34, 734–747 (1999)

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48, 482–483 (2012)

M. Zamprogno, A. Minuti, F. Girardi, P. Confalonieri, G. Nicollini, A 10-b 100-kS/s 1-mW general-purpose ADC for cellular telephones. IEEE Trans. Circuits Syst. II Express Briefs 59, 138–142 (2012)

J. Zhang, R. Ding, Z. Zhu, 99.2% energy saving and high-linearity switching method for SAR ADCs. Analog Integr. Circuits Signal Process. 91, 93–96 (2017)

Y. Zhu, C.H. Chan, U.F. Chio, S.W. Sin, U. Seng-Pan, R.P. Martins, F. Maloberti, A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45, 1111–1121 (2010)

Z. Zhu, Y. Xiao, X. Song, VCM-based monotonic capacitor switching scheme for SAR ADC. Electron. Lett. 49, 327–329 (2013)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Aminzadeh, H. A Low-Cost Tiny-Size Successive Approximation ADC for Applications Requiring Low-Resolution Conversion with Moderate Sampling Rate. Circuits Syst Signal Process 38, 242–258 (2019). https://doi.org/10.1007/s00034-018-0854-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0854-0