Abstract

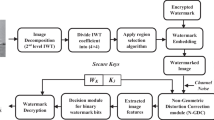

In this paper, a hardware implementation of a data hiding technique is proposed for efficient quality access control of images using lifting-based discrete wavelet transformation (DWT). Host image is decomposed into n-level wavelet tiles. A binary watermark image is transmuted and embedded into high–high DWT coefficients using adaptive dither modulation technique without self-noise suppression. The embedding of external information into the host image will degrade the visual quality. This feature may be utilized for access control. At the decoder side, an authorized user can enjoy superior quality image by extracting watermark bits using minimum distance decoding. Field-programmable gate array-based hardware architecture is proposed for real-time implementation of the scheme. The experiment is done over a large number of benchmark images, and the results are found to be superior to the related work which is present in the literature. It is also seen that (a) in real-time processing, the scheme saves 89.53% power than the related implementation found in the literature, and (b) a very high throughput of 23.8 MB/s is achieved for watermarking encoder and decoder, respectively, at a maximum operating frequency of 130.14 MHz for the processing of (512 × 512) sized images.

Similar content being viewed by others

References

H. Belhadj, V. Aggrawal, A. Pradhan, A. Zerrouki, Power-aware FPGA design. Actel Corporation White Paper. 75 (2009)

K.D. Buch, Low power architecture and HDL coding practices for on-board hardware applications (2018). https://nepp.nasa.gov/mapld_2009/talks/…/Buch_Kaushal%20D._mapld09_pres_2.ppt. Accessed 09 Mar 2018

J. Chen, W. Hong, T.S. Chen, C.W. Shiu, Steganography for BTC compressed images using no distortion technique. Imaging Sci. J. 58(4), 177–185 (2010)

D. Coltuc, Low distortion transform for reversible watermarking. IEEE Trans. Image Process. 21(1), 412–417 (2012)

A.D. Darji, T.C. Lad, S.N. Merchant, A.N. Chandorkar, Watermarking hardware based on wavelet coefficients quantization method. Circuits Syst. Signal Process. 32(6), 2559–2579 (2013)

S. Das, R. Maity, N.P. Maity, VLSI-based pipeline architecture for reversible image watermarking by difference expansion with high-level synthesis approach. Circuits Syst. Signal Process. 37(4), 1575–1593 (2018)

P. Garrault, B. Philofsky, HDL coding practices to accelerate design performance. Xilinx White Paper # 231, pp. 1–22 (2006)

A. Gerimella, M.V.V. Satyanarayana, P.S. Murugesh, U.C. Niranjan, ASIC for digital color image watermarking, in Proceedings of IEEE 11th Digital Signal Processing Workshop and IEEE Signal Processing Education Workshop, vol 1, pp. 292–295 (2004)

S. Ghosh, B. Kundu, D. Datta, S.P. Maity, H. Rahaman, Design and implementation of fast FPGA based architecture for reversible watermarking, in Proceeding of International Conference on Electrical Information and Communication Technology, vol 1, pp. 1–6 (2013)

R.C. Gonzalez, R.E. Woods, S.L. Eddins, Digital Image Processing using MATLAB (Pearson Education, Upper Saddle River, 2005)

R. Grosbois, P. Gerbelot, T. Ebrahimi, Authentication and access control in the JPEG 2000 compressed domain, in Proceeding of SPIE 46th Annual Meeting, Applications of Digital Image Processing, vol. 1, pp. 95–104 (2001)

S.J. Horng, D. Rosiyadi, P. Fan, X. Wang, M.K. Khan, An adaptive watermarking scheme for e-government document images. Multimed. Tools Appl. 72(3), 3085–3103 (2014)

Image Database. http://www.cl.cam.ac.uk/fapp2/watermarking. (2010). Accessed 2010.

Image Database. http://www.petitcolas.net/fabien/watermarking/image_database/index.html. (2010). Accessed 2010.

C. Jin, J. Peng, Robustness of a blind image watermark detector designed by orthogonal projection. Electron Lett. Comput. Vis. Image Anal. 4, 11–20 (2004)

R. Karri, K. Wu, P. Mishra, Y. Kim, Concurrent error detection schemes for fault-based side-channel cryptanalysis of symmetric block ciphers. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 21(1), 1509–1517 (2002)

P. Karthigaikumar, K. Baskaran, FPGA and ASIC implementation of robust invisible binary image watermarking algorithm using connectivity preserving criteria. Microelectron. J. 42(1), 82–88 (2011)

C. Kim, D. Shin, L. Leng, C.-N. Yang, Lossless data hiding for absolute moment block truncation coding using histogram modification. J. Real-Time Image Proc. 14(1), 101–114 (2018)

R. Kountchev, M. Milanova, R. Kountcheva, Content protection and hierarchical access control in image databases, in Proceeding of International Symposium on Innovations in Intelligent Systems and Applications, vol. 1, pp. 1–6 (2015)

S.L. Lin, C.F. Huang, M.H. Liou, C.Y. Chen, Improving histogram-based reversible information hiding by an optimal weight-based prediction scheme. J. Inf. Hiding Multimed. Signal Process. 4(1), 19–33 (2013)

J. Liu, K. She, A hybrid approach of DWT and DCT for rational dither modulation watermarking. Circuits Syst Signal Process. 31(2), 797–811 (2012)

C.C. Lo, Y.C. Hu, W.L. Chen, C.M. Wu, Reversible data hiding scheme for BTC-compressed images based on histogram shifting. Int J Secur Appl. 8(2), 301–314 (2014)

M. Maes, T. Kalker, J.P. Linnartz, J. Talstra, F.G. Depovere, J. Haitsma, Digital watermarking for DVD video copy protection. IEEE Signal Process. Mag. 17(5), 47–57 (2000)

S.P. Maity, M.K. Kundu, Distortion free image-in-image communication with implementation in FPGA. AEU Int. J. Electron Commun. 67(1), 438–447 (2013)

H.K. Maity, S.P. Maity, FPGA implementation of reversible watermarking in digital image using reversible contrast mapping. J. Syst. Softw. 96(1), 93–104 (2014)

H.K. Maity, S.P. Maity, C. Delpha, A modified RCM for reversible watermarking with FPGA implementation, in Proceeding of 4th European Workshop on Visual Information Processing, pp. 100–105 (2013)

S.P. Mohanty, E. Kougianos, N. Ranganathan, VLSI architecture and chip for combined invisible robust and fragile watermarking. IET Comput. Digital Tech. 1(5), 600–611 (2007)

S.P. Mohanty, N. Ranganathan, K. Balakrishnan, A dual voltage frequency VLSI chip for image watermarking in DCT domain. IEEE Trans. Circuits Syst. II Express Briefs 53(5), 394–398 (2006)

S.P. Mohanty, N. Ranganathan, R.K. Namballa, VLSI implementation of visible watermarking for a secure digital still camera design, in Proceeding of 17th International Conference on VLSI Design, vol 1, pp. 1063–1068 (2004)

M. Nagabushanam, S. Ramachandran, Fast implementation of lifting based 1D/2D/3D DWT-IDWT architecture for image compression. Int. J. Comput. Appl. 51(6), 35–45 (2012)

A. Phadikar, S.P. Maity, M.K. Kundu, Quantization based data hiding scheme for efficient quality access control of images using DWT via lifting, in Proceeding of Sixth Indian Conference on Computer Vision, Graphics & Image Processing, vol. 1, pp. 265–272 (2008)

A. Phadikar, H. Mandal, G. Maity, T.L. Chiu, A new model of QIM data hiding for quality access control of digital image, in Proceeding of IEEE International Conference on Soft-Computing and Networks Security, vol. 1, pp. 1–5 (2015)

A.V. Subramanyam, S. Emmanuel, M.S. Kankanhalli, Robust watermarking of compressed and encrypted JPEG2000 images. IEEE Trans. Multimed. 14(3), 703–716 (2012)

W. Sun, Z.M. Lu, Y.C. Wen, F.X. Yu, R.J. Shen, High performance reversible data hiding for block truncation coding compressed images. SIViP 7(2), 297–306 (2013)

Z. Wang, A.C. Bovik, H.R. Sheikh, E.P. Simoncelli, Image quality assessment: from error measurement to structural similarity. IEEE Trans. Image Process. 13(4), 600–612 (2004)

S. Weng, J.S. Pan, X. Gao, Reversible watermark combining pre-processing operation and histogram shifting. J Inf Hiding Multimed. Signal Process. 3(4), 320–326 (2012)

L. Wilson, International technology roadmap for semiconductors (ITRS). Semiconductor Industry Association (2013)

I.K. Yeo, H.J. Kim, Generalized patchwork algorithm for image watermarking. Multimed. Syst. 9(3), 261–265 (2003)

W. Zhu, M.V. Wickerhauser, Discrete wavelet transforms in practice. https://www.math.wustl.edu/~victor/talks/mvwpmf2.pdf. (2009). Accessed 09 Mar 2018

Acknowledgements

This study was supported by the Ministry of Science and Technology (MOST), Taiwan R.O.C., under Grant Number MOST 107-3113-E-155-001-CC2,106-3113-E-155-001-CC2, 106-2221-E-155-036, 105-3113-E-155-001, 104-3113-E-155-001, 103-3113-E-155-001, 103-2221-E-155-028-MY3.

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Phadikar, A., Maity, G.K., Chiu, TL. et al. FPGA Implementation of Lifting-Based Data Hiding Scheme for Efficient Quality Access Control of Images. Circuits Syst Signal Process 38, 847–873 (2019). https://doi.org/10.1007/s00034-018-0893-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0893-6