Abstract

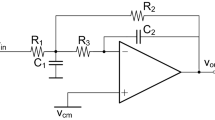

This work presents and validates the design of a four-quadrant analog multiplier based on the bulk-driven technique. Using the source–gate as well as the bulk–source voltages of a PMOS transistor as input ports, the multiplication task can be achieved. The AC signals are injected into the bulk terminals by means of a very-low-frequency programmable high-pass RC network which also serves to set its proper DC operation point. Although two RC networks are required, this multiplication cell is composed of only seven PMOS transistors and two coupling capacitors which makes it a very compact circuit. Furthermore, no preprocessed signals like the sum of \(\pm \,v_x \pm \,v_y\) are required at the input ports. The implemented circuit shows a bandwidth of 50 MHz for an output capacitance of 40 pF and a THD lower than 1\(\%\) for gate/bulk input amplitudes below 0.2 Vp. The power consumption of the multiplication core is 660 \(\upmu \)W and 2.6 mW including output buffers. In order to simulate and fabricate this circuit, an ON Semi 0.50 \(\upmu \)m CMOS standard technology is used, showing a silicon area consumption of \(280\,\upmu \hbox {m} \times 400\,\upmu \)m including output buffers. The proposed multiplier is suitable for biomedical, AM modulation, base-band modulation and analog computation.

Similar content being viewed by others

References

B.J. Blalock, S.A. Jackson, A 1.2-V CMOS four-quadrant analog multiplier, in 1999 Southwest Symposium on Mixed-Signal Design (Cat. No.99EX286), Tucson, AZ (1999), pp. 1–4

B. Boonchu, W. Surakampontorn, CMOS voltage-mode analog multiplier, in 2006 IEEE International Symposium on Circuits and Systems, Island of Kos (2006)

C. Chen, Z. Li, A low-power CMOS analog multiplier. IEEE Trans. Circuits Syst. II Express Briefs 53(2), 100–104 (2006)

D. Coue, G. Wilson, A four-quadrant subthreshold mode multiplier for analog neural-network applications. IEEE Trans. Neural Netw. 7(5), 1212–1219 (1996)

M. Dei, N. Nizza, G.M. Lazzerini, P. Bruschi, M. Piotto, A four quadrant analog multiplier based on a novel CMOS linear current divider, 2009 Ph.D. Research in Microelectronics and Electronics, Cork, pp. 128–131 (2009)

B. Gilbert, A precise four-quadrant multiplier with subnanosecond response. IEEE J. Solid State Circuits 3(4), 365–373 (1968)

A. Hadiashar, J.L. Dawson, A chopper stabilized CMOS analog multiplier with ultra low DC offsets, in 2006 Proceedings of the 32nd European Solid-State Circuits Conference, Montreux (2006), pp. 364–367

G. Han, E. Sanchez-Sinencio, CMOS transconductance multipliers: a tutorial. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 45(12), 1550–1563 (1998)

C.L. Kuo, B.J. Huang, C.C. Kuo, K.Y. Lin, H. Wang, A 10 to 35 GHz low power bulk-driven mixer using 0.13 um CMOS process. IEEE Microw. Wirel. Componen. Lett. 18(7), 455–457 (2008)

Z. Li, C. Chen, Low-power low-noise CMOS analogue multiplier. IEE Proc. Circuits Devices Syst. 153(3), 261–267 (2006)

W. Machowski, S. Kuta, J. Jasielski, Four-quadrant analog multiplier based On CMOS inverters, in Proceedings of the International Conference Mixed Design of Integrated Circuits and System, MIXDES 2006, Gdynia (2006), pp. 290–293

W. Machowski, S. Kuta, J. Jasielski, W. Koodziejski, Broadband quarter-square 4Q analog multiplier based on CMOS inverters, in ICSES 2010 International Conference on Signals and Electronic Circuits, Gliwice (2010), pp. 237–240

W. Machowski, S. Kuta, J. Jasielski, W. Koodziejski, Quarter-square analog four-quadrant multiplier based on CMOS invertes and using low voltage high speed control circuits, in Proceedings of the 17th International Conference Mixed Design of Integrated Circuits and Systems—MIXDES 2010, Warsaw (2010), pp. 333–336

S.A. Mahmoud, Low voltage low power wide range fully differential CMOS four-quadrant analog multiplier, in 2009 52nd IEEE International Midwest Symposium on Circuits and Systems, Cancun (2009), pp. 130–133

A.H. Miremadi, A. Ayatollahi, A. Abrishamifar, A. Siadatan, A low voltage CMOS analog multiplier with high linearity, in 2009 European Conference on Circuit Theory and Design, Antalya (2009), pp. 257–262

P. Prommee, M. Somdunyakanok, K. Angkaew, A. Jodtang, K. Dejhan, Single low-supply and low-distortion CMOS analog multiplier, in IEEE International Symposium on Communications and Information Technology, 2005, ISCIT 2005 (2005), pp. 251–254

P. Prommee, M. Somdunyakanok, K. Poorahong, P. Phruksarojanakun, K. Dejhan, CMOS wide-range four-quadrant analog multiplier circuit, in 2005 International Symposium on Intelligent Signal Processing and Communication Systems (2005), pp. 197–200

A. Satapathy, S.K. Maity, S.K. Mandal, A flipped voltage follower based analog multiplier in 90nm CMOS process, in 2015 International Conference on Advances in Computer Engineering and Applications, Ghaziabad (2015), pp. 628–631

C. Sawigun, J. Mahattanakul, A low-voltage CMOS linear transconductor suitable for analog multiplier application, in 2006 IEEE International Symposium on Circuits and Systems, Island of Kos (2006), p. 4

A. Tajalli, Y. Leblebici, E.J. Brauer, Implementing ultra-high-value floating tunable CMOS resistors. Electron. Lett. 44(5), 349–350 (2008)

S.C. Yener, A. Uygur, H.H. Kuntman, Ultra low-voltage ultra low-power memristor based band-pass filter design and its application to EEG signal processing. Analog Integr. Circuits Signal Process. 89, 719–726 (2016)

Acknowledgements

The authors would like to thank to National Council of Science and Technology (CONACyT), Mexico, for the scholarships \(\#\)371630 and \(\#\)477685.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zamora-Mejia, G., Diaz-Armendariz, A., Santiago-Ramirez, H. et al. Gate and Bulk-Driven Four-Quadrant CMOS Analog Multiplier. Circuits Syst Signal Process 38, 1547–1560 (2019). https://doi.org/10.1007/s00034-018-0945-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0945-y