Abstract

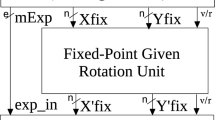

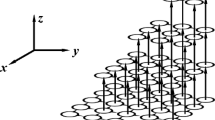

This paper presents a new algorithm for implementing exact Givens rotation for use in QR matrix decomposition. The algorithm is based on constant multipliers to perform multiple angle rotations in parallel, reducing latency and gate count, and is called multi-angle constant multiplier. Complexity and optimal angle division sequences have been studied for up to 20 bits of precision. Bit-exact software implementation of the algorithm was used in QR decomposition of \(4\times 4\) matrices with 16 bits of precision, and its numerical stability was extensively tested. QR decomposition was implemented in Xilinx Virtex 6, where pipelining strategies for latency-operating frequency trade-offs have been considered.

Similar content being viewed by others

References

AC Datatypes v3.7 (2016). https://www.mentor.com/hls-lp/downloads/ac-datatypes. Accessed June 2016

P.L. Chiu, L.Z. Huang, L.W. Chai, Y.H. Huang, Interpolation-based QR decomposition and channel estimation processor for MIMO-OFDM system. IEEE Trans. Circuits Syst. I Regul. Pap. 58(5), 1129–1141 (2011). https://doi.org/10.1109/TCSI.2010.2092090

A.G. Dempster, M.D. Macleod, Constant integer multiplication using minimum adders. IEE Proc. Circuits Devices Syst. 141(5), 407–413 (1994)

A.G. Dempster, M.D. Macleod, Use of minimum-adder multiplier blocks in FIR digital filters. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 42(9), 569–577 (1995)

M.D. Ercegovac, T. Lang, Digital Arithmetic (Elsevier, Amsterdam, 2004)

G.H. Golub, C.F. Van Loan, Matrix Computations, vol. 3, 3rd edn. (JHU Press, Baltimore, 2003)

X. Hu, R. Harber, S. Bass, Expanding the range of convergence of the CORDIC algorithm. IEEE Trans. Comput. 40(1), 13–21 (1991). https://doi.org/10.1109/12.67316

Z.Y. Huang, P.Y. Tsai, Efficient implementation of QR decomposition for gigabit MIMO-OFDM systems. IEEE Trans. Circuits Syst. I Regul. Pap. 58(10), 2531–2542 (2011). https://doi.org/10.1109/TCSI.2011.2123770

J.S. Lin, Y.T. Hwang, S.H. Fang, P.H. Chu, M.D. Shieh, Low-complexity high-throughput QR decomposition design for MIMO systems. IEEE Trans. Very Large Scale Integr. Syst. 23(10), 2342–2346 (2015). https://doi.org/10.1109/TVLSI.2014.2361906

L. Ma, K. Dickson, J. McAllister, J. McCanny, QR decomposition-based matrix inversion for high performance embedded MIMO receivers. IEEE Trans. Signal Process. 59(4), 1858–1867 (2011). https://doi.org/10.1109/TSP.2011.2105485

P. Meher, J. Valls, J. Tso-Bing, K. Sridharan, K. Maharatna, 50 Years of CORDIC: algorithms, architectures, and applications. IEEE Trans. Circuits Syst. I Regul. Pap. 56(9), 1893–1907 (2009). https://doi.org/10.1109/TCSI.2009.2025803

S.D. Munoz, J. Hormigo, High-throughput FPGA implementation of QR decomposition. IEEE Trans. Circuits Syst. II Express Briefs 62(9), 861–865 (2015)

Spiral: Software/Hardware Generation for DSP Algorithms (2016). http://spiral.ece.cmu.edu/mcm/gen.html. Accessed June 2016

Y. Voronenko, M. Püschel, Multiplierless multiple constant multiplication. ACM Trans. Algorithms (TALG) 3(2), 11 (2007)

C. Zhang, H. Prabhu, Y. Liu, L. Liu, O. Edfors, V. wall, Energy efficient group-sort QRD processor with on-line update for MIMO channel pre-processing. IEEE Trans. Circuits Syst. I Regul. Pap. 62(5), 1220–1229 (2015). https://doi.org/10.1109/TCSI.2015.2402936

W. Zhao, J. Lin, S.C. Chan, Throughput/area efficient FPGA implementation of QR decomposition for MIMO systems, in 2016 IEEE International Conference on Digital Signal Processing (DSP) (2016), pp. 522–526. https://doi.org/10.1109/ICDSP.2016.7868612

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Grujić, D.N., Saranovac, L. Multi-angle Constant Multiplier Givens Rotation Algorithm. Circuits Syst Signal Process 38, 4229–4244 (2019). https://doi.org/10.1007/s00034-019-01060-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-019-01060-x