Abstract

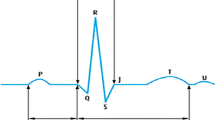

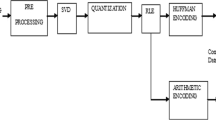

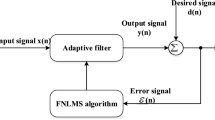

Electrocardiogram monitoring is crucial for the prevention and treatment of cardiovascular diseases. To record the electrical activity of different regions of the heart and manage the signals generated for long-term monitoring, a compression algorithm is necessary. This letter presents a novel compressor and decompressor able to support 3-lead compression without increasing hardware costs and area. The experimental results demonstrated that the bit compression ratio and power consumption can be improved by the proposed architecture. The effectiveness of this approach was verified by fabricating a chip using 0.18-\(\upmu \hbox {m}\) complementary metal-oxide-semiconductor technology. The proposed encoder has an operating frequency of 20 MHz and a gate count of 4.8K, and the proposed decoder has an operating frequency of 10 MHz and a gate count of 4.8K.

Similar content being viewed by others

References

C.A. Chen, S.L. Chen, H.Y. Huang, C.H. Luo, An efficient micro control unit with a reconfigurable filter design for wireless body sensor networks (WBSNs). Sensors 12, 16211–162270 (2012)

S.L. Chen, G.A. Luo, T.L. Lin, Efficient fuzzy-controlled and hybrid entropy coding strategy lossless ECG encoder VLSI design for wireless body sensor networks. Electron. Lett. 49, 1058–1060 (2013)

S.L. Chen, M.C. Tuan, T.K. Chi, T.L. Lin, VLSI architecture of lossless ECG compression design based on fuzzy decision and optimisation method for wearable devices. Electron. Lett. 51, 1409–1411 (2015)

S.L. Chen, J.G. Wang, VLSI implementation of low-power cost-efficient lossless ECG encoder design for wireless healthcare monitoring application. Electron. Lett. 49, 91–93 (2013)

K. Li, Y. Pan, F. Chen, K.-T. Cheng, R. Huan, Real-time lossless ECG compression for low-power wearable medical devices based on adaptive region prediction. Electron. Lett. 50, 1904–1906 (2014)

Y.H. Tseng, Y.H. Chen, C.W. Lu, Adaptive Integration of the Compressed Algorithm of CS and NPC for the ECG Signal Compressed Algorithm in VLSI Implementation. Sensors 17, 2288 (2017)

WHO, Global Status Report on Noncommunicable Disease 2014, World Health Organization: Geneva, Switzerland, (2015)

Acknowledgements

The authors would like to acknowledge chip fabrication support provided by Taiwan Semiconductor Research Institute (TSRI), Taiwan, R. O. C. The authors would like to thank the Particle Physics and Beam Delivery Core Laboratory of Institute for Radiological Research, Chang Gung University/Chang Gung Memorial Hospital, Linkou, for their assistance.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This work was supported in part by the Ministry of Science and Technology of Taiwan under project MOST 107-2221-E-182-066 and the Chang Gung Memorial Hospital, Linkou under project CMRPD2H0301, CMRPD2G0312, CMRPD2H0051, and CIRPD2F0013.

Rights and permissions

About this article

Cite this article

Chen, YH., Tseng, YH., Chu, PH. et al. VLSI Implementation of a Cost-Efficient 3-Lead Lossless ECG Compressor and Decompressor. Circuits Syst Signal Process 39, 1665–1671 (2020). https://doi.org/10.1007/s00034-019-01198-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-019-01198-8