Abstract

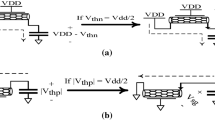

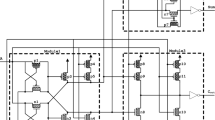

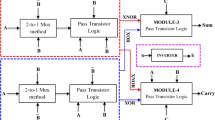

Using multi-valued logic can lead to reducing the interconnections in the chip. Reducing the interconnection, in turn, leads to decreasing the chip area and interconnections power dissipation. The design of the multi-valued logic circuits should be performed with the minimum complexity to fulfill the multi-valued logic aim. In the recent years, much research has been focused on the design of multi-valued logics in nanoelectronics due to the high capability of nanoelectronics to design them. In this paper, first, a novel single-supply ternary successor and predecessor are designed based on the multi-threshold voltage in CNFET, which is more energy efficient than those in the previous works. Then, these are used to design the ternary full adder. To reduce the number of transistors in the proposed full adder, the structure of this full adder is designed so that only one successor and predecessor are used and some common portions can be used in the sum and carry generator, and this is shown by equations. The number of transistors in the proposed single-supply full adder is reduced from 132 in the best previous single-supply full adder to 54. Also, to enhance the PDP, the successor and predecessor are used in the quad-state mode (‘0’, ‘1’, ‘2’ and ‘z’: high impedance), where in the ‘z’ mode, the direct current path is cut off. The circuits are simulated by the HSPICE software, using the Stanford 32 nm CNTFET library. The simulation results confirm the correct operation of the proposed circuit and PDP improvement in the proposed ternary full adder, which is about 81.12%, as compared to the best single supply reported in the previous works.

Similar content being viewed by others

Data Availability

The datasets generated during the current study are available from the corresponding author on reasonable request.

References

A. Akturk, G. Pennington, N. Goldsman, A. Wickenden, Electron transport and velocity oscillations in a carbon nanotube. IEEE Trans. Nanotechnol. 6(4), 469–474 (2007)

J. Appenzeller, Carbon nanotubes for high-performance electronics progress and prospect. Proc. IEEE 96(2), 201–211 (2008)

P.C. Balla, A. Antoniou, Low power dissipation MOS ternary logic family. IEEE J. Solid-State Circuits 19(5), 739–749 (1984)

A. Batchtold, P. Hadley, T. Nakanishi, C. Dekker, Logic circuits with carbon nanotube transistors. Science 294(5545), 1317–1320 (2001)

G. Cho, F. Lombardi, Design and process variation analysis of CNTFET-based ternary memory cells. Integr. VLSI J. 54, 97–108 (2016)

A. Daraei, S.A. Hosseini, Novel energy-efficient and high-noise margin quaternary circuits in nanoelectronics. AEU – Int. J. Electron. Commun. 105, 145–162 (2019)

J. Deng, H.-S.P. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—part I: model of the intrinsic channel region. IEEE Trans. Electron. Dev. 54(12), 3186–3194 (2007)

J. Deng, H.-S.P. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—part II: full device model and circuit performance benchmarking. IEEE Trans. Electron. Dev. 54(12), 3195–3205 (2007)

S. Etezadi, S.A. Hosseini, Novel ternary logic gates design in nanoelectronics. AEEE Adv. Electr. Electron. Eng. 17(3), 294–305 (2019)

S. Firouzi, S. Tabrizchi, F. Sharifi, A.H. Badawy, High performance, variation-tolerant CNFET ternary full adder a process, voltage, and temperature variation-resilient design. Comput. Electr. Eng. 77, 205–216 (2019)

H. Hashempour, F. Lombardi, Device model for ballistic CNFETs using the first conducting band. IEEE Des. Test Comput. 25(2), 178–186 (2008)

A. Heung, H.T. Mouftah, Depletion/enhancement CMOS for a lower power family of three-valued logic circuits. IEEE J. Solid-State Circuits 20(2), 609–616 (1985)

S.A. Hosseini, S. Etezadi, A novel very low-complexity multi-valued logic comparator in nanoelectronics. Circuits Syst. Signal Process. 39(4), 223–244 (2020)

S.A. Hosseini, S. Etezadi, Novel low storage power and high noise margin ternary memory cell in nanoelectronics. IET Circuits Dev. Syst. 13, 1751–8598 (2020). https://doi.org/10.1049/iet-cds.2019.0432

S.A. Hosseini, E. Roosta, A novel low complexity and energy-efficient method to implement quaternary logic function in nanoelectronics. Microelectron. J. (2020). https://doi.org/10.1016/j.mejo.2020.104821

P. Keshavarzian, R. Sarikhani, A Novel CNTFET-based ternary full adder. Circuits Syst. Signal Process. 33(3), 665–679 (2013)

Y. Lin, J. Appenzeller, J. Knoch, P. Avouris, High-performance carbon nanotube field-effect transistor with tunable polarities. IEEE Trans. Nanotechnol. 4(5), 481–489 (2005)

S. Lin, Y.B. Kim, F. Lombardi, The CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnol. 10(2), 217–225 (2011)

S. Lin, Y. Kim, F. Lombardi, Design of a ternary memory cell using CNTFETs. IEEE Trans. Nanotechnol. 11(5), 1019–1025 (2012)

M.S. Mastoori, F. Razaghian, A novel energy-efficient ternary successor and predecessor using CNTFET. Circuits Syst. Signal Process. 35(5), 875–895 (2015)

M.H. Moaiyeri, Z. Mehdizadeh Taheri, M. Rezaei Khezeli, A. Jalali, Efficient passive shielding of MWCNT interconnects to reduce crosstalk effects in multiple-valued logic circuits. IEEE Trans. Electromagn. Compat. 61(5), 1593–1601 (2019)

M. Mukaidono, Regular ternary logic functions—ternary logic functions suitable for treating ambiguity. IEEE Trans. Comput. 35(2), 179–183 (1986)

K. Rahbari, S.A. Hosseini, Novel ternary D-Flip-Flap-Flop and counter based on successor and predecessor in nanotechnology. AEU – Int. J. Electron. Commun. 109, 107–120 (2019)

A. Rahman, J. Guo, S. Datta, M.S. Lundstrom, Theory of ballistic nanotransistors. IEEE Trans. Electron Dev. 50(10), 1853–1864 (2003)

A. Raychowdhury, K. Roy, Carbon-nanotube-based voltage-mode multiple-valued logic design. IEEE Trans. Nanotechnol. 4(2), 168–179 (2005)

M. Rezaei Khezeli, M.H. Moaiyeri, A. Jalali, Active shielding of MWCNT bundle interconnects: an efficient approach to cancellation of crosstalk-induced functional failures in ternary logic. IEEE Trans. Electromagn. Compat. 61(1), 100–110 (2019)

M. Rezaei Khezeli, M.H. Moaiyeri, A. Jalali, Comparative analysis of simultaneous switching noise effects in MWCNT bundle and Cu power interconnects in CNTFET-based ternary circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 27(1), 37–46 (2019)

E. Roosta, S.A. Hosseini, A novel multiplexer-based quaternary full adder in nanoelectronics. Circuits Syst Signal Process. 38(9), 4056–4076 (2019)

M. Shahangian, S.A. Hosseini, S.H. Pishgar Komleh, Design of a multi-digit binary-to-ternary converter based on CNTFETs. Circuits Syst. Signal Process. 38(6), 2544–2563 (2019)

E. Shahrom, S.A. Hosseini, A new low power multiplexer based ternary multiplier using CNTFETs. AEU – Int. J. Electron. Commun. 93, 191–207 (2018)

F. Sharifi, M.H. Moaiyeri, K. Navi, N. Bagherzadeh, Robust and energy-efficient carbon nanotube FET-based MVL gates: A novel design approach. Microelectron. J. 46(12), 1333–1342 (2015)

F. Sharifi, A. Panahi, M.H. Moaiyeri, H. Sharifi, K. Navi, High performance CNFET-based ternary full adders. IETE J. Res. 64(1), 108–115 (2017)

T. Sharma, L. Kumre, CNTFET-based design of ternary arithmetic modules. Circuits Syst. Signal Process. 38(5), 4640–4666 (2019)

Stanford University CNFET model Website. Stanford University, Stanford, CA (2008). http://nano.stanford.edu/model.php?Id=23

S. Tabrizchi, A. Panahi, F. Sharifi, K. Navi, N. Bagherzadeh, Method for designing ternary adder cells based on CNFETs. IET Circuits Dev. Syst. 11(5), 465–470 (2017)

S. Tabrizchi, M.R. Taheri, K. Navi, N. Bagherzadeh, Novel CNFET ternary circuit techniques for high-performance and energy efficient design. IET Circuits Dev. Syst. 13(2), 193–202 (2019)

M. Takbiri, R. Faghih Mirzaee, K. Navi, Analytical review of noise margin in MVL: clarification of a deceptive matter. Circuits Syst. Signal Process. 38(9), 4280–4301 (2019)

S.J. Tans, A.R.M. Verschueren, C. Dekker, Room-temperature transistor based on a single carbon nanotube. Nature 393(7), 49–52 (1998)

K. You, K. Nepal, Design of a ternary static memory cell using carbon nanotube based transistors. Micro & Nano Lett. 6(6), 381–385 (2011)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Hosseini, S.A., Etezadi, S. A Novel Low-Complexity and Energy-Efficient Ternary Full Adder in Nanoelectronics. Circuits Syst Signal Process 40, 1314–1332 (2021). https://doi.org/10.1007/s00034-020-01519-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01519-2