Abstract

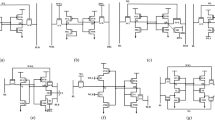

Static random access memory is a key component for most microprocessor-based digital devices. With the declining technology node and reducing supply voltage, it is essential to improve its performance. This paper proposes a seven transistor, single-ended, bit cell configuration. The performance of the cell are evaluated at 300 mV supply voltage. The hold/read noise margins for the proposed bit cell is fairly high at 98 mV each, while the write margin is 154 mV. The reliability of the cell is measured using Monte Carlo process variation and temperature variation analysis. The results obtained for the proposed cell are compared against various pre-existing 5T, 6T, 7T, and 8T cells to showcase the improvements achieved by the proposed 7T cell. The power consumption for the proposed cell is minimal amongst others and requires a pulse width of 13 and 5 ns to perform successful write and read operations, respectively. The above-stated enhancement is achieved for the layout area of 0.65 μm2. While the layout footprint for 5T, 6T1, 6T2, 7T1, 7T2, 7T3, 8T1, 8T2, and 10T cell are 0.66, 0.82, 0.048, 0.74, 0.82, 0.8, 0.84, 1.34, and 1.27 µm2, respectively.

Similar content being viewed by others

Availability of Data and Material

All data generated or analyzed during this study are included in this published article.

References

S. Ahmad, B. Iqbal, N. Alam, M. Hasan, Low leakage fully half-select-free robust SRAM cells with BTI reliability analysis. IEEE Trans. Dev. Mater. Reliab. 18(3), 337–349 (2018)

S. Ahmad, M.K. Gupta, N. Alam, M. Hasan Single-ended Schmitt Trigger based robust low power SRAM cell. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 20(8), 2634–2642 (2016)

R.N. Asli, S. Taghipour, Reliable and high performance asymmetric FinFET SRAM cell using back-gate control. Microelectron Reliab 104, 113545 (2020)

P.F. Butzen, R.P. Ribas, Leakage current in sub-micrometer CMOS gates. Universidade Federal do Rio Grande do Sul (2017) [online]. http://inf.ufrgs.br/logics/docman/book_emicro_butzen.pdf

B.H. Calhoun, A.P. Chandrakasan, Static noise margin variation for subthreshold SRAM in 65-nm CMOS. IEEE J. Solid-State Circuits 41(7), 1673–1679 (2006)

I. Carlson, S. Andersson, S. Natarajan, A. Alvandpour, A high density, low leakage, 5T SRAM for embedded caches, in Proceedings 30th European Solid State Circuits Conference (2004), pp. 215–218

I.J. Chang, J.J. Kim, S. Park, K. Roy, A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. IEEE J. Solid State Circuits 44(2), 650 (2009)

K. Cho, J. Park, T.W. Oh, O.K. Jung, One sided Schmitt–Trigger based 9T SRAM cell for near threshold operation. IEEE Trans. Circuits Syst. I Regul. Pap. 67(5), 1551–1561 (2020)

T. Doorn, E.T. Maten, J. Croon, A.D. Bucchianico, O. Wittich, Importance sampling Monte Carlo simulations for accurate estimation of SRAM yield, in ESSCIRC 2008—34th European solid-state circuits conference (2008)

S.S. Ensan, M.H. Moaiyeri, M. Moghaddam, B. Ebrahimi, S. Hessabi, A.A. Kusha, A low-leakage and high-writable SRAM cell with back-gate biasing in FinFET technology. J. Comput. Electron. 18, 519–526 (2019)

S.S. Ensan, M.H. Moaiyeri, M. Moghaddam, S. Hessabi, A low-power single-ended SRAM in FinFET technology. AEU—International Journal of Electronics and Communications. 99(2), 361–368 (2019)

S.S. Ensan, M.H. Moaiyeri, S. Hessabi, A robust and low-power near-threshold SRAM in 10-nm FinFET technology. Analog Integr. Circ. Sig. Process 94, 497–506 (2018)

N. Eslami, B. Ebrahimi, E. Shakouri, D. Najafi, A single-ended low leakage and low voltage 10T SRAM cell with high yield. Analog Integr. Circ. Sig. Process 105, 263–274 (2020)

R. Faraji, H.R. Naji, M.R. Nezhad, M. Arabnejhad, A new SRAM design using body bias technique for low power and high speed application. Int. J. Circuit Theory Appl. 42(11), 1189–1202 (2014)

Y. He, J. Zhang, X. Wu, S. Zhen, B. Zhang, A half-select disturb—free 11T SRAM cell with built-in write/read-assist scheme for ultralow-voltage operations. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 27(10), 2344–2353 (2019)

R.F. Hobson, A new single-ended SRAM cell with write-assist. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 15(2), 173–181 (2007)

K.O. Jeppson, S. Christensson, N. Hedenstierna, Formal definitions of edge-based gemoetric design rules. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 12(1), 59–69 (1993)

J.P. Kulkarni, K. Roy, Ultralow-voltage process-variation-Tolerant Schmitt-Trigger-based SRAM design. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 20(2), 319–332 (2012)

M. Kumar, J.S. Ubhi, Design and analysis of CNTFET based 10T SRAM for high performance at nanoscale. Int. J. Circuit Theory Appl. 47(11), 1775–1785 (2019)

C.B. Kushwah, S.K. Vishvakarma, D. Dwivedi, Single-ended boost-less (SE-BL) 7T process tolerant SRAM design in sub-threshold regime for ultra-low-power applications. Circuits Syst. Signal Process. 35, 385–407 (2016)

S. Lin, Y.B. Kim, F. Lombardi, A highly-stable nanometer memory for low power design, inProceedings IEEE international workshop design test of nano devices, circuits systems (2008), pp. 17–20

S. Lin, Y.B. Kim, F. Lombardi, Design and analysis of a 32 nm PVT tolerant CMOS SRAM cell for low leakage and high stability. Integration 43(2), 176–187 (2010)

J.S. Liu, M.B. Clavel, M.K. Hudait, An energy-efficient tensile strained Ge/InGaAs FET 7T SRAM cell architecture for ultralow voltage applications. IEEE Trans. Electron Dev. 64(5), 2193–2200 (2017)

N. Mishra, P. Mittal, B. Kumar, Analytical modeling for static and dynamic response of organic pseudo all-p inverter circuits. J. Comput. Electron. 18, 1490–1500 (2019)

M. Moghaddam, M.H. Moaiyeri, M. Eshghi, Ultra low-power 7T SRAM cell design based on CMOS, in 2015 23rd Iranian Conference on Electrical Engineering (2015)

H. Noguchi, S. Okumura, Y. Iguchi, H. Fujiwara, Y. Morita, K. Nii, H. Kawaguchi, M. Yoshimoto, Which is the best dual-port SRAM in 45-nm process technology? 8T, 10T single end, and 10T differential, in Proceedings of ICICDT (2007), pp. 55–58

G. Pasandi, M. Pedram, Internal write-back and read-before-write schemes to eliminate the disturbance to the half-selected cells in SRAMs. IET Circuits Dev. Syst. 12, 460–466 (2018)

S.A. Pourbakhsh, X. Chen, D. Chen, X. Wang, N. Gong, J. Wang, Sizing-priority based low-power embedded memory for mobile video applications, in 2016 17th International Symposium on Quality Electronic Design (ISQED) (IEEE, 2016)

A.P.S. Rathod, P. Lakhera, A.K. Baliga, P. Mittal, B. Kumar, Performance comparison of pass transistor and CMOS logic configuration based de-multiplexer, in International Conference on Computing, Communication and Automation (2015), pp. 1433–1437

G. Rawat, K. Rathore, S. Kala, P. Mittal, Design and analysis of ALU: Vedic mathematics approach, in International Conference on Computing, Communication and Automation (2015), pp. 1372–1376

B. Rawat, P. Mittal, Single bit line accessed high performance ultralow voltage operating 7T SRAM bit cell with improved read stability. Int. J. Circuit Theory Appl. 49(5), 1435–1449 (2021)

C. Roy, A. Islam, Power-aware source feedback single-ended 7T SRAM cell at nanoscale regime. Microsyst. Technol. 25(5), 1783–1791 (2017)

E. Shakouri, B. Ebrahimi, N. Eslami, M. Chahardori, Single-ended 10T SRAM cell with high yield and low standby power. Circuits Syst. Signal Process. 40, 3479–3499 (2021)

V. Sharma, S. Vishvakarma, S.S. Chouhan, K. Halonen, A write improved low power 12T SRAM cell for wearable wireless sensor nodes. Int. J. Circuit Theory Appl. 46(12), 2314–2333 (2018)

A. Sil, S. Ghosh, M.A. Bayoumi, A novel 90 nm 8T SRAM cell with enhanced stability, in IEEE International Conference on Integration Circuit Design Technology (2007)

P. Singh, S.K. Vishvakarma, Ultra-low power high stability 8T SRAM for application in object tracking system. IEEE Access. 6, 2279–2290 (2017)

J. Singh, S.P. Mohanty, D.K. Pradhan, Robust SRAM designs, and analysis (Springer, New York, 2013)

N. Surana, J. Mekie, Energy efficient single-ended 6-T SRAM for multimedia applications. IEEE Trans. Circuits Syst. II Express Br. 66(6), 1023–1027 (2019)

S.O. Toh, Z. Guo, T.J.K. Liu, B. Nikolic, Characterization of dynamic SRAM stability in 45nm CMOS. IEEE J. Solid-State Circuits 46(11), 2702–2712 (2011)

L. Wen, X. Cheng, K. Zhou, S. Tian, X. Zeng, Bit-interleaving-enabled 8T SRAM with shared data-aware-write and reference-based sense amplifier. IEEE Trans. Circuits Syst. II Express Briefs 63(7), 643–647 (2016)

N. Yoshnobu, H. Masahi, K. Takayuki, K. Itoh, Review and future prospects of low-voltage RAM circuits. IBM J. Res. Dev. 47(5/6), 525–552 (2003)

B. Yang, L. Kim, A low-power SRAM using hierarchical bit line and local sense amplifiers. IEEE J. Solid State Circuit 40(6), 1366–1376 (2005)

H.I. Yang, M.H. Chang, S.Y. Lai, H.F. Wang, W. Hwang, A low-power low-swing single-ended multi-port SRAM, in Proceedings of VLSIDAT (2007), pp. 28–31

Author information

Authors and Affiliations

Contributions

Both the authors have an equal contribution for idea realization and implementation, finding the results, outcomes analysis, curves plotting, paper writing, paper revising, proofreading, replying to reviewer comments, etc.

Corresponding author

Ethics declarations

Conflicts of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rawat, B., Mittal, P. A Reliable and Temperature Variation Tolerant 7T SRAM Cell with Single Bitline Configuration for Low Voltage Application. Circuits Syst Signal Process 41, 2779–2801 (2022). https://doi.org/10.1007/s00034-021-01912-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01912-5