Abstract

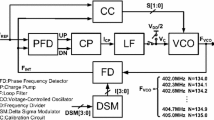

This study develops a multiphase voltage-controlled oscillator (VCO) by using the subfeedback loop technique. The proposed N-stage ring oscillator with k-stage subfeedback loops (where N is not a multiple of k) has N output phases, and its operating frequency is as high as that of the k-stage subfeedback loops. Circuit analysis and simulation processes for design optimization are presented herein. The first-order linear inverter model of the proposed ring oscillator defines the relationship between its operating frequency and phase number. In the topology of the proposed oscillator, the operating frequency does not decrease as the number of stages of the ring oscillator increases. The proposed multiphase VCO is verified in a 5-GHz 12-phase phase-locked loop. The test chip is implemented in a 0.18-μm complementary metal–oxide–semiconductor process, and its core area is determined to be 260 × 355 μm2. The root mean square jitter and peak-to-peak jitter are 1.03 and 8.85 ps, respectively. The phase noise of the output signal is − 91.44 dBc/Hz at 1-MHz.

Similar content being viewed by others

References

M.M. Abdul-Latif, E. Sanchez-Sinencio, Low phase noise wide tuning range N-push cyclic-coupled ring oscillators. IEEE J. Solid-State Circuits 47(6), 1278–1294 (2012)

D. Biswas, Spur reduction circuit for fractional-N PLLs. Circuits Syst. Signal Process 41(5), 2466–2485 (2022)

I.S. Bristy, M.N. Uddin, Optimization and performance analysis of 32 channel 60 Gbps hybrid mono stage MZM based WDM PON covering 120 km transmission distance, in IEEE International Conference on Robotics, Electrical and Signal Processing Techniques (2021), pp. 635–639

H. Ghasemian, A. Bahrami, E. Abiri, M.R. Salehi, A new low-power charge pump with a glitch-free PFD for speedup the acquisition process of a PLL in 65 nm CMOS technology. Circuits Syst. Signal Process 40(6), 2982–3006 (2021)

A.A. Hafez, C.-K. Yang, Design and optimization of multipath ring oscillators. IEEE Trans. Circuits Syst. I Reg. Pap. 58(10), 2332–2345 (2011)

H.-Y. Huang, F.-C. Tsai, Analysis and optimization of ring oscillator using sub-feedback scheme, in Proceedings of IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems (2009), pp. 28–29

I.U. Khan, D. Balodi, N.K. Misra, Low power LC-quadrature VCO with superior phase noise performance in 0.13 µm RF-CMOS process for modern WLAN application. Circuits Syst. Signal Process 41(5), 2522–2540 (2022)

B. Kim, D.N. Helman, P.R. Gray, A 30-MHz hybrid analog/digital clock recovery circuit in 2-μm CMOS. IEEE J. Solid-State Circuits 25(6), 1385–1394 (1990)

J. Kim, M.A. Horowitz, Adaptive supply serial links with sub-1-V operation and per-pin clock recovery. IEEE J. Solid-State Circuits 37(11), 1403–1413 (2002)

K.-H. Kim, H.-J. Chung, W.-S. Kim, M. Park, Y.-C. Jang, J.-Y. Kim, H.-W. Park, U. Kang, P.W. Coteus, J.-S. Choi, C.-H. Kim, An 8 Gb/s/pin 9.6 ns row-cycle 288 Mb deca-data rate SDRAM with an I/O error detection scheme. IEEE J. Solid-State Circuits 42(1), 193 (2007)

Y. Konno, K. Tomioka, Y. Aiba, K. Yamazoe, B.-S. Song, A CMOS 1×- to 16×-speed DVD write channel IC, in IEEE International Solid-State Circuits Conference: Digest of Technical Papers (2005), pp. 568–569

M.-A. LaCroix, H. Wong, Y.H. Liu, H. Ho, S. Lebedev, P. Krotnev, D.A. Nicolescu, D. Petrov, C. Carvalho, S. Alie, E. Chong, F.A. Musa, D. Tonietto, A 60Gb/s PAM-4 ADC-DSP transceiver in 7 nm CMOS with SNR-based adaptive power scaling achieving 6.9pJ/b at 32dB loss, in IEEE IEEE International Solid-State Circuits Conference: Digest of Technical Papers (2019), pp. 114–116

S.-J. Lee, B. Kim, K. Lee, A novel high-speed ring oscillator for multiphase clock generation using negative skewed delay scheme. IEEE J. Solid-State Circuits 32(2), 289–291 (1997)

J.-C. Liu, Y.-P. Li, A low supply voltage all-digital phase-locked loop with a bootstrapped and forward interpolation digitally controlled oscillator. IEEE Access 9(3), 39717–39726 (2021)

Y.-L. Lo, W.-H. Ho, A low-voltage PLL design using a new calibration technique for low-power implantable biomedical systems. Circuits Syst. Signal Process 36(12), 4809–4828 (2017)

J.G. Maneatis, M.A. Horowitz, Precise delay generation using coupled oscillators. IEEE J. Solid-State Circuits 28(12), 1273–1282 (1993)

A. Matsumoto, S. Sakiyama, Y. Tokunaga, T. Morie, S. Dosho, A design method and developments of a low-power and high-resolution multiphase generation system. IEEE J. Solid-State Circuits 43(4), 831–843 (2008)

J.F. Parker, D. Ray, A 1.6-GHz CMOS PLL with on-chip loop filter. IEEE J. Solid-State Circuits 33(3), 337–343 (1998)

A. Rofourgan, J. Rael, M. Rofourgan, A. Abidi, A 900 MHz CMOS LC-oscillator with quadrature outputs, in IEEE International Solid-State Circuits Conference: Digest of Technical Papers (1996), pp. 392–393

S. Salem, M. Saneei, D. Abbasi-Moghadam, Jitter modeling in digital CDR with quantization noise analysis. Circuits Syst. Signal Process 40(8), 3884–3906 (2021)

L. Sun, T.A. Kwasniewski, A 1.25-GHz 0.35-um monolithic CMOS PLL based on a multiphase ring oscillator. IEEE J. Solid-State Circuits 36(6), 910–916 (2001)

L. Sun, T. Kwasniewski, K. Iniewski, A quadrature output voltage-controlled ring oscillator based on three-stage sub-feedback loops, in Proceedings of IEEE International Symposium on Circuits and Systems (1999), pp. 176–179

Y.-H. Tu, J.-C. Liu, K.-H. Cheng, C.-Y. Chang, Low supply voltage and multiphase all-digital crystal-less clock generator. IEE Circuits Devices Syst. 12(6), 720–725 (2018)

Acknowledgements

The authors would like to thank the Ministry of Science and Technology (MOST) and Taiwan Semiconductor Research Institute (TSRI) for the supporting of EDA tools and fabrication of the test chip. The authors also would like to thank Prof. Kuo-Hsing Cheng of National Central University, Taiwan, for the support of the test equipment.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Huang, HY., Liu, JC., Tsai, FC. et al. A 12-Phase and 5-GHz PLL with a Subfeedback Loop Technique. Circuits Syst Signal Process 42, 1873–1892 (2023). https://doi.org/10.1007/s00034-022-02205-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02205-1