Abstract

In this paper, both grounded and floating type novel designs of inductance simulator, capacitance multiplier simulator and frequency-dependent negative conductance (FDNC) simulator are proposed. Current follower differential input transconductance amplifier (CFDITA) is utilized as active building block in the realization of the proposed works. All the proposed ideas employ grounded capacitor(s) as only passive element(s) which make these designs suitable to modern integration technology. The proposed designs are electronically tunable as transconductance of CFDITA can be varied with bias current. Additionally, the proposed designs have no matching constraints. PSPICE with 0.18 µm CMOS technology process parameters is used to perform simulations of the proposed designs. Experimental verification of functionality of the proposed grounded inductance simulator is also done using commercially available ICs, AD844 and LM13700. The applications of the proposed floating inductance simulator as band-pass filter and band-reject filter are explored. Additionally, proposed grounded FDNC simulator is also tested in third-order high-pass filter to demonstrate the applicability aspects.

Similar content being viewed by others

Data Availability

Data sharing is not applicable to this article as no datasets were generated or analysed during the current study.

References

E. Alaybeyoglu, Implementation of capacitor multiplier with cell-based variable transconductance amplifier. IET Circuits Devices Syst. 13(3), 267–272 (2018)

E. Alaybeyoglu, H. Kuntman, Capacitor multiplier with high multiplication factor for integrated low pass filter of biomedical applications using DTMOS technique. AEU Int. J. Electron. Commun. 107, 291–297 (2019)

K. Bhardwaj, M. Srivastava, New FDNR and FDNC simulation configurations using inverted VDDIBAs. Adv VLSI Commun Signal Process Springer Singap. 583–594 (2021)

K. Bhardwaj, M. Srivastava, Novel CDDITA-based-grounded inductance simulation circuits, advances in VLSI. Communication, and signal processing, lecture notes in electrical engineering. (Springer, Singapore, 2021)

D.R. Bhaskar, G. Mann, P. Kumar, OTRA-based positive/negative grounded capacitance multiplier. Analog Integr. Circ. Sig. Process. 111, 469–481 (2022)

D. Biolek, J. Vavra, A. Keskin, CDTA-based capacitance multipliers. Circuits Syst. Signal Process. 38, 1466–1481 (2019)

B. Chaturvedi, A. Kumar, Novel CMOS MO-CFDITA based fully electronically controlled square/triangular wave generator with adjustable duty cycle. IET Circuits Devices Syst. 12(6), 817–826 (2018)

B. Chaturvedi, A. Kumar, Electronically tunable current-mode instrumentation amplifier with high CMRR and wide bandwidth. AEU-Int. J. Electron. Commun. 92, 116–123 (2018)

M. Dogan, E. Yuce, CFOA based a new grounded inductor simulator and its applications. Microelectron. J. 90, 297–305 (2019)

M. Dogan, E. Yuce, A new CFOA based grounded capacitance multiplier. AEU Int. J. Electron. Commun. 115, 153034 (2020)

M. Faseehuddin, J. Sampe, S. Shireen, S.H. Ali, Lossy and lossless inductance simulators and universal filters employing a new versatile active block. Informacije MIDEM 48(2), 97–114 (2018)

W. Jaikla, S. Bunrueangsak, F. Khateb, T. Kulej, P. Suwanjan, P. Supavarasuwat, Inductance simulators and their application to the 4th order elliptic lowpass ladder filter using CMOS VD-DIBAs. Electronics 10(6), 684 (2021)

W. Jaikla, R. Sotner, F. Khateb, Design and analysis of floating inductance simulators using VDDDAs and their applications. AEU Int. J. Electron. Commun. 112, 152937 (2019)

M. Konal, F. Kacar, Grounded inductance simulator realization with single VDDDA. Analog Integr. Circ. Sig. Process 110(2), 279–288 (2022)

A. Kumar, B. Chaturvedi, Novel CMOS CFDITA and its application as electronically-tunable bistable multivibrator. Int. Conf. Signal Process. Commun. (ICSC). 374–379 (2016)

U. Kumar, S.K. Shukla, Analytical study of inductor simulation circuits. Act. Passive Electron. Compon. 13(4), 211–227 (1989)

E. Ozer, M.E. Basak, F. Kacar, Realizations of lossy and lossless capacitance multiplier using CFOAs. AEU Int. J. Electron. Commun. 127, 153444 (2020)

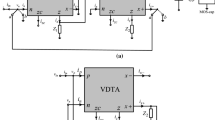

P.V. Petrović, New floating/grounded FDNC and non-ideal grounded FDNR simulators based on VDTA. Analog Integr. Circ. Sig. Process 110(2), 259–277 (2022)

A. Sedra, K.C. Smith, A second-generation current conveyor and its applications. IEEE Trans. Circuit Theory. 17(1), 132–134 (1970)

A. Singh, M.K. Jain, S. Wairya, Novel lossless grounded and floating inductance simulators employing a grounded capacitor based on CC-CFA. J. Circuits Syst. Comput. 28(6), 1950093 (2019)

A.K. Singh, P. Kumar, R. Senani, Electronically tunable grounded/floating inductance simulators using Z-copy CFCCC. Turk. J. Electr. Eng. Comput. Sci. 26(2), 1041–1055 (2018)

D. Singh, D. Nand, A. Kumar, Newly realized grounded capacitance multiplier using single CFDITA. 7th International Conference on Signal Processing and Communication (ICSC). (2021) pp. 362–365.

S. Singh, N. Pandey, R. Pandey, CFOA based negative floating capacitance multiplier. Adv. Electron. Eng Springer Singap (2020). https://doi.org/10.1007/978-981-15-1289-6_22

S. Siripongdee, W. Jaikla, Electronically controllable grounded inductance simulators using single commercially available IC: LT1228. AEU Int. J. Electron. Commun. 76, 1–10 (2017)

K.C. Smith, A. Sedra, The current conveyor-A new circuit building block. Proc. IEEE 56(8), 1368–1369 (1968)

M. Srivastava, K. Bhardwaj, Compact lossy inductance simulators with electronic control. Iran. J. Electr. Electron. Eng. 15(3), 343–351 (2019)

V. Stornelli, L. Safari, G. Barile, G. Ferri, A new extremely low power temperature insensitive electronically tunable VCII-based grounded capacitance multiplier. IEEE Trans. Circuits Syst. II Express Briefs 68(1), 72–76 (2020)

V. Stornelli, L. Safari, G. Barile, G. Ferri, A new VCII based grounded positive/negative capacitance multiplier. AEU Int. J. Electron. Commun. 137, 153793 (2021)

W. Tangsrirat, Synthetic grounded lossy inductance simulators using single VDIBA. IETE J. Res. 63(1), 134–141 (2017)

W. Tangsrirat, Actively floating lossy inductance simulators using voltage differencing buffered amplifiers. IETE J. Res. 65(4), 446–459 (2019)

M. Tangsrirat, O. Channumsin, Tunable floating capacitance multiplier using single fully balanced voltage differencing buffered amplifier. J. Commun. Technol. Electron. 64(8), 797–803 (2019)

S. Theingjit, T. Pukkalanun, W. Tangsrirat, Grounded FDNC and FDNR realizations based on Gm-C technique and their applications to ladder filter design. Eng. Lett. 24, 263–267 (2016)

J. Vavra, Floating capacitance multiplier based on DVCC. 41st International Conference on Telecommunications and Signal Processing (TSP). (2018) pp. 1–4

R. Verma, N. Pandey, R. Pandey, Novel CFOA based capacitance multiplier and its application. AEU Int. J. Electron. Commun. 107, 192–198 (2019)

A. Yesil, E. Yuce, S. Minaei, Grounded capacitance multipliers based on active elements. AEU Int. J. Electron. Commun. 79, 243–249 (2017)

E. Yuan, CMOS active inductors and transformers principle, implementation, and applications (Springer Science & Business Media, New York, 2008)

E. Yuce, H. Alpaslan, New CMOS based current follower and its applications to inductor simulator and band-pass filter. Indian J. Pure Appl. Phys. (IJPAP). 54(8), 511–516 (2016)

E. Yuce, S. Minaei, Commercially available active device based grounded inductor simulator and universal filter with improved low frequency performances. J. Circuits Syst. Comput. 26(04), 1750052 (2017)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kumar, A., Chaturvedi, B. & Jagga, S. New CMOS Compatible Realizations of Grounded/Floating L, C Multiplier and FDNC Simulators. Circuits Syst Signal Process 42, 1911–1939 (2023). https://doi.org/10.1007/s00034-022-02207-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02207-z