Abstract

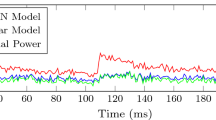

The RTOS (Real-Time Operating System) is a critical component in the SoC (System-on-a-Chip), which is the main body for consuming total system energy. Power optimization based on hardware–software partitioning of a RTOS (RTOS–Power partitioning) can significantly minimize the energy consumption of a SoC. This paper presents a new model for RTOS–Power partitioning, which helps in understanding the essence of the RTOS–Power partitioning techniques. A discrete Hopfield neural network approach for implementing the RTOS–Power partitioning is proposed, where a novel energy function, operating equation and coefficients of the neural network are redefined. Simulations are carried out with comparison to other optimization techniques. Experimental results demonstrate that the proposed method can achieve higher energy savings up to 60% at relatively low costs of less than 4k PLBs while increasing the performance compared to the purely software realized SoC–RTOS.

Similar content being viewed by others

References

Jerraya AA, Yoo S, Verest D, When, N (eds) (2003) Embedded software for SoC. Kluwer, Netherlands, ISBN 1-4020-7528-6, pp 3–11

Dick RP (2002) Multi-objective synthesis of low-power real-time distributed embedded systems. Ph.D dissertation, Department of Electrical Engineering, Princeton University, pp 11–21

Li T, John LK (2003) Run-time modeling and estimation of operating system energy consumption. In: Proceedings of the SIGMETRICS’03, San Diego, pp 160–171

Tan TK, Raghunathan A, Jha NK (2005) Energy macromodeling of embedded operating systems. ACM Trans Embed Comput Syst (TECS) 4(1):231–254

Gupta RK, De Micheli G (1993) Hardware–software co-synthesis for digital systems. IEEE Design Test Comput 10(3):29–41

Eles P, Peng Z, Kuchcinski K, Doboli A (1997) System level hardware/software partitioning based on simulated annealing and Tabu search. Design Autom Embed Syst 2(1):5–32

Saha D, Mitra RS, Basu A (1998) Hardware/software partitioning using genetic algorithm. In: Proceedings of the International Conference on VLSI design, Hyderabad, pp 155–159

Filho FC, Maciel P, Barros E (2001) A petri nets based approach for hardware/software partitioning. Integr Circuits Syst Design 8(6):72–77

Xiong ZH, Li SK, Chen JH (2005) Hardware/software partitioning based on dynamic combination of genetic algorithm and ant algorithm. J Softw 16(4):503–512

Arató P, Juhász S, Mann ZÁ, Papp D (2003) Hardware–software partitioning in embedded system design. In: Proceedings of the IEEE international symposium on intelligent signal processing, Budapest, pp 63–69

Stitt G, Lysecky R, Vahid F (2003) Dynamic hardware/software partitioning: a first approach. In: Design automation conference (DAC), Anaheim, pp 74–81

Guo B, Wang DH, Shen Y, Li ZS, Liu Z (2006) Hardware–software partitioning of real-time operating systems using Hopfield neural networks. NeuroComputing (2006) (in press)

Henkel J (2002) A low power hardware/software partitioning approach for core-based embedded systems. In: Design automation conference (DAC), New Orleans, pp 122–127

Tamaki Y, Funabiki N, Nishikawa S (1999) A binary neural network algorithm for the graph partitioning problem. Electron Commun Jpn Pt 3 82(12):34–42

Pereira C, Raghunathan V, Gupta S, Gupta R, Srivastava M (2002) A software architecture power aware real time operating systems. CECS Technical Report 02-02, University of California, Irvine

He ZT, Mok A, Peng C (2005) Timed RTOS modeling for embedded system design. In: Proceedings of the IEEE real-time and embedded technology and applications symposium (RTAS’05), San Francisco, pp 54–63

Acknowledgments

The authors thank the anonymous reviewers for their constructive comments, which helped us in improving the quality of this paper. The first author acknowledges the financial support from the National Natural Science Foundation of China under Grant no. 60572026.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Guo, B., Wang, D.H., Shen, Y. et al. A Hopfield neural network approach for power optimization of real-time operating systems. Neural Comput & Applic 17, 11–17 (2008). https://doi.org/10.1007/s00521-006-0074-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00521-006-0074-6