Abstract

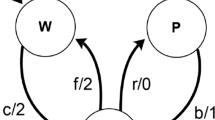

The task of finding a set of test sequences that provides good coverage of industrial circuits is infeasible because of the size of the circuits. For small critical subcircuits of the design, however, designers can create a set of test sequences that achieve good coverage. These sequences cannot be used on the full design because the inputs to the subcircuit may not be accessible. In this work we present an efficient test generation algorithm that receives a test sequence created for the subcircuit and finds a test sequence for the full design that reproduces the given sequence on the subcircuit. The algorithm uses a new technique called dynamic transition relations to increase its efficiency .

The most common and most expensive step in our algorithm is the computation of the set of predecessors of a set of states. To make this computation more efficient we exploit a partitioning of the transition relation into a set of simpler relations. At every step we use only those that are necessary, resulting in a smaller relation than the original one. A different relation is used for each step, hence the name dynamic transition relations. The same idea can be used to improve symbolic model checking for the temporal logic CTL.

We have implemented the new method in SMV and run it on several large circuits. Our experiments indicate that the new method can provide gains of up to two orders of magnitude in time and space during verification. These results show that dynamic transition relations can make it possible to verify circuits that were previously unmanageable due to their size and complexity .

Similar content being viewed by others

References

Beenker F, Dekker R, Stans R, van der Star M (1989) A testability strategy for silicon computers. In: Proceedings of the international test conference, Washington, DC, August 1989, pp 660–669

Boppana V, Rajan S, Takayama K, Fujita M (1999) Model checking based on sequential ATPG. In: Proceedings of the conference on computer aided verification, Trento, Italy, July 1999, pp 418–430

Bryant RE (1986) Graph-based algorithms for boolean function manipulation. IEEE Trans Comput C-35(8):677–691

Burch JR, Clarke EM, McMillan KL, Dill DL, Hwang LJ (1992) Symbolic model checking: 1020 states and beyond. Inf Comput 98(2):142–170

Campos S, Clarke E, Grumberg O (2000) Selective quantitative analysis and interval model checking: verifying different facets of a system. Formal Meth Sys Des 17:163–192

Campos S, Clarke E, Marrero W, Minea M (1995) Verifying the performance of the PCI local bus using symbolic techniques. In: Proceedings of the international conference on computer design, Austin, TX, October 1995, pp 72–78

Chakrabarty K, Murray B, Iyengar V (1999) Built-in test pattern generation for high-performance circuits using twisted-ring counters. In: Proceedings of the IEEE VLSI Test symposium, San Diego, 22–27 April 1999

Clarke E, Grumberg O, Peled D (2000) Model checking. MIT Press, Cambridge, MA

Clarke EM, Emerson EA, Sistla AP (1986) Automatic verification of finite-state concurrent systems using temporal logic specifications. ACM Trans Programm Lang Sys 8(2):244–263

Coudert O, Madre JC, Berthet C (1990) Verifying temporal properties of sequential machines without building their state diagrams. In: Proceedings of the conference on computer aided verification, Grenoble, France, pp 365–373

Engels A, Feijs L, Mauw S (1997) Test generation for intelligent networks using model checking. In: Proceedings of the 3rd conference on tools and algorithms for the construction and analysis of systems (TACAS), Enschede, The Netherlands, April 1997, pp 384–398

Fernandez JC, Jard C, Jeron T, Viho C (1996) Using on-the-fly verification techniques for the generation of test suites. In: Proceedings of the conference on computer aided verification, New Brunswick, NJ, August 1996

Goga N (2000) An optimization of the TorX test generation algorithm. Xootic Mag November 2000, pp 15–21

Lee J, Patel JH (1991) An architectural level test generator for a hierarchical design environment. In: Proceedings of the 21st symposium on fault-tolerant computing, Nashville, TN, October 1991, pp 729–738

Lee J, Patel JH (1993) An architectural level test generator for a hierarchical design environment based on nonlinear equation solving. J Electron Test

McMillan KL (1993) Symbolic model checking. Kluwer, Dordrecht

Murray B (1994) Hierarchical testing using precomputed tests for modules. PhD thesis, Department of Computer Science and Engineering, University of Michigan, Ann Arbor, MI

Petrenko A, Yevtushenko N, Bochmann G (1996) Testing deterministic implementations from nondeterministic FSM specifications. In: Proceedings of the 9th international workshop on protocol test systems, Darmstadt, Germany, pp 125–140

Tretmans J, Belinfante A (1999) Automatic testing with formal methods. In: Proceedings of EuroSTAR’99: 7th European international conference on software testing, analysis and review, Barcelona, Spain, November 1999

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Campos, S., Grumberg, O., Yorav, K. et al. Test sequence generation and model checking using dynamic transition relations. Int J Softw Tools Technol Transfer 6, 174–182 (2004). https://doi.org/10.1007/s10009-004-0142-0

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10009-004-0142-0