Abstract

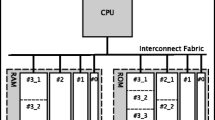

To increase memory bandwidth, many programmable Digital Signal Processors (DSPs) employ two on-chip data memories. This architectural feature supports higher memory bandwidth by allowing multiple data memory accesses to occur in parallel. Exploiting dual memory banks, however, is a challenging problem for compilers. This, in part, is due to the instruction-level parallelism, small numbers of registers, and highly specialized register capabilities of most DSPs. In this paper, we present a new methodology based on a genetic algorithm for assigning data to dual-bank memories. Our approach is global, and integrates several important issues in memory assignment within a single model. Special effort is made to identify those data objects that could potentially benefit from an assignment to a specific memory, or perhaps duplication in both memories. As part of our experimentation, we compare the effectiveness of three different repair heuristics which consist in transforming infeasible solutions into feasible ones. Our computational results show that when using the most effective repair method, the GA is able to achieve a 54% reduction in the number of memory cycles and a reduction in the range of 7 to 42% in the total number of cycles when tested with well-known DSP kernels and applications.

Similar content being viewed by others

References

Cho J, Paek Y, Whalley W (2002) Efficient register and memory assignment for non-orthogonal architectures via graph coloring and MST algorithms. In: Proceedings of the international conference on LCTES and SCOPES, Berlin, Germany

Garey M, Johnson D (1979) Computers and intractability. A guide to the theory of NP-completeness, W.H. Freeman and Company, New York

Benchmark Programs, DSP56000/DSP56001 Digital Signal Processor User’s Manual, Motorola INC., Semiconductor Products Sector, DSP Division, Austin Texas

Orvosh D, Davis L (1993) Shall we repair? Genetic algorithms, combinatorial optimization, and feasibility constraints. In: Proceedings of the fifth internatinal conference on genetic algorithms, Morgan Kaufmann, San Mateo, CA, p 650

Saghir M, Chow P, Lee C (1996) Exploiting dual data-memory banks in digital signal processors. In: Proceedings of the 7th international conference on architectural support for programming languages and operating systems, vol 30, no 5, pp 234–243

Saghir M, Chow P, Lee C (1995) Automatic data partitioning for HLL DSP compilers. In: Proceedings of the 7th international conference on signal processing applications and technology, pp I-658–664

Sudarsanum A, Malik S (1997) Memory bank and register allocation in software synthesis for ASIPs. In: International conference on computer-aided design, pp 388–392

Sudarsanam A, Malik S, Simultaneous reference allocation in code generation for dual data memory bank ASIPs. J ACM Trans Autom Electron Syst (TOADES) 5:242–264

Zhuge Q, Xiao B, Sha E (2002) Variable partitioning and scheduling of multiple memory architectures for DSP. In: Proceedings of the IEEE international parallel and distributed processing symposium (IPDPS)

Zivojnovic V, Velarde J, Schaeger C, Meyr H (1994) DSPstone—A DSP oriented benchmarking methodology. In: Proceedings of the 6th international conference on signal processing applications and technology

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

GréWal, G., Coros, S., Banerji, D. et al. Assigning data to dual memory banks in DSPs with a genetic algorithm using a repair heuristic. Appl Intell 26, 53–67 (2007). https://doi.org/10.1007/s10489-006-0005-3

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10489-006-0005-3