Abstract

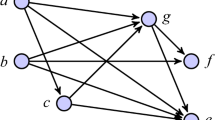

A recent advancement in VLSI that drastically improved the circuit density is the introduction of CMOL (CMOS/nanodevices hybrid), which consists of an overlay of a nanofabric over a CMOS stack. Combinational logic in CMOL is implemented from a netlist of NOR gates and Inverters by programming nanodevices placed between overlapping nanowires. The length of the nanowires is restricted, and therefore connectivity of the circuit elements is constrained to be within a certain radius, else additional buffers are required.

In this paper we present a Tabu Search (TS) algorithm to address the assignment problem in CMOL. The heuristic is engineered to provide sub-optimal solution by efficient exploration of search space. Empirical results for ISCAS benchmarks are compared with previous solutions using GA, MA, and LRMA heuristics. Results show that in almost all cases, TS exhibits more intelligent search of the solutions subspace, and is able to find better solutions in less time. For all tested benchmarks, over 90 % reduction in average CPU processing time when compared with best published techniques was obtained.

Similar content being viewed by others

References

Abid Z, Alma’aitah A, Barua M, Wang W (2009) Efficient CMOL gate designs for cryptography applications. IEEE Trans Nanotechnol 8(3):315–321

Abid Z, Liu M, Wang W (2011) 3D integration of CMOL structures for FPGA applications. IEEE Trans Comput 60(4):463–471

Brglez F, Bryan D, Kozminski K (1989) Combinational profiles of sequential benchmark circuits. In: IEEE international symposium on circuits and systems, 1989, vol 3, pp 1929–1934

Butts M, DeHon A (2002) Molecular electronics: devices, systems and tools for gigagate, gigabit chips. In: ICCAD-2002, pp 433–440

Chen G, Song X, Hu P (2009) A theoretical investigation on CMOL FPGA cell assignment problem. IEEE Trans Nanotechnol 8(3):322–329

Chu Z, Xia Y, Hung WN, Wang L, Song X (2010) A memetic approach for nanoscale hybrid circuit cell mapping. In: 2010 13th euromicro conference on digital system design: architectures, methods and tools (DSD), pp 681–688

Cortes P, Muñuzuri J, Onieva L, Fernández J (2011) A tabu search algorithm for dynamic routing in ATM cell-switching networks. Appl Soft Comput 11(1):449–459

Dong C, Wang W, Haruehanroengra S (2006) Efficient logic architectures for CMOL nanoelectronic circuits. Micro Nano Lett 1(2):74–78

Garbolino T, Papa G (2010) Genetic algorithm for test pattern generator design. Appl Intell 32(2, SI):193–204

Glover F, Laguna M (1997) Tabu search. Kluwer Academic, Norwell

Hamidipour H, Keshavarzi P, Naderi A (2010) Routing congestion removing of CMOL FPGA circuits by a recursive method. In: Proceedings of the 9th WSEAS international conference on microelectronics, nanoelectronics, optoelectronics, MINO’10. World Scientific and Engineering Academy and Society (WSEAS), Stevens Point, pp 75–79

Hedar AR, Ali A (2012) Tabu search with multi-level neighborhood structures for high dimensional problems. Appl Intell 37:189–206. doi:10.1007/s10489-011-0321-0

Hung WN, Gao C, Song X, Hammerstrom D (2008) Defect-tolerant CMOL cell assignment via satisfiability. IEEE Sens J 8(6):823–830

Khan SA, Engelbrecht AP (2012) A fuzzy particle swarm optimization algorithm for computer communication network topology design. Appl Intell 36(1):161–177

Korkmaz EE (2010) Multi-objective genetic algorithms for grouping problems. Appl Intell 33(2):179–192

Lee CY, Lee ZJ, Lin SW, Ying KC (2010) An enhanced ant colony optimization (EACO) applied to capacitated vehicle routing problem. Appl Intell 32(1):88–95

Likharev KK (2011) Crossnets: neuromorphic hybrid CMOS/nanoelectronic networks. Sci Adv Mater 3:322–332

McKendall AR Jr, Jaramillo J (2006) A tabu search heuristic for the dynamic space allocation problem. Comput Oper Res 33(3):768–789

Minhas MR, Sait SM (2005) A parallel tabu search algorithm for optimizing multiobjective VLSI placement. In: ICCSA (4). Lecture notes in computer science, vol 3483. Springer, Berlin, pp 587–595

Ozyer T, Zhang M, Alhajj R (2011) Integrating multi-objective genetic algorithm based clustering and data partitioning for skyline computation. Appl Intell 35(1):110–122

Sait SM, Khan JA (2003) Simulated evolution for timing and low power VLSI standard cell placement. Eng Appl Artif Intell 16(5–6):407–423

Sait SM, Youssef H (1995) VLSI physical design automation: theory and practice. McGraw-Hill, New York

Sait SM, Youssef H (1999) Iterative computer algorithms with applications in engineering: solving combinatorial optimization problems. IEEE Comput Soc, Los Alamitos

Shahookar K, Mazumder P (1991) VLSI cell placement techniques. ACM Comput Surv 2(23):143–220

Snider GS, Williams SR (2007) Nano/CMOS architectures using a field-programmable nanowire interconnect. Nanotechnology 18(3):035204

Strukov DB, Likharev KK (2005) CMOL FPGA: a reconfigurable architecture for hybrid digital circuits with two-terminal nanodevices. Nanotechnology 16(6):888–900

Strukov DB, Likharev KK (2005) Prospects for terabit-scale nanoelectronic memories. Nanotechnology 16(1):137

Strukov DB, Likharev KK (2006) CMOL FPGA circuits. In: Proc of int conf on computer design, CDES’2006, pp 213–219

Strukov DB, Likharev KK (2006) A reconfigurable architecture for hybrid CMOS/nanodevice circuits. In: Proceedings of the 2006 ACM/SIGDA 14th international symposium on field programmable gate arrays, FPGA’06. ACM, New York, pp 131–140

Wang K, Zheng YJ (2012) A new particle swarm optimization algorithm for fuzzy optimization of armored vehicle scheme design. Appl Intell 37(4):520–526

Wu J, Abbas-Turki A, El Moudni A (2012) Cooperative driving: an ant colony system for autonomous intersection management. Appl Intell 37(2):207–222

Xia Y, Chu Z, Hung WN, Wang L, Song X (2010) CMOL cell assignment by genetic algorithm. In: 2010 8th IEEE international NEWCAS conference (NEWCAS), pp 25–28

Xia Y, Chu Z, Hung W, Wang L, Song X (2011) An integrated optimization approach for nano-hybrid circuit cell mapping. IEEE Trans Nanotechnol 10(6):1275–1284

Zhang C, Li P, Guan Z, Rao Y (2007) A tabu search algorithm with a new neighborhood structure for the job shop scheduling problem. Comput Oper Res 34(11):3229–3242

Acknowledgements

The authors acknowledge King Fahd University of Petroleum & Minerals for its support, and Dr. William N.N. Hung and Mr. Zhufei Chu for providing ISCAS’89 benchmark files. The authors would like also to thank Dr. Rajat Subhra Chakraborty for his help and support. Thanks are also due to the reviewers of the manuscript whose comments helped in improving our solutions.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sait, S.M., Arafeh, A.M. Cell assignment in hybrid CMOS/nanodevices architecture using Tabu Search. Appl Intell 40, 1–12 (2014). https://doi.org/10.1007/s10489-013-0441-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10489-013-0441-9