Abstract

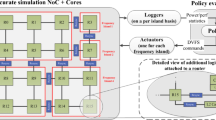

The voltage/frequency island (VFI) design paradigm is a practical architecture for energy-efficient networks-on-chip (NoC) systems. In VFI-based NoC systems, each island can be operated with different voltage and clock frequency and thus it is important to carefully partition processing elements (PEs) into islands based on their workloads and communications. In this paper, we propose an energy-efficient design scheme that optimizes energy consumption and hardware costs in VFI-based NoC systems. Since on-chip networks take up a substantial portion of system power budget in NoC-based systems, the proposed scheme uses communication-aware VFI partitioning and tile mapping/routing algorithms to minimize the inter-VFI communications. Experimental results show that the proposed design technique can reduce communication energy consumption by 32–51% over existing techniques and total energy consumption by 3–14%.

Similar content being viewed by others

References

Benini L, Micheli GD (2002) Networks on chip: a new SoC paradigm. IEEE Comput 35(1):70–78

Dally WJ, Towles B (2001) Route packets, not wires: on-chip interconnection networks. In: Proc design automation conference, pp 684–689

Chapiro DM (1984) Globally asynchronous locally synchronous systems. PhD dissertation, Dept Comput Sci, Stanford Univ, Stanford, CA

Hemani A, Meincke T, Kumar S, Postula A, Olsson T, Nilsson P, Oberg J, Ellervee P, Lundqvist D (1999) Lowering power consumption in clock by using globally asynchronous locally synchronous design style. In: DAC ’99: proceedings of the 36th annual ACM/IEEE design automation conference, pp 873–878

Chelcea T, Nowick SM (2000) A low-latency fifo for mixed-clock systems. In: Proc of the IEEE computer society annual workshop on VLSI (WVLSI’00), p 119

Ogras UY, Marculescu R, Choudhary P, Marculescu D (2007) Voltage-frequency island partitioning for GALS-based networks-on-chip. In: DAC ’07: proceedings of the 44th annual design automation conference, pp 110–115

Ogras UY, Marculescu R, Marculescu D, Jung EG (2009) Design and management of voltage-frequency island partitioned networks-on-chip. IEEE Trans Very Large Scale Integr Syst 17(3):330–341

Jang W, Ding D, Pan DZ (2008) A voltage-frequency island aware energy optimization framework for networks-on-chip. In: ICCAD ’08: proceedings of the 2008 IEEE/ACM international conference on computer-aided design, pp 264–269

Intel, Single-chip cloud computer. http://techresearch.intel.com/articles/Tera-Scale/1826.htm

Shang L, Peh L-S, Jha NK (2003) Dynamic voltage scaling with links for power optimization of interconnection networks. In: Proc international symposium on high-performance computer architecture

Worm F, Ienne P, Thiran P, Micheli GD (2002) An adaptive low power transmission scheme for on-chip networks. In: Proc international system synthesis symposium, pp 92–100

Kim EJ, Yum KH, Link GM, Vijaykrishnan N, Kandemir M, Irwin MJ, Yousif M, Das CR (2003) Energy optimization techniques in cluster interconnects. In: Proceedings of the 2003 international symposium on low power electronics and design, pp 459–464

Soteriou V, Peh L-S (2003) Dynamic power management for power optimization of interconnection networks using on/off links. In: Proc symposium on high performance interconnects, pp 15–20

Hu J, Marculescu R (2003) Exploiting the routing flexibility for energy/performance aware mapping of regular NoC architectures. In: Proc design, automation and test in Europe conference, pp 10688–10693

Shin D, Kim J (2004) Power-aware communication optimization for networks-on-chips with voltage scalable links. In: CODES ’04: proc of international conference on hardware/software codesign and system synthesis, pp 170–175

Marcon C, Calazans N, Moraes F, Susin A, Reis I, Hessel F (2005) Exploring NoC mapping strategies: an energy and timing aware technique. In: DATE ’05: proc of the conference on design, automation and test in Europe, pp 502–507

Chen G, Li F, Kandemir M (2006) Compiler-directed channel allocation for saving power in on-chip networks. In: POPL ’06: conference record of the 33rd ACM SIGPLAN-SIGACT symposium on principles of programming languages, pp 194–205

Li F, Chen G, Kandemir M (2005) Compiler-directed voltage scaling on communication links for reducing power consumption. In: Proceedings of the 2005 IEEE/ACM international conference on computer-aided design, pp 456–460

Kandemir M, Ozturk O (2008) Software-directed combined cpu/link voltage scaling fornoc-based cmps. In: Proceedings of the 2008 ACM SIGMETRICS international conference on measurement and modeling of computer systems, pp 359–370

Sheibanyrad A, Panades IM, Greiner A (2007) Systematic comparison between the asynchronous and the multi-synchronous implementations of a network on chip architecture. In: DATE ’07: proceedings of the conference on design, automation and test in Europe, pp 1090–1095

Bjerregaard T, Sparso J (2005) A router architecture for connection-oriented service guarantees in the mango clockless network-on-chip. In: DATE ’05: proceedings of the conference on design, automation and test in Europe, pp 1226–1231

Beigne E, Clermidy F, Vivet P, Clouard A, Renaudin M (2005) An asynchronous NoC architecture providing low latency service and its multi-level design framework. In: ASYNC ’05: proceedings of the 11th IEEE international symposium on asynchronous circuits and systems, pp 54–63

Leung L-F, Tsui C-Y (2007) Energy-aware synthesis of networks-on-chip implemented with voltage islands. In: DAC ’07: proceedings of the 44th annual design automation conference, pp 128–131

Guang L, Nigussie E, Koskinen L, Tenhunen H (2009) Autonomous DVFS on supply islands for energy-constrained NoC communication. In: ARCS ’09: proceedings of the 22nd international conference on architecture of computing systems, pp 183–194

Ghosh P, Sen A, Hall A (2009) Energy efficient application mapping to NoC processing elements operating at multiple voltage levels. In: NOCS ’09: proceedings of the 2009 3rd ACM/IEEE international symposium on networks-on-chip, pp 80–85

Schmitz MT, Al-Hashimi BM (2001) Considering power variations of DVS processing elements for energy minimisation in distributed systems. In: Proc international symposium on system synthesis, pp 250–255

Lim S, Bae Y, Jang G, Rhee B, Min S, Park C, Shin H, Park K, Kim C (1995) An accurate worst case timing analysis for RISC processors. In: IEEE transactions on software engineering, vol 21, pp 593–604

Dick RP (2003) Embedded system synthesis benchmarks suites. http://ziyang.eecs.umich.edu/dickrp/e3s/

Kernighan B, Lin S (1970) An efficient heuristic procedure for partitioning graphs. Bell Syst Tech J 49:291–307

Luo J, Jha NK (2007) Power-efficient scheduling for heterogeneous distributed real-time embedded systems. IEEE Trans Comput-Aided Des Integr Circuits Syst 26(6):1161–1170

Vahid F, Le TD (1997) Extending the Kernighan-Lin heuristic for hardware and software functional partitioning. Des Autom Embed Syst 2:237–261

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Shin, D., Kim, W., Kwon, S. et al. Communication-aware VFI partitioning for GALS-based networks-on-chip. Des Autom Embed Syst 15, 89–109 (2011). https://doi.org/10.1007/s10617-011-9070-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10617-011-9070-x