# Register Saturation in Instruction Level Parallelism Sid Touati

## ▶ To cite this version:

Sid Touati. Register Saturation in Instruction Level Parallelism. International Journal of Parallel Programming, 2005, 33 (4), pp.393-449. 10.1007/s10766-005-6466-x. hal-00130633

HAL Id: hal-00130633

https://hal.science/hal-00130633

Submitted on 28 Sep 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **Register Saturation in Instruction Level Parallelism**

Sid-Ahmed-Ali TOUATI University of Versailles, PRiSM laboratory, France touati@prism.uvsq.fr

## **Abstract**

The registers constraints are usually taken into account during the scheduling pass of an acyclic data dependence graph (DAG): any schedule of the instructions inside a basic block must bound the register requirement under a certain limit. In this work, we show how to handle the register pressure before the instruction scheduling of a DAG. We mathematically study an approach which consists in managing the exact upper-bound of the register need for all the valid schedules of a considered DAG, independently of the functional unit constraints. We call this computed limit the register saturation (RS) of the DAG. Its aim is to detect possible obsolete register constraints, i.e., when RS does not exceed the number of available registers. If it does, we add some serial edges to the original DAG such that the worst register need does not exceed the number of available registers. We propose an appropriate mathematical formalism for this problem. Our generic processor model takes into account superscalar, VLIW and EPIC/IA64 architectures. Our deeper analysis of the problem and our formal methods enable us to provide nearly optimal heuristics and strategies for register optimization in the face of ILP.

**Keywords** Register Requirement, Register Pressure, Instruction Level Parallelism, Integer Linear Programming, Optimizing Compilation.

## 1 Introduction

The introduction of instruction level parallelism (ILP) has rendered the classical techniques of register allocation for sequential code semantics inadequate. In [16], the authors showed that there is a phase ordering problem between classical register allocation techniques and ILP instruction scheduling. If a classical register allocation is done early, the introduced false dependences inhibit instruction scheduling from extracting a schedule with high amount of ILP. However, this conclusion does not prevent a compiler from effectively performing an early register allocation, with the condition that the allocator is sensitive to the scheduler, as done in [2, 18, 20, 23, 25, 26].

Some other studies [5, 8, 16, 24, 28] claim that it is better to combine instruction scheduling and register allocation in a single complex pass, arguing that applying each method separately has a negative influence on the efficiency of the other. However, we think that this phase ordering problem arises only if the applied first pass (ILP scheduler or register allocator) is "selfish". Indeed, we can effectively decouple register constraints from instruction scheduling if enough care is taken. In this paper, we show how we can treat register constraints before scheduling, and we explain why we think that our methods provide better techniques than the existing solutions.

The principal reason for handling register constraints before instruction scheduling is that register allocation is more important as an optimization issue than code scheduling. This is because performance is far more sensitive to memory accesses than to fine-grain scheduling (memory gap): a cache miss may inhibit the processor from achieving a high dynamic ILP, even if the scheduler has extracted it at compile time. Even if we expect spill code to exhibit high locality, and hence likely produces cache hits, this cannot be asserted at compile time. It is very hard for a compiler to guarantee the existence of data inside a memory hierarchy level. Consequently, it is difficult to really guarantee the latency of a memory operation at compile time. So, the schedule of the instructions computed by the compiler wouldn't act in harmony with the dynamic execution of

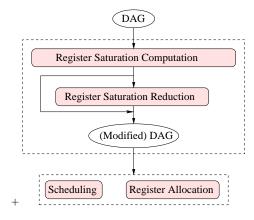

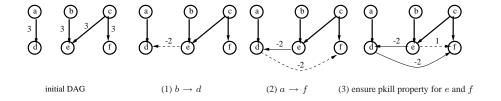

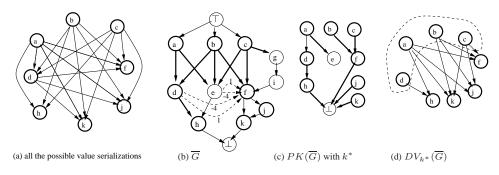

Figure 1. Early Register Pressure Management

the hardware. The authors in [15] relate that about 66% of application execution times are spent satisfying memory requests. Furthermore, memory requests exhibit a high potential for conflicts, even if they are data independent. These conflicts are due to micro-architectural restrictions and simplifications in the memory disambiguation mechanisms (load/store queues) and possible banking structure in cache levels [21]. These possible conflicts may cause severe performance degradation even in the presence of high levels of ILP, and even if the data is located in the cache [22]. Of course, our claim that spill code is more damaging than a weak static ILP extraction is more appropriate for those architectures where memory access latency is very long compared to the delay of calculation. This is the case in almost all high performance processors. If memory access delay is not critical, the register saturation concept may be useless.

Another reason for handling register constraints prior to ILP scheduling is that register constraints are much more complex than resource constraints. Scheduling under resource constraints is a performance issue. Given a data dependence graph (DDG), we are sure to find at least one valid schedule for any underlying hardware properties (a sequential schedule in extreme case, *i.e.*, no ILP). However, scheduling a DDG with a limited number of registers is more complex. Unless we generate superscalar codes with sequential semantics, we cannot guarantee in the case of VLIW the existence of at least one schedule. In some cases, we must introduce spill code and hence we change the problem (the input DDG). Also, a combined pass of scheduling with register allocation presents an important drawback if not enough registers are available. During scheduling, we may need to insert load-store operations if not enough free registers exist. We cannot guarantee the existence of a valid issue time for these introduced memory accesses in already scheduled code; resource or data dependence constraints may prohibit all possible issue slots inside the scheduled code. This fact forces an iterative process of scheduling followed by spilling until reaching a solution. Even if we can experimentally reduce the backtracking as in [31], this iterative aspect adds a high algorithmic complexity factor to a pass integrating both register allocation and scheduling. As far as we know, there is no formal solution that effectively solves this problem.

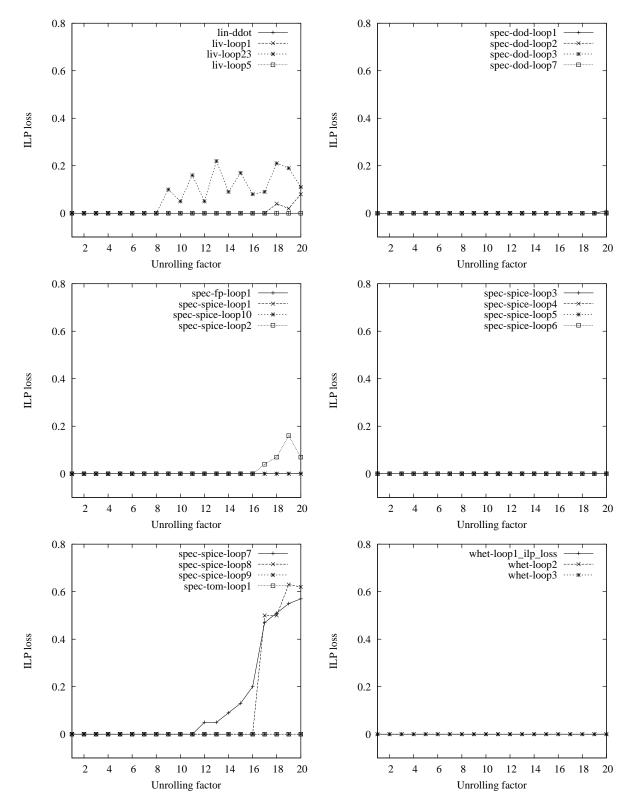

The above arguments suggest that we consider new ways of handling register pressure before starting the scheduling process. The scheduler should be freed from register constraints so that the schedule does not suffer from excessive serialization. This article synthesizes our contributions from [29, 30]. We study the concept of register saturation (RS), which prevents a DAG from producing an excessive number of simultaneously live values for all the valid schedules. Our pre-pass analyzes a DAG (with respect to control flow) to deduce the maximum register need among all schedules. We call this limit the *register saturation* (RS), because the register need can reach this limit but never exceed it. If RS exceeds the number of available registers, we introduce new edges in the DAG to reduce RS, as illustrated in Figure 1. In this paper, we give some theoretical results on RS and provide exact (optimal) and approximate methods for the problems of computing and reducing RS. After our RS analysis pass, the DAG is free from register constraints and can be sent to the scheduler and the register allocator.

This article is organized as follows. Section 2 presents our DAG and processor model which can be used for most of existing ILP architectures (superscalar, VLIW, EPIC/IA64). Section 3 provides some theoretical results on computing the RS that prove the NP-completeness of this problem. Section 4 presents an algorithmic heuristics for computing RS. Computing

the optimal RS by integer linear programming (intLP) is given in Section 5. Our intLP formulation use the linear writing of logical formulas ( $\Longrightarrow$ ,  $\Longleftrightarrow$ ,  $\lor$ ) and the max operator (max(x,y)) by introducing extra binary variables. If the RS exceeds the number of available registers, RS must be reduced. Section 6 proves that this problem is NP-hard. An algorithmic heuristics for reducing RS is given in Section 7 and an exact optimal solution is presented in Section 8. Section 9 presents our large range of experiments, which show that our heuristics are nearly optimal in practice. Before concluding, in Section 10 we discuss why the RS concept is a better way to handle register constraints prior to ILP scheduling compared to register minimization. To enhance readability, only the most important formal proofs are presented in this paper. The complete theoretical proofs are provided in the cited references.

## 2 DAG and Processor Model

A DAG  $G=(V,E,\delta)$  in our study represents the data dependences between the operations and any other serial constraints. Each operation u has a strictly positive latency lat(u). The DAG is defined by its set of nodes (operations) V, its set of edges (data dependences and serial constraints)  $E=\{(u,v)|\ u,v\in V\}$ , and  $\delta$  such that  $\delta(e)$  is the latency of the edge e in terms of processor clock cycles. We assume that the initial DAG contains only edges with positive latencies. This assumption is useful for some formal proofs. However, we will see in later sections (when reducing RS) that we can insert new edges with non-positive latencies.

A schedule  $\sigma$  of G is a function which gives an integer execution (issue) time for each operation:

$$\sigma$$

is valid  $\iff \forall e = (u, v) \in E, \quad \sigma(v) - \sigma(u) \ge \delta(e)$

The set of all valid acyclic schedules of G is denoted by  $\Sigma(G)$ .

To simplify the writing of some mathematical formulas, we assume that the DAG has one source  $(\top)$  and one sink  $(\bot)$ . If not, we introduce two fictitious nodes  $(\top,\bot)$  representing nops (evicted at the end of the RS analysis). We add a virtual serial edge  $e_1=(\top,s)$  to each source with  $\delta(e_1)=0$ , and an edge  $e_2=(t,\bot)$  from each sink with the latency of the sink operation  $\delta(e_2)=lat(t)$ . The total schedule time of a schedule is then  $\sigma(\bot)$ . The null latency of an added edge  $e_1$  is not inconsistent with our assumption that latencies must be strictly positive because the added virtual serial edges do not exist in the original DAG. Furthermore, we can avoid introducing these virtual nodes without any impact on our theoretical study, since their purpose is only to simplify some mathematical expressions.

We consider a target RISC-style architecture with multiple register types, where  $\mathcal{T}$  denotes the set of register types (for instance,  $\mathcal{T} = \{int, float\}$ ). We differentiate between statements and precedence constraints, based on whether they refer to values to be stored in registers or not.

- $V_{R,t} \subseteq V$  is the set of statements (operations) which define values to be stored in registers of type  $t \in \mathcal{T}$ . We simply call such statements *values*. We assume that each statement  $u \in V_{R,t}$  writes into at most one register of a type  $t \in \mathcal{T}$ . Statements which define multiple values with different types are accepted in our model if they do not define more than one value of a single type. We denote by  $u^t$  the value of type t defined by the operation u.

- $E_{R,t} \subseteq E$  is the set of data flow dependence edges through a value of type  $t \in \mathcal{T}$ . We call them flow edges.

- All the edges in  $E E_{R,t}$ , i.e. edges which are not data flow dependences, are called *serial* edges.

Basically, there are three types of ILP codes: superscalar, VLIW and EPIC. Superscalar codes can be simply considered as linear sequential programs. Even if the compiler try to generate efficient superscalar codes, the processor is the unique responsible for dynamically extracting ILP at execution time. So, code generation for such ILP codes write sequential ones, as if they would be executed by a sequential processor. However, VLIW codes contain information about parallel operations. The compiler has the task of statically extracting ILP and then generating the code by compacting the parallel operations into *Very Long Instructions Words*. The processor executes such instructions (containing many independent operations) sequentially. So, the compiler has the complete control of the dynamic execution of VLIW codes (except dynamic events, such as cache misses, exceptions, etc.). EPIC codes have a semantics that may be considered as a mixture between VLIW and superscalar: while the compiler include information about ILP in the code, the processor can use such ILP information at execution time, or can simply execute sequentially the program. From the compiler point of view, an EPIC processor can be viewed as a sequential (superscalar) or as VLIW processor.

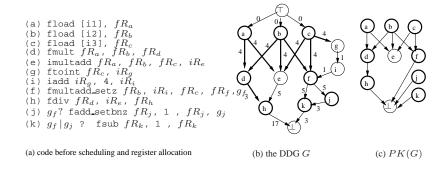

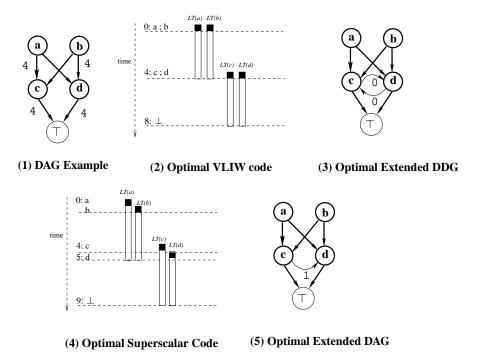

Figure 2. DAG Model

To accommodate static issue VLIW and EPIC/IA64 processors in which the hardware pipeline steps are visible to compilers (we allow for dynamically scheduled superscalar processors as well), we assume that reading from and writing into a register may be delayed from the beginning of the schedule time, and these delays are visible to the compiler (architecturally visible). We define two delay (offset) functions  $\delta_{r,t}$  and  $\delta_{w,t}$  in which: the read cycle of  $u^t$  from a register of type t is  $\sigma(u) + \delta_{r,t}(u)$ , and the write cycle of  $u^t$  into a register of type t is  $\sigma(u) + \delta_{w,t}(u)$ . By definition, we have  $\delta_{r,t}(u) \leq \delta_{w,t}(u) < lat(u)$ . For instance, according to superscalar and EPIC/IA64 code semantics,  $\delta_{r,t}$  and  $\delta_{w,t}$  are equal to zero. This is because, according to the semantics provided by the vendors, such codes can be considered as sequential (linear). Any register written by operation u at time slot c in the code, that register is assumed as busy at the program point c (no delay is architecturally visible). The same remark holds when reading from registers.

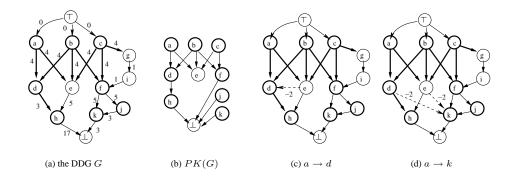

Figure 2.b gives the DAG that we use in this paper constructed from the code of part (a). In this example, we focus on the floating point registers: the values and flow edges are illustrated by bold lines. We assume for instance that each read occurs exactly at the schedule time and each write at the final execution step  $(\delta_r(u) = 0, \delta_w(u) = lat(u) - 1)$ . The nodes with non-bold lines are any other operations that do not write into registers (as stores), or write into registers of unconsidered types. The edges with non-bold lines represent the precedence constraints that are not flow dependences through registers, such as data dependences through memory, or through registers of unconsidered types, or any other serial constraints.

## **Notation and Definitions on DAGs**

In this paper, we use the following notations for a given DAG G = (V, E) (as those usually used in lattices and orders algebra):

- $\Gamma_G^+(u) = \{v \in V | (u, v) \in E\}$  successors of u in the graph G;

- $\Gamma_G^-(u) = \{v \in V | (v, u) \in E\}$  predecessors of u in the graph G;

- $\forall e = (u, v) \in E$  source $(e) = u \land target(e) = v$ . u, v are called endpoints;

- $\forall u, v \in V : u < v \iff \exists \text{ a path } (u, \dots, v) \text{ in } G$ ;

- $\forall u, v \in V : u || v \iff \neg(u < v) \land \neg(v < u)$ . u and v are said to be parallel;

- $\forall u \in V \uparrow u = \{v \in V | v = u \lor v < u\}$  u's ascendants including u. In other terms, a node u is an ascendant of a node v iff u = v or if there exists a path from u to v;

- $\forall u \in V \downarrow u = \{v \in V | v = u \lor u < v\}$  u's descendants including u. In other terms, a node u is a descendant of a node v iff u = v or if there exists a path from v to u;

- two edges e, e' are *adjacent* iff they share an endpoint;

- $A \subseteq V$  is an antichain iff all nodes belonging to A are parallel. Formally,  $A \subseteq V$  is an antichain in G iff  $\forall u, v \in A, u||v|$ ;

- AM is a maximal antichain iff its size in terms of number of nodes is maximal. Formally, AM is a maximal antichain  $\forall A$  antichain in G,  $|A| \leq |AM|$ ;

- the extended DAG  $G \setminus E'$  of G generated by the edges set  $E' \subseteq V^2$  is the DAG obtained from G after adding the edges in E'. As a consequence, any valid schedule of G' is necessarily a valid schedule for G:

$$G' = G \setminus E' \Longrightarrow \Sigma(G') \subseteq \Sigma(G)$$

- an extended graph has a similar definition as above, but it is not restricted to be a DAG;

- let  $I_1 = [a_1, b_1] \subset \mathbb{N}$  and  $I_2 = [a_2, b_2] \subset \mathbb{N}$  be two integer intervals. We say that  $I_1$  is before  $I_2$ , noted by  $I_1 \prec I_2$ , iff  $b_1 < a_2$ . We say that  $I_1$  finishes  $I_2$  iff  $b_1 = b_2$ .

## 3 Some Theoretical Results on Computing Register Saturation

In this section, we study some formal properties of register saturation in order to help us compute it algorithmically. For clarity and without loss of generality, let us focus on a single register type. Accordingly, our notation becomes  $V_R$  for the set of values of the implicit type we consider,  $E_R$  for the set of flow edges through a register of that type, and  $\delta_r$  and  $\delta_w$  for reading/writing delays. Also, we use the notation u for both the operation u and the value it produces.

## 3.1 Register Need of a Schedule

Given a DAG  $G = (V, E, \delta)$ , a value  $u \in V_R$  is alive from the point just after the writing clock cycle of u until the point of its last use (consumption). Values which are not read in G or are still alive when exiting the DAG are assumed to be kept in registers as exit values. We model these exit values by considering that the bottom node  $\bot$  consumes them. We define the set of consumers for each value  $u \in V_R$  as:

$$Cons(u) = \begin{cases} \{v \in V | (u, v) \in E_R\} & \text{if } \exists (u, v) \in E_R \\ \bot & \text{otherwise} \end{cases}$$

Given a schedule  $\sigma \in \Sigma(G)$ , the last consumption of a value is called the killing date and noted:

$$\forall u \in V_R, \quad kill_{\sigma}(u) = \max_{v \in Cons(u)} (\sigma(v) + \delta_r(v))$$

All the consumers of u whose reading time is equal to the killing date of u are called the killers of  $u^1$ . We assume that a value written at instant i in a register is available one step later. That is to say, if operation u reads from a register at instant i while operation v is writing in the same register at the same time, u does not get v's result but, gets the value previously stored in the register. Then, the *lifetime interval*  $LT_{\sigma}(u)$  of a value u according to  $\sigma$  is  $]\sigma(u) + \delta_w(u)$ ,  $kill_{\sigma}(u)]$ . This interval is left-open by convention only and can be changed without any consequence on our mathematical study.

Given the lifetime intervals of all the values, the register need of  $\sigma$  is the maximum number of values simultaneously alive:

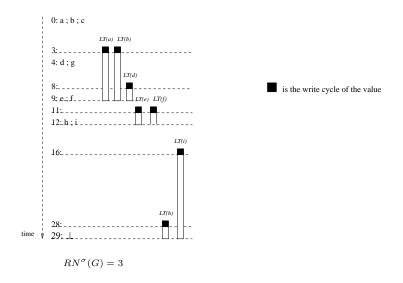

$$RN^{\sigma}(G) = \max_{0 \le i \le \sigma(\perp)} |vsa_{\sigma}(i)|$$

where  $vsa_{\sigma}(i) = \{u \in V_R | i \in LT_{\sigma}(u)\}$  is the set of values alive at time step i. A maximal set of values simultaneously alive are called *excessive values*. In other terms, if the register need at time step i is maximal, then all the values alive at this time step are called *excessive values*. Figure 3 is an example of a valid schedule for the previous DAG that needs three FP registers. The bars represent the lifetime intervals.  $\{e, f\}$  are the killers of b.  $\{a, b, d\}$  is a set of FP excessive values since they are the maximum number of values simultaneously alive of type float. 9 is a FP excessive clock cycle since at this time there are three FP values simultaneously alive. Note that we may have more than one set of excessive values, since the register need may be defined with many sets of values simultaneously alive.

<sup>&</sup>lt;sup>1</sup>While it is evident that a killer is unique in the case of linear codes (superscalar), VLIW codes may leads to multiple killers per value.

Figure 3. Register Need of Acyclic Schedules

## 3.2 Register Saturation Problem

The RS is the maximal register need for all the valid schedules of the DAG:

$$RS(G) = \max_{\sigma \in \Sigma(G)} RN^{\sigma}(G)$$

We call  $\sigma$  a saturating schedule iff  $RN^{\sigma}(G) = RS(G)$ . In this section, we study how to compute RS(G). We will see that this problem comes down to answering the question "which operation must kill this value?" When looking for saturating schedules, we do not worry about the total schedule time. Our aim is only to prove that the register need can reach the RS but cannot exceed it. Minimizing the total schedule time is considered in Section 6 when we reduce the RS. Furthermore, we will prove that, for the purpose of maximizing the register need, looking for only one suitable killer of a value is sufficient rather than looking for a group of killers: for any schedule that assigns more than one killer for a value u, we can build another schedule with at least the same register need such that this value u is killed by only one consumer. Therefore, the purpose of this section is to select a suitable killer for each value in order to saturate the register requirement.

Since we do not assume any schedule, the lifetime intervals are not defined yet, so we cannot know at which date a value is killed. However, we can deduce which consumers in Cons(u) are impossible killers for the value u. If  $v_1, v_2 \in Cons(u)$  and  $\exists$  a path  $(v_1 \cdots v_2)$ ,  $v_1$  is always scheduled before  $v_2$  by at least  $lat(v_1)$  processor cycles. Then  $v_1$  can never be the last reader of u (remember our assumption of positive latencies in the initial DAG). We can consequently deduce which consumers can "potentially" kill a value (possible killers). We denote by  $pkill_G(u)$  the set of operations which can kill a value.  $u \in V_R$ :

$$pkill_G(u) = \{v \in Cons(u) | \downarrow v \cap Cons(u) = \{v\}\}$$

A potential killing operation for a value u is simply a consumer of u that is neither a descendant nor an ascendant of another consumer of u. One can check that all operations in  $pkill_G(u)$  are parallel in G. Any operation which does not belong to  $pkill_G(u)$  can never kill the value u. The following lemma proves that for any value u and for any schedule  $\sigma$ , there exists a potential killer v that is a killer of u according to  $\sigma$ . Furthermore, for any potential killer v of a value v, there exists a schedule  $\sigma$  that makes v a killer of v.

**Lemma 1** Given a DAG  $G = (V, E, \delta)$ , then  $\forall u \in V_R$

$$\forall \sigma \in \Sigma(G), \quad \exists v \in pkill_G(u) : \quad \sigma(v) + \delta_r(v) = kill_\sigma(u)$$

(1)

$$\forall v \in pkill_G(u), \quad \exists \sigma \in \Sigma(G) : \quad kill_\sigma(u) = \sigma(v) + \delta_r(v)$$

(2)

Figure 4. Each Potential Killing Operation can Kill the Value

## **Proof:**

The proof of (1) is directly derived from the definition of pkill. Since

$$v \in pkill(u) \Longrightarrow \nexists v' \in Cons(u) \quad v < v'$$

then the killing date of u must be the schedule date of some operations in pkill(u). Let us prove that

$$\forall u \in V_R, \ \nexists v' \in Cons(u) - pkill(u), \ \exists \sigma \in \Sigma(G): \quad kill_{\sigma}(u) = \sigma(v') + \delta_r(v')$$

Suppose the converse is true.

$$\exists v' \in Cons(u) - pkill(u) \Longrightarrow \exists v \in pkill(u) | v' < v$$

Let lp(v', v) be the longest path from v' to v.

since

$$lp(v', v) \ge lat(v') > \delta_r(v') \Longrightarrow \sigma(v) - \sigma(v') > \delta_r(v')$$

Since  $\delta_r(v) \geq 0$ :

$$\sigma(v) + \delta_r(v) - \sigma(v') > \delta_r(v') \Longrightarrow \sigma(v) + \delta_r(v) > \sigma(v') + \delta_r(v')$$

Then

$$kill_{\sigma}(u) > \sigma(v) + \delta_r(v) > \sigma(v') + \delta_r(v')$$

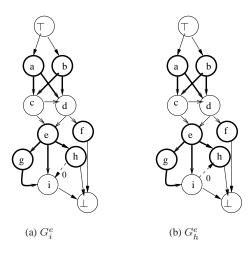

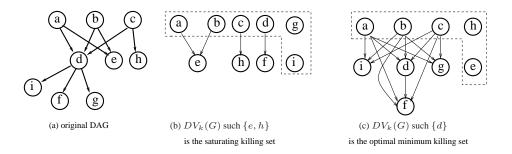

In order to prove (2) we create an extended DAG  $G_v^u = G \setminus^{E'}$ , for each  $v \in pkill(u)$ , to enforce v to be the last read of the value u.  $\forall v' \in pkill(u) - \{v\}$ , we add a serial edge e from v' to v with latency  $\delta(e) = \delta_r(v') - \delta_r(v)$ . Then, any schedule  $\sigma \in \Sigma(G_v^u)$  ensures  $\sigma(v) + \delta_r(v) \geq \sigma(v') + \delta_r(v')$  which means  $kill_{\sigma}(u) = \sigma(v)$ . Let's prove that  $G_v^u$  is still a DAG. Suppose the converse is true, i.e.,  $\exists u \in V_R, \ \exists v \in pkill(u)$  such that  $G_v^u$  is cyclic. Let  $C = (v, \cdots, v', v)$  be this cycle where the introduced edge is (v', v). We know that all the potential killing operations pkill(u) of a value u are parallel in G. However, before introducing this edge, a path  $P = v \leadsto v'$  means that v < v' in G which is a contradiction.

Figure 4 shows the two extended DAGs associated with e. The original DAG is presented in Figure 4. Here, we assume that all read delay are null. e has two potential killing operations  $\{h,i\}$ , so we have two extended DAG:  $G_i^e$  ensures that i kills e, and  $G_h^e$  that ensures that h kills e.

┙

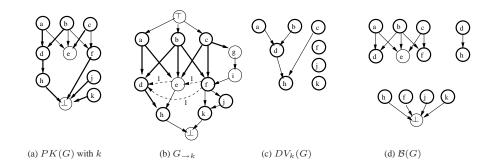

A potential killing DAG of G, noted  $PK(G) = (V, E_{PK})$ , is built to model the potential killing relations between the operations, (see Figure 2.c.), where:

$$E_{PK} = \{(u, v) | u \in V_R \land v \in pkill_G(u)\}$$

There may be more than one operation candidate for killing a value. Next, we prove that looking for a unique suitable killer for each value is sufficient for maximizing the register need: the next theorem proves that for any schedule that assigns more than one killer for a value, we can build another schedule with at least the same register need such that this value is killed by only one consumer. Consequently, our formal study will look for a unique killer for each value instead of looking for a group of killers.

**Theorem 1** Let  $G = (V, E, \delta)$  be a DAG and a schedule  $\sigma \in \Sigma(G)$ . If there is at least one excessive value that has more than one killer according to  $\sigma$ , then there exists another schedule  $\sigma' \in \Sigma(G)$  such that:

$$RN^{\sigma'}(G) \ge RN^{\sigma}(G)$$

and each excessive value is killed by a unique killer according to  $\sigma'$ .

#### **Proof:**

We suppose that there exists a schedule  $\sigma \in \Sigma(G)$  with at least one excessive value that has more than one killer:

$$\exists \sigma \in \Sigma(G), \exists u \in EV^{\sigma}(G) : |killers_{\sigma}(u)| > 1$$

where  $EV^{\sigma}(G)$  is a set of excessive values assuming  $\sigma$  as a schedule for G. We show in this proof how to build a new schedule  $\sigma' \in \Sigma(G)$  such that u is killed by a unique killer and  $\sigma'$  needs at least as many registers as  $\sigma$  does.

Suppose that u has j killers according to  $\sigma$ , and we note them:

$$killers_{\sigma}(u) = \{k_1, ..., k_j\}$$

with  $kill_{\sigma}(u) = \sigma(k_1) + \delta_r(k_1) = \cdots = \sigma(k_j) + \delta_r(k_j)$ . We choose one killer within this set to be the only one killer of u according to  $\sigma'$ , say  $k_1$ . We build  $\sigma'$  by "shifting" down  $k_1$  and all its descendants with a strictly positive factor, say 1:

$$\forall v \in V \quad \sigma'(v) = \begin{cases} \sigma(v) + 1 & \text{if } v \in \downarrow k_1 \\ \sigma(v) & \text{otherwise} \end{cases}$$

Now, we prove that  $\sigma'$  is valid and needs at least as many registers as  $\sigma$  does, and that  $k_1$  is the only killer of u according to  $\sigma'$ .

$\sigma'$  is valid: we can easily check that any dependence  $\forall e = (v_1, v_2) \in E$  is satisfied by  $\sigma'$ :

1. if both  $v_1, v_2 \not\in \downarrow k_1$ , then

$$\sigma'(v_2) - \sigma'(v_1) = \sigma(v_2) - \sigma(v_1) > \delta(e)$$

2. in the case where  $v_1 \not\in \downarrow k_1 \land v_2 \in \downarrow k_1$

$$\sigma'(v_2) - \sigma'(v_1) = \sigma(v_2) + 1 - \sigma(v_1) > \delta(e)$$

- 3. the case of  $v_1 \in \downarrow k_1 \land v_2 \not\in \downarrow k_1$  is impossible because the edge  $e = (v_1, v_2)$  exists;

- 4. in the case where both  $v_1, v_2 \in \downarrow k_1$ , then

$$\sigma'(v_2) - \sigma'(v_1) = \sigma(v_2) + 1 - \sigma(v_1) - 1 \ge \delta(e)$$

$RN^{\sigma'} \ge RN^{\sigma}$ : let t be an excessive clock cycle according to  $\sigma$ , i.e, a clock cycle t where the excessive values are simultaneously alive during it:

$$\forall v \in EV^{\sigma}(G): \qquad t \in LT_{\sigma}(v)$$

$$\Longrightarrow \forall v \in EV^{\sigma}(G): \qquad \sigma(v) + \delta_{w}(v) < t \leq kill_{\sigma}(v)$$

Here, we want to prove that these excessive values according to  $\sigma$  are still alive during t according to  $\sigma'$ . Any value  $v \in EV^{\sigma}(G)$  has the same definition date in  $\sigma'$  as in  $\sigma$ , this is because only  $\downarrow k_1$  nodes have been shifted down and :

$$\forall v \in EV^{\sigma}(G) - \{u\} : v \not\in \downarrow k_1$$

otherwise  $LT_{\sigma}(u) \prec LT_{\sigma}(v)$  which is in contradiction with  $u, v \in EV^{\sigma}(G)$ . Then

$$\forall v \in EV^{\sigma}(G): \quad \sigma'(v) = \sigma(v)$$

However, the killing date of any excessive value  $v \in EV^{\sigma}(G)$  could be increased by the translation factor 1:

$$\forall v \in EV^{\sigma}(G): \quad kill_{\sigma}(v) \leq kill_{\sigma'}(v)$$

which gives

$$\forall v \in EV^{\sigma}(G) : \quad \sigma'(v) < t \le kill_{\sigma'}(v)$$

$$\Longrightarrow RN^{\sigma'} \ge |EV^{\sigma}(G)| = RN^{\sigma}(G)$$

$k_1$  is the unique killer of u: since  $k_1 \in pkill_G(u)$ , there is no other potential killer  $k \in pkill(u) \land k \neq k_1$  such as  $k \in \downarrow k_1$ . Otherwise,  $k_1$  cannot kill u (pkill operations property). In this case  $\sigma'(k) = \sigma(k)$  while  $\sigma'(k_1) = \sigma(k) + 1$ . We conclude

$$\forall k \in pkill_G(u) - \{k_1\}$$

$\sigma'(k_1) + \delta_r(k_1) > \sigma'(k) + \delta_r(k) \Longrightarrow killers_{\sigma'}(u) = \{k_1\}$

Finally, generalizing to an arbitrary number of excessive values like u (those that have more than one killer and that are simultaneously alive with u) is obviously done by iteratively building new  $\sigma'$  schedule for each of these values. However, we must take a precaution. Indeed, if we treat an excessive value  $u_1$  by shifting down one of its killers, and then we proceed to another excessive value  $u_2$ , we cannot guarantee that shifting down  $u_2$ 's killer would not shift down other  $u_1$  consumers (and hence,  $u_1$  becomes killed by multiple consumers). To break this recursivity, we proceed as follows. When we treat an excessive value u by shifting down its killer k(v), we add an edge to the DAG from each potential killer of u (except k(u)) to k(u). Hence, when we iterate over the remaining excessive values, any shifting down action would always guarantee the existence of a unique killer for the previously treated values. The added edges does not introduce a cycle since they define a strict order between the potential killing nodes.

┙

**Corollary 1** Given a DDG  $G = (V, E, \delta)$ , there is always a saturating schedule for G with the property that each saturating value has a unique killer.

## **Proof:**

Direct consequence of Theorem 1.

┙

Figure 5. Valid Killing Function and Bipartite Decomposition

(a) An arbitrary DAG G with a killing function

(b) The extended graph associated with the killing function

Figure 6. An Example of an Invalid Killing Function

Let us begin by assuming a killing function, k, which guarantees that an operation  $v \in pkill_G(u)$  is the killer of  $u \in V_R$ . If we assume that k(u) is the unique killer of  $u \in V_R$ , we must always verify the following assertion:

$$\forall v \in pkill_G(u) - \{k(u)\}: \quad \sigma(v) + \delta_r(v) < \sigma(k(u)) + \delta_r(k(u))$$

(3)

There is a family of schedules that ensures this assertion. In order to define them, we extend G by new serial edges that force all the potential killing operations of each value u to be scheduled before k(u). This leads us to define an extended DAG associated with k and denoted  $G_{\rightarrow k} = G \setminus^{E_k}$  where:

$$E_k = \left\{ e = (v, k(u)) | u \in V_R \ v \in pkill_G(u) - \{k(u)\} \text{ with } \delta(e) = \delta_r(v) - \delta_r(k(u)) + 1 \right\}$$

Then, any schedule  $\sigma \in \Sigma(G_{\to k})$  ensures Property 3. The necessary existence of such a schedule defines the condition for a *valid killing function*:

k is a valid killing function

$$\iff G_{\rightarrow k}$$

is acyclic

Figure 5 gives an example of a valid killing function k. This function is illustrated by bold edges in part (a), where each target of a bold edge kills its source. Part (b) is the DAG associated with k.

According to our definition, invalid killing functions may exist. Figure 6 is an example, where Part (a) illustrates an arbitrary DAG with a killing function (the source of each bold edge is killed by its sink). Part (b) shows that the extended graph associated with the killing function is cyclic. According to our definition, the killing function defined in Part (a) isn't valid.

Provided a valid killing function k, we can deduce the values which can never be simultaneously alive for any  $\sigma \in \Sigma(G_{\to k})$ . Let  $\downarrow_R(u) = \downarrow u \cap V_R$  be the set of the descendant operations  $of u \in V$  that are values. We call them *descendant values*.

**Lemma 2** Given a DAG  $G = (V, E, \delta)$  and a valid killing function k, then:

1. the descendant values of k(u) cannot be simultaneously alive with u:

$$\forall u \in V_R, \ \forall \sigma \in \Sigma(G_{\to k}), \ \forall v \in \downarrow_R k(u) : LT_{\sigma}(u) \prec LT_{\sigma}(v)$$

(4)

2. there exists a valid schedule which makes any values non-descendant of k(u) simultaneously alive with u, i.e.  $\forall u \in V_R$ ,  $\exists \sigma \in \Sigma(G_{\rightarrow k})$ :

$$\forall v \in \left(\bigcup_{v' \in pkill_G(u)} \downarrow_R v'\right) - \downarrow_R k(u) : LT_{\sigma}(u) \cap LT_{\sigma}(v) \neq \phi$$

(5)

**Proof:**

A complete proof is given in [30], Appendix A, Section A.1.4, page 253.

┙

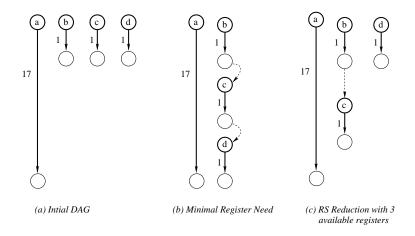

We define a DAG which models the values that can never be simultaneously alive when assuming k as a killing function. The *disjoint value DAG* of G associated with k, and denoted  $DV_k(G) = (V_R, E_{DV})$  is defined by:

$$E_{DV} = \{(u, v) | u, v \in V_R \land v \in \downarrow_R k(u) \}$$

Any edge (u, v) in  $DV_k(G)$  means that u's lifetime interval is always before v's lifetime interval according to any schedule of  $G_{\rightarrow k}$ , see Figure 5.c (this DAG is simplified by transitive reduction). This definition permits us to state Theorem 2 as follows.

**Theorem 2** Given a DAG  $G = (V, E, \delta)$  and a valid killing function k, let  $AM_k$  be a maximal antichain in the disjoint value DAG  $DV_k(G)$ . Then:

• the register need of any schedule of  $G_{\rightarrow k}$  is always less than or equal to the size of a maximal antichain in  $DV_k(G)$ . Formally,

$$\forall \sigma \in \Sigma(G_{\to k}), \ RN^{\sigma}(G) \le |AM_k|$$

• there is always a schedule which makes all the values in this maximal antichain simultaneously alive. Formally,

$$\exists \sigma \in \Sigma(G_{\to k}), \ RN^{\sigma}(G) = |AM_k|$$

#### **Proof:**

First property Let us begin by proving that:

$$\forall \sigma \in \Sigma(G_{\to k}) : RN^{\sigma}(G) \le |AM_k|$$

$DV_k(G)$ , the disjoint value DAG, models the order between value lifetime in any schedule of  $G_{\to k}$ . The definition of the disjoint value DAG states that  $\forall \sigma \in \Sigma(G_{\to k}), \forall u, v \in V_R$ :

$$u < v \text{ in } DV_k(G) \Longleftrightarrow u < k(u) \le v \text{ in } G_{\rightarrow k}$$

If v=k(u), then  $\sigma(u)+\delta_w(u)<\sigma(v)+\delta_r(v)$ , because of true data dependence. By hypothesis on DAG model we have  $\delta_r(v)\leq \delta_w(v)$ , then  $\sigma(u)+\delta_w(u)<\sigma(v)+\delta_w(v)$ . In the case where  $v\neq k(u)$ , any path from k(u) to v is a data dependence path with strictly positive integer latencies. We deduce that:

$$\forall \sigma \in \Sigma(G_{\to k}) \quad \sigma(k(u)) + \delta_r(k(u)) \le \sigma(v) + \delta_w(v)$$

That is,

$$kill_{\sigma}(u) \leq \sigma(v) + \delta_w(v)$$

We deduce that the following assertion is correct:

$$\forall \sigma \in \Sigma(G_{\to k}) \quad u \sim v \text{ in } DV_k(G) \implies LT_{\sigma}(u) \cap LT_{\sigma}(v) = \phi$$

We rewrite it:  $\forall \sigma \in \Sigma(G_{\rightarrow k})$

$$\begin{array}{ll} LT_{\sigma}(u)\cap LT_{\sigma}(v)\neq\phi&\Longrightarrow&u||v\text{ in }DV_{k}(G)\\ &\Longrightarrow&\{u,v\}\in vsa^{\sigma}(c)\,,c\in LT_{\sigma}(u)\cap LT_{\sigma}(v) \end{array}$$

Then, any values simultaneously alive for  $\sigma \in \Sigma(G_{\to k})$  belong to an antichain in  $DV_k(G)$ :

$$\forall 0 \leq c < \overline{\sigma}, \ \exists A \text{ an antichain of } DV_k(G) \quad vsa^{\sigma}(c) \subseteq A$$

Since  $RN^{\sigma}(G_{\to k}) = \max_{0 \le c \le \overline{\sigma}} |vsa^{\sigma}(c)|$  and  $|vsa^{\sigma}(c)| \le |AM_k|$ , we conclude that  $RN^{\sigma}(G) = \max_{0 \le c \le \overline{\sigma}} |vsa^{\sigma}(c)| \le |AM_k|$ .

**Second Property** Now, given a set of excessive values  $AM_k$ , we must prove that:

$$\exists \sigma \in \Sigma(G_{\rightarrow k}) : RN^{\sigma}(G) = |AM_k|$$

We have to build a schedule  $\sigma$  such that  $RN^{\sigma}(G) = |AM_k|$ . For this purpose, we consider  $G_{\to k}$  in order to ensure the killing relation, and we add some serial edges to enforce the values in  $AM_k$  in order to be simultaneously alive. This leads us to a new extended DAG  $G' = G_{\to k} \setminus^{E'}$  and

$$\forall \sigma \in \Sigma(G') \ \forall u, v \in AM_k : LT_{\sigma}(u) \cap LT_{\sigma}(v) \neq \phi$$

A sufficient condition that two values u, v in  $AM_k$  must satisfy to be simultaneously alive for any schedule of  $G_{\rightarrow k}$  is

$$\left[v < u < k(v) \land lp(v, u) \ge \delta_w(v) - \delta_w(u) \land \\

\land lp(u, k(v)) > \delta_w(u) - \delta_r(k(v))\right] \tag{6}$$

$$\lor \left[u < v < k(u) \land lp(u, v) \ge \delta_w(u) - \delta_w(v) \land \\

\land lp(v, k(u)) > \delta_w(v) - \delta_r(k(u))\right] \tag{7}$$

$$\lor \left[k(u) = k(v)\right] \tag{8}$$

with lp(u, v) for  $u, v \in V$  denoting the longest path from u to v.

These conditions ensure that  $\forall \sigma \in \Sigma(G_{\rightarrow k}) \ \forall u, v \in V_R$ :

$$\begin{array}{ccc} u,v \text{ satisfy (6)} & \Longrightarrow & \sigma(u) + \delta_w(u) \geq \sigma(v) + \delta_w(v) \\ & & \wedge \sigma(k(v)) + \delta_r(k(v)) > \sigma(u) + \delta_w(u) \\ u,v \text{ satisfy (7)} & \Longrightarrow & \sigma(v) + \delta_w(v) \geq \sigma(u) + \delta_w(u) \\ & & \wedge \sigma(k(u)) + \delta_r(k(u)) > \sigma(v) + \delta_w(v) \\ u,v \text{ satisfy (8)} & \Longrightarrow & kill_\sigma(u) = kill_\sigma(v) \end{array}$$

Then, by using usual interval order algebra notations:

$$u, v ext{ satisfy Cond. (6)} \implies \neg(LT_{\sigma}(u) \prec LT_{\sigma}(v) \lor LT_{\sigma}(u) \succ LT_{\sigma}(v))$$

$u, v ext{ satisfy Cond. (7)} \implies \neg(LT_{\sigma}(u) \succ LT_{\sigma}(v) \lor LT_{\sigma}(u) \prec LT_{\sigma}(v))$

$u, v ext{ satisfy Cond. (8)} \implies LT_{\sigma}(u) ext{ finishes } LT_{\sigma}(v)$

If two values in  $u,v\in AM_k$  do not satisfy any of these conditions, then we use Algorithm 1 to enforce them. This algorithm uses the boolean function  $vsa_{G'}(u,v)$  to check if two values u,v satisfy one of the above conditions. We add iteratively serial edges until all values in  $AM_k$  satisfy one of these conditions. The added serial edges do not introduce a cycle and any schedule  $\sigma$  of G' has  $RN^{\sigma}(G') = |AM_k|$ . All this is proved by Lemma 3, as follows.

$_{\perp}$

# **Algorithm 1** Extended $G_{\rightarrow k}$ to enforce values to be simultaneously alive

```

Require: a valid killing function k

construct the extended graph G_{\rightarrow k} associated with k

G' \leftarrow G_{\rightarrow k} {the final extended graph is initialized}

search for a maximal antichain AM_k in the disjoint value DAG DV_k(G)

for all u \in AM_k do

for all v \in AM_k | u \neq v do

if \neg vsa_{G'}(u,v) then

if u||v in G' then

if \neg (k(u) < v) then

add the serial edges e=(u,v), e'=(v,k(u)) to G' with \delta(e)=\delta_w(u)-\delta_w(v) and \delta(e')=\delta_w(v)-\delta_w(v)

\delta_r(k(u)) + 1

else \{\neg(k(v) < u) \text{ certainly}\}\

add the serial edges e=(v,u), e'=(u,k(v)) to G' with \delta(e)=\delta_w(v)-\delta_w(u) and \delta(e')=\delta_w(u)-\delta_w(u)

end if

else

if v < u then

add the serial edges e = (v, u) and e' = (u, k(v)) to G' with \delta(e) = \delta_w(v) - \delta_w(u) and \delta(e') = \delta_w(u) - \delta_w(u)

\delta_r(k(v)) + 1

else \{u < v\}

add the serial edges e = (u, v) and e' = (v, k(u)) to G' with \delta(e) = \delta_w(u) - \delta_w(v) and \delta(e') = \delta_w(v) - \delta_w(v)

\delta_r(k(u)) + 1;

end if

end if

end if

end for

end for

```

**Lemma 3** Let  $G = (V, E, \delta)$  be a DAG. Let k be a killing function and  $AM_k$  be a maximal antichain in the disjoint value DAG  $DV_k(G)$ . The extended graph  $G' = G_{\rightarrow k} \setminus^{E'}$  produced by Algorithm 1 has the two following properties:

- 1. it a DAG;

- 2. for any schedule  $\sigma$  of G', the lifetime intervals of any two values belonging to the maximal antichain  $AM_k$  interfere. Formally,

$$\forall u, v \in AM_k, \ \forall \sigma \in \Sigma(G'): LT_{\sigma}(u) \cap LT_{\sigma}(v) \neq \phi$$

## **Proof:**

We proceed by induction. We prove that after exiting Algorithm 1, G' is still a DAG. We also prove that the algorithm makes all values in  $AM_k$  satisfying one of the conditions (6), (7) or (8). For this last condition, if two values do not satisfy it in the DAG  $G_{\rightarrow k}$ , they cannot satisfy it in G': this is because the killing operations

Figure 7. Making Values Simultaneously Alive

has been fixed in  $G_{\rightarrow k}$ . So, if u, v do not satisfy Condition (8), Algorithm 1 can only force them to satisfy Condition (6) or Condition (7).

We prove also the following property

$$\forall u, v \in AM_k \quad \neg (k(v) < u \lor k(u) < v) \text{ in } G'$$

which is the same as proving that Algorithm 1 guarantees that all values in  $AM_k$  are forced to be simultaneously alive in G':

$$\nexists u, v \in AM_k | u \sim v \text{ in } DV_k(G')$$

Initially, this is correct because  $u, v \in AM_k \Longrightarrow u \not\in \downarrow_R k(v) \land v \not\in \downarrow_R k(u)$ . In this proof, we note  $G_i'$  the graph built after exiting iteration i. Suppose that after exiting iteration i-1,  $G_{i-1}'$  is still a DAG and

$$\forall u, v \in AM_k \quad \neg (k(v) < u \lor k(u) < v) \text{ in } G'_{i-1}$$

Let  $u_i$  and  $v_i$  be the two chosen values at iteration i which do not satisfy any of the conditions. Let us prove now that  $G_i'$  is still a DAG and the two chosen values  $u_i, v_i \in AM_k$  satisfy one of the conditions after exiting iteration i. Furthermore, we prove that after exiting this iteration

$$\nexists w \in AM_k | k(u_i) < w \lor k(v_i) < w \text{ in } G_i'$$

Our algorithm introduces serial edges in four cases:

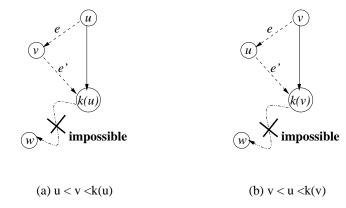

- 1.  $u_i||v_i \text{ in } G'_{i-1}$ , then

- if  $\neg(k(u_i) < v_i)$ , the two introduced edges  $e = (u_i, v_i), e' = (v_i, k(u_i))$  cannot introduce a cycle, because  $u_i < k(u_i)$  in  $G'_{i-1}$ , see Figure 7.a. Now they are satisfying Cond. (7). Also, after introducing these edges, the following property is satisfied:

$$\nexists w \in AM_k | k(u_i) < w \lor k(v_i) < w \text{ in } G_i'$$

Suppose the converse is true, *i.e.*,

$$\exists w \in AM_k | k(u_i) < w \lor k(v_i) < w \text{ in } G_i'$$

If  $k(u_i) < w$  in  $G'_i \Longrightarrow k(u_i) < w$  in  $G'_{i-1}$  because we have not introduced a serial edge from  $k(u_i)$ , which is impossible because of induction hypothesis.

If  $k(v_i) < w$  in  $G'_i \Longrightarrow k(v_i) < w$  in  $G'_{i-1}$  because we have not introduced a serial edge from  $k(v_i)$ , which is also impossible because of induction hypothesis;

• else  $\neg (k(v_i) < u_i)$  certainly, because otherwise

$$v_i < k(v_i) < u_i \land u_i < k(u_i) < v_i \Longrightarrow u_i < v_i \land v_i < u_i \text{ in } G'_{i-1} \text{ (impossible)}$$

Then the introduced edges  $e = (v_i, u_i), e' = (u_i, k(v_i))$  cannot introduce any cycle because  $v_i < k(v_i)$  in  $G'_{i-1}$ , see Figure 7.b. Now they are satisfying Cond. (6). Also, after introducing these edges, the following property is satisfied:

$$\nexists w \in AM_k | k(u_i) < w \lor k(v_i) < w \text{ in } G_i'$$

The proof is similar to the above case;

2. if  $v_i < u_i$  in  $G'_{i-1}$ , then by induction hypothesis  $\neg(k(v_i) < u_i)$  in  $G'_{i-1}$ . The two introduced edges  $e = (v_i, u_i)$  and  $e' = (u_i, k(v_i))$  cannot cause any cycle. Now they are satisfying Cond. (6). Also, after introducing these edges,

$$\nexists w \in AM_k | k(u_i) < w \lor k(v_i) < w \text{ in } G_i'$$

The proof is similar to the case above;

3.  $u_i < v_i$  in  $G'_{i-1}$ , this case is similar to above. Now they are satisfying Cond. (7).

After  $n = |AM_k|^2$  iterations, we conclude that :

$$\forall u, v \in AM_k$$

$u, v$  satisfy one of the conditions (6), (7) or (8)

and then

$$\forall u, v \in AM_k \ \forall \sigma \in \Sigma(G')$$

$LT_{\sigma}(u) \cap LT_{\sigma}(v) \neq \phi$

Theorem 2 allows us to rewrite the RS formula as

$$RS(G) = \max_{k \text{ a valid killing function}} |AM_k|$$

where  $AM_k$  is a maximal antichain in  $DV_k(G)$ . We refer to the problem of finding such a killing function as the maximizing maximal antichain problem (MMA). We call each solution for the MMA problem a saturating killing function, and  $AM_k$  its saturating values. A saturating killing function means a killing function that produces a saturated register need. The saturating values are the values that are simultaneously alive, and their number reaches the maximal possible register need. Unfortunately,

**Theorem 3** Given a DAG  $G = (V, E, \delta)$ , computing a saturating killing function is NP-complete.

## **Proof:**

A complete proof is given in [30], Appendix A, Section A.1.5, page 253.

**Corollary 2** Given a DAG  $G = (V, E, \delta)$ , computing the register saturation is NP-complete.

#### **Proof:**

A complete proof is given in [30], Appendix A, Section A.1.6, page 257.

┙

┙

┙

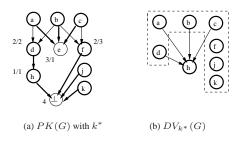

## 4 A Heuristics for Computing the RS

This section presents our heuristics to approximate an optimal k by another valid killing function  $k^*$ . An optimal k is simply a killing function that defines the optimal register saturation. We have to choose a killing operation for each value such that we maximize the parallel values in  $DV_k(G)$ . Our heuristics compute a valid killing function by focusing on the potential killing DAG PK(G), starting from source nodes to sinks. Our aim is to select a group of killing operations for a group of parents that keeps as many descendant values alive as possible. The main steps of our heuristics are:

- 1. decompose the potential killing DAG PK(G) into connected bipartite components;

- 2. for each bipartite component, search for the best saturating killing set (defined below);

- 3. choose a killing operation within the saturating killing set (defined below).

We decompose the potential killing DAG into connected bipartite components (CBC) in order to choose a common saturating killing set for a group of parents. Our purpose is to have a maximum number of children and their descendant's values simultaneously alive with their parent's values. A CBC  $cb = (S_{cb}, T_{cb}, E_{cb})$  is a partition of a subset of operations into two disjoint sets where:

- $E_{cb} \subseteq E_{PK}$  is a subset of the potential killing relations;

- $S_{cb} \subseteq V_R$  is the set of the parent values, such that each parent is killed by at least one operation in  $T_{cb}$ ;

- $T_{cb} \subset V$  is the set of the children, such that any operation in  $T_{cb}$  can potentially kill at least one value in  $S_{cb}$ .

A bipartite decomposition of the potential killing graph PK(G) is the set (see Figure 5.d)

$$\mathcal{B}(G) = \{cb = (S_{cb}, T_{cb}, E_{cb}) | \forall e \in E_{PK} \exists cb \in \mathcal{B}(G) : e \in E_{cb} \}$$

Note that the parents, as well as the children, are parallel inside the potential killing DAGPK(G). Formally,

$$\forall cb \in \mathcal{B}(G) \ \forall s, s' \in S_{cb} \ \forall t, t' \in T_{cb} : \quad s||s' \wedge t||t' \ \text{in } PK(G)$$

A saturating killing set SKS(cb) of a bipartite component  $cb = (S_{cb}, T_{cb}, E_{cb})$  is a subset of children  $T'_{cb} \subseteq T_{cb}$ . Such subset provides a unique killer for each value present in the set  $S_{cb}$  of parents. Such unique killer is chosen so as to minimize the number of descendant values of all the killers in  $T_{cb}$ . The dual consequence is to get a maximal number of values simultaneously alive with the parent values belonging to  $S_{cb}$ .

**Definition 1 (Saturating Killing Set)** Given a DAG  $G = (V, E, \delta)$ , a saturating killing set SKS(cb) of a connected bipartite component  $cb \in \mathcal{B}(G)$  is a subset  $T'_{cb} \subseteq T_{cb}$ , such that:

1. killing constraints: each parent must be killed

$$\bigcup_{t \in T'_{cb}} \Gamma^-_{cb}(t) = S_{cb}$$

2. objective function: minimize the number of descendant values of  $T'_{cb}$

$$\min |\bigcup_{t \in T'_{cb}} \downarrow_R t|$$

Unfortunately, computing a SKS is also NP-complete (the proof is the same as Theorem 3's proof).

A Heuristics for Finding a SKS Intuitively and according to Lemma 2, we should choose a subset of children in a bipartite component that would kill the greatest number of parents while minimizing the number of descendant values. We define a cost function  $\rho$  that enables us to choose the best candidate child. Given a bipartite component  $cb = (S_{cb}, T_{cb}, E_{cb})$  and a set Y of (cumulated) descendant values and a set X of not (yet) killed parents, the cost of a child  $t \in T_{cb}$  is:

$$\rho_{X,Y}(t) = \begin{cases} \frac{|\Gamma_{cb}^-(t) \cap X|}{|\downarrow_R t \cup Y|} & \text{if } \downarrow_R t \cup Y \neq \phi \\ |\Gamma_{cb}^-(t) \cap X| & \text{otherwise} \end{cases}$$

The first case enables us to select the child which covers the greatest number of non-killed parents, with a corresponding minimum number of descendant values. If there are no descendant values, then we choose the child that covers the most non-killed parents.

#### **Algorithm 2** Greedy-k: a heuristics for the MMA problem

```

Require: a DAG G = (V, E, \delta)

for all values u \in V_R do

k^*(u) = \bot {all values are initially non killed}

end for

build \mathcal{B}(G) the bipartite decomposition of PK(G).

for all bipartite component cb = (S_{cb}, T_{cb}, E_{cb}) \in \mathcal{B}(G) do

X := S_{cb} {all parents are initially uncovered}

Y := \phi {initially, no cumulated descendant values}

SKS^*(cb) := \phi

while X \neq \phi do {build the SKS for cb}

select the child t \in T_{cb} with the maximal cost \rho_{X,Y}(t)

SKS^*(cb) := SKS^*(cb) \cup \{t\}

X := X - \Gamma_{cb}^{-}(t) \{ \text{remove covered parents} \}

Y := Y \cup \bigcup_R t {update the cumulated descendent values}

end while

for all t \in SKS^*(cb) do {in decreasing cost order}

for all parent s \in \Gamma_{cb}^-(t) do

if k^*(s) = \bot then {kill non killed parents of t}

k^*(s) := t

end if

end for

end for

end for

```

Algorithm 2 gives a greedy heuristics that searches for an approximation  $SKS^*$  and computes a killing function  $k^*$  in polynomial time. Our heuristics has the following property.

**Corollary 3** Let  $G = (V, E, \delta)$  be a DAG. If PK(G) is a tree, then Greedy-k computes an optimal register saturation with a polynomial time complexity.

## **Proof:**

Trivially, each value has at most one possible killer, *i.e.*, there is only one choice for the killing function. Then, the saturating values are simply the sources of the potential killing DAG PK(G). Expression trees for instances belong to this class of DAGs, because their potential killing DAGs are trees.

┙

Figure 8. Example of Computing the Register Saturation

Since the approximated killing function  $k^*$  is valid, Theorem 2 ensures that we can always find a valid schedule which requires exactly  $|AM_{k^*}|$  registers. Consequently, our heuristics do not compute an upper bound of the optimal register saturation, and the optimal RS can be greater than the one computed by Greedy-k. A conservative heuristic which computes a solution exceeding the optimal RS cannot ensure the existence of a valid schedule which reaches the computed limit, and hence it would imply an unnecessary RS reduction process and a waste of registers. The validity of the killing function is a key condition because it ensures the existence of a register allocation requiring exactly  $|AM_{k^*}|$  registers. As a summary, here are our steps to compute the RS:

- 1. apply Greedy-k on G. The result is a valid killing function  $k^*$ ;

- 2. construct the disjoint value DAG  $DV_{k^*}(G)$ ;

- 3. find a maximal antichain  $AM_{k^*}$  of  $DV_{k^*}(G)$  using Dilworth decomposition [11]. The approximated set of saturating values is the nodes belonging to  $AM_{k^*}$ . The approximated RS is equal to  $RS^*(G) = |AM_{k^*}| \le RS(G)$ .

Figure 8.a shows a saturating killing function  $k^*$  computed by Greedy-k: bold edges mean that each source is killed by its sink. Each killer is labeled by its cost  $\rho$ . Part (b) gives the disjoint value DAG associated with  $k^*$ . The Saturating values are  $\{a, b, c, d, f, j, k\}$ , so the RS is 7.

## 5 Exact Register Saturation Computation

First, if  $|V_{R,t}|$ , the total number of values of type t, is less than or equal to  $\mathcal{R}_t$ , the number of available registers of type t, then we are sure that any schedule cannot require more than  $|V_{R,t}| \leq \mathcal{R}_t$  registers. Otherwise, we must compute the register saturation (RS).

Let  $RN_t^{\sigma}(G)$  denote the register need of register type t given a schedule  $\sigma \in \Sigma(G)$ , which is equal to the maximal number of values of type t simultaneously alive. The RS of a register type t for a DAG G is the maximal register need of type t among all valid schedules of G:

$$RS_t(G) = \max_{\sigma \in \Sigma(G)} RN_t^{\sigma}(G)$$

Below, we give the set of variables and constraints of an exact integer linear programming (intLP) formulation for computing the optimal  $RS_t(G)$ . Our intLP formulation expresses the logical operators ( $\Longrightarrow$ ,  $\lor$ ,  $\Longleftrightarrow$ ) and the max operator (max(x,y)) by introducing extra binary variables. However, expressing these additional operators requires that we bound the domain of the integer variables, as explained below.

## 5.1 Expressing Logical Operators by Integer Programming

In [17], the authors show how to model the disjunctive operator  $\vee$ . Consider the problem:

$$\left\{ \begin{array}{l} \text{maximize (or minimize) } f(x) \\ \text{subject to : } g(x) \geq 0 \ \lor \ h(x) \geq 0 \end{array} \right.$$

By introducing a binary variable  $\alpha \in \{0, 1\}$ , this disjunction is equivalent to:

$$\begin{cases} g(x) \ge \alpha \underline{g} \\ h(x) \ge (1 - \alpha)\underline{h} \end{cases}$$

where  $\underline{g}$  and  $\underline{h}$  are two known non null finite lower bounds for g and h respectively. We deduce the linear constraints of any other logical operator:

- 1.  $g(x) \ge 0 \Longrightarrow h(x) \ge 0$  can be written  $g(x) < 0 \lor h(x) \ge 0$

- 2.  $g(x) \ge 0 \iff h(x) \ge 0$  can be written  $(g(x) \ge 0 \land h(x) \ge 0) \lor (h(x) < 0 \land g(x) < 0)$

Also,

$$z = max(x, y)$$

can be written

$$\left\{ \begin{array}{l} x \geq y \Longrightarrow z = x \\ y \geq x \Longrightarrow z = y \end{array} \right..$$

Thanks to the use of binary variables for expressing logical operators, our intLP formulation of register constraints contains a polynomial number of variables and constraints, *i.e*, it depends only on the number of nodes and edges of the input DAG. Unfortunately, this is not the case of the existing techniques in the literature where the number of variables and constraints is pseudo-polynomial, since this number depends on the total schedule time. The following section presents our intLP formulation of RS computation.

## 5.2 Scheduling Variables

For all operations  $u \in V$ , we define the integer variable  $\sigma_u \ge 0$  that identifies the schedule time for each operation. Note that these schedule variables do not represent the final schedule under resource constraints (that will be computed after our RS pass), they only represent intermediate variables for our intLP formulation. The first linear constraints are those that describe precedence relations (the constraints that ensure the existence of at least one valid schedule), so we write into the intLP system:

$$\forall e = (u, v) \in E : \qquad \sigma_v - \sigma_u \ge \delta(e)$$

In order to bound the domain set of our variables, we define T a worst possible schedule time. We choose T sufficiently large, where for instance  $T = \sum_{e \in E} \delta(e)$  is a suitable worst total schedule time (the extreme case of a sequential schedule, i.e, no ILP). Then, we write the following constraint:

$$\sigma_{\perp} \leq T$$

As a consequence, we deduce for any  $u \in V$ :

- $\sigma_u \geq \sigma_u = LongestPathTo(u)$  is the shortest schedule time;

- $\sigma_u \leq \overline{\sigma_u} = T LongestPathFrom(u)$  is the longest schedule time according to the worst total schedule time T.

#### **5.3** Register Need Constraints

**Interference Graph** The lifetime interval of a value  $u^t$  of type t is (given a schedule  $\sigma$ )

$$LT_{\sigma}(u^{t}) = ]\sigma_{u} + \delta_{w,t}(u), \max_{v \in Cons(u^{t})} (\sigma_{v} + \delta_{r,t}(v))]$$

That is, we assume that a value written at instant c in a register is available one step later. Thus, if an operation u reads from a register r at instant c while another operation v is writing to the r at the same time, u does not get v's result, but rather gets the value previously stored in r. Note that these semantics are explicitly chosen and encoded in the definition of  $LT_{\sigma}(u^t)$ , and are not a limitation of the model.

We define for each value  $u^t$  the variable  $k_{u^t} \ge 0$  which computes its killing date (the last time that  $u^t$  is read). Since our variable domains are bounded (assuming a finite T), we know that  $k_{u^t}$  is bounded by the two following finite schedule times:

$$\forall t \in \mathcal{T}, \ \forall u^t \in V_{R,t}: \qquad \underline{k_{u^t}} < k_{u^t} \le \overline{k_{u^t}}$$

where

- $k_{u^t} = \sigma_u + \delta_{w,t}(u)$  is the first possible definition date of  $u^t$ ;

- $\overline{k_{u^t}} = \max_{v \in Cons(u^t)} \left( \overline{\sigma_v} + \delta_{r,t}(v) \right)$  is the latest possible killing date of  $u^t$ .

We use the linear constraints of the max operator to compute  $k_{u^t}$  as explained in Section 5.1. We write into the intLP system:

$$\forall u^t \in V_{R,t}: \qquad k_{u^t} = \max_{v \in Cons(u^t)} (\sigma_v + \delta_{r,t}(v))$$

Now, we can consider  $H_t$  the undirected interference graph of G for the register type t. For any pair of distinct values  $u^t, v^t \in V_{R,t}$ , we define a binary variable  $s^t_{u,v} \in \{0,1\}$  such that it is set to 1 if the two lifetimes intervals of type t interfere:  $\forall t \in \mathcal{T}, \ \forall \ \text{couple} \ u^t, v^t \in V_{R,t}$ :

$$s_{u,v}^t = \left\{ \begin{array}{ll} 1 & \text{if } LT_\sigma(u^t) \cap LT_\sigma(v^t) \neq \phi \\ 0 & \text{otherwise} \end{array} \right.$$

The number of variables  $s_{u,v}^t$  is the number of combinations of two values among  $|V_{R,t}|$ , i.e.,  $(|V_{R,t}| \times (|V_{R,t}| - 1))/2$ .  $LT_{\sigma}(u^t) \cap LT_{\sigma}(v^t) = \phi$  means that one of the two lifetime intervals is "before" the other, i.e.,  $(LT_{\sigma}(u^t) \prec LT_{\sigma}(v^t)) \vee (LT_{\sigma}(v^t) \prec LT_{\sigma}(u^t))$ , where  $\prec$  denotes the "before" relation in interval algebra. Then, we have to express the following constraints:

$$s_{u,v}^t = 1 \Longleftrightarrow \neg \left( LT_{\sigma}(u^t) \prec LT_{\sigma}(v^t) \lor LT_{\sigma}(v^t) \prec LT_{\sigma}(u^t) \right)$$

where  $LT_{\sigma}(u^t) \prec LT_{\sigma}(v^t)$  iff  $k_{u^t} \leq \sigma_v + \delta_{w,t}(v)$ . The negation of this constraint is  $k_{u^t} > \sigma_v + \delta_{w,t}(v)$ , i.e.,  $k_{u^t} - \sigma_v - \delta_{w,t}(v) - 1 \geq 0$ . Since  $s_{u,v}^t \in \{0,1\}$ , these variables are constrained as follows:

$$s_{u,v}^t \ge 1 \Longleftrightarrow \begin{cases} k_{u^t} - \sigma_v - \delta_{w,t}(v) - 1 \ge 0 \\ k_{v^t} - \sigma_u - \delta_{w,t}(u) - 1 \ge 0 \end{cases}$$

Given three logical expressions (P,Q,S),  $(P \iff (Q \land S))$  is equivalent to the expression  $(P \land Q \land S) \lor (\neg P \land \neg Q) \lor (\neg P \land \neg S)$ . We write these two disjunctions with linear constraints by introducing binary variables [30]) and by computing the finite lower bounds of the linear functions.

Maximal Clique in the Interference Graph The maximum number of values of type t simultaneously alive corresponds to a maximal clique in  $H_t = (V_{R,t}, \mathcal{E}_t)$ , where  $(u^t, v^t) \in \mathcal{E}_t$  iff their lifetime intervals interfere  $(s^t_{u,v} = 1)$ . For simplicity, rather than considering the interference graph itself, we prefer to consider its complementary graph  $H'_t = (V_{R,t}, \mathcal{E}'_t)$  where  $(u^t, v^t) \in \mathcal{E}'_t$  iff their lifetime intervals do *not* interfere  $(s^t_{u,v} = 0)$ . Then, the maximum number of values of type t simultaneously alive corresponds to a maximal independent set in  $H'_t$ .

To write the constraints that describe independent sets (IS), we define a binary variable  $x_{u^t} \in \{0,1\}$  for each value  $x_{u^t} \in V_{R,t}$  such that  $x_{u^t} = 1$  if  $u^t$  belongs to some IS of  $H'_t$ . We express in the model the following linear constraints:

$$\forall x_{u^t}, x_{v^t} \in V_{R,t}: \quad s_{u,v}^t = 0 \Longrightarrow x_{u^t} + x_{v^t} \le 1$$

This equations means that if two nodes u and v are connected in H', then one and only one of them may belong to a given IS.

## 5.4 Linear Objective Function and General Remarks

The register requirement of type t is a maximal IS in  $H'_t$ , i.e., the maximal  $\sum_{u^t \in V_{R,t}} x_{u^t}$ . Thus, the register saturation of type t is computed by:

$$\text{Maximize } \sum_{u^t \in V_{R,t}} x_{u^t}$$

The total number of integer variables in the intLP formulation is bounded by  $\mathcal{O}(|V|^2)$ , and the total number of constraints is at most  $\mathcal{O}(|E| + |V|^2)$ . Note that our intLP formulation may be optimized by considering that:

- an edge e = (u, v) in the initial DAG is redundant for the scheduling constraints and can be safely ignored if  $lp(u, v) > \delta(e)$  where lp(u, v) denotes the longest path from u to v (with the condition that this edge doesn't belong to this longest path);

- two values  $(u^t, v^t) \in V_{R,t}$  can never be simultaneously alive iff for all the possible schedules, one value is always defined after the killing date of the other. This is the case if any of the two following conditions is satisfied:

$$\forall v' \in Cons(v^t): \quad lp(v', u) \ge \delta_r(v') - \delta_w(u)$$

$$\forall u' \in Cons(u^t): \quad lp(u', v) \ge \delta_r(u') - \delta_w(v)$$

The next section explores the problem of reducing RS if it exceeds the number of available registers.

## 6 The Complexity of Register Saturation Reduction

In the case where the register saturation  $RS_t(G)$  exceeds the number of available registers  $\mathcal{R}_t$  of the type t, then we must add extra serial edges into the DAG G to reduce  $RS_t(G)$  below this limit. The added edges must save ILP as much as possible by taking care of the critical path. We note by  $\overline{E}$  the set of extra edges that we add to G to build a new extended DAG, namely  $\overline{G} = G \setminus^{\overline{E}}$ , such that  $RS_t(\overline{G}) \leq \mathcal{R}_t$ . We want to first solve the formal problem stated below.

**Definition 2 (ReduceRS Problem)** Let  $G = (V, E, \delta)$  be a DAG. Let  $\mathcal{R}_t$  and  $\mathcal{P}$  be two positive integers. Does there exist an extended DDG  $\overline{G} = G \setminus^{\overline{E}}$  of G such that:

$$RS_t(\overline{G}) \leq \mathcal{R}_t$$

and

$$CriticalPath(\overline{G}) \leq \mathcal{P}$$

Note that an extended DDG may contain a cycle (as we will see later), while an extended DAG is restricted to stay a DAG.

**Theorem 4** The ReduceRS problem is NP-hard.

#### **Proof:**

We prove that ReduceRS problem reduces from the problem of scheduling under register constraints (SRC). Let us start by defining the latter problem. For the sake of clarity, we assume that the considered register type t is implicit (we do not include t in our notations inside this proof).

**Definition 3 (SRC problem)** Let  $G = (V, E, \delta)$  be a DAG,  $\mathcal{R}$  be a positive integer, and  $\mathcal{P}$  be a length. Does there exist a valid schedule  $\sigma \in \Sigma(G)$  such that:

$$RN^{\sigma}(G) \leq \mathcal{R}$$

and

total schedule time

$$< P$$

The SRC problem has been proven NP-hard in [13]. Now we prove the equivalence of ReduceRS and SRC in terms of computational complexity.

#### 1. ReduceRS $\Longrightarrow$ SRC

Let  $\overline{G}$  be a solution for the ReduceRS problem. Then trivially, any "as soon as possible" schedule  $\sigma \in \Sigma(\overline{G})$  is a solution for SRC.

## 2. SRC $\Longrightarrow$ ReduceRS

Let  $\sigma$  be a solution for SRC, *i.e.*,  $RN^{\sigma}(G) \leq \mathcal{R}$  with a total schedule time of  $\leq \mathcal{P}$ . We build an extended DDG  $\overline{G}$  by adding serial edges to impose the same precedence relations as defined by  $\sigma$  on the value lifetimes of any schedule of  $\overline{G}$ . Then,  $\forall u, v \in V_R | LT_{\sigma}(u) \prec LT_{\sigma}(v)$  we add the following edges:

• If  $v \in Cons(u)$ , add serial edges from the readers of u (except v) to v; the set of added edges is:

$$\{e = (u', v) | u' \in Cons(u) - \{v\}\}$$

• Otherwise, add serial edges from all u's readers to v; the set of added edges is:

$$\{e = (u', v) | u' \in Cons(u)\}$$

The latency of these added edges has to be assigned based on the target architecture. There are two cases:

- 1. in the case of superscalar codes, there are sequential code semantics. So, the latency of each added edge is set to 1;

- 2. in the case of VLIW or EPIC/IA64, there are reading and writing offsets. Thus, for each added edge e = (u', v), the latency is set to  $\delta(e) = \delta_r(u') \delta_w(v)$ .

Indeed, the added edges and the chosen latencies force the following assertion:

$$LT_{\sigma}(u) \prec LT_{\sigma}(v) \Longrightarrow \forall \sigma' \in \Sigma(\overline{G}): LT_{\sigma'}(u) \prec LT_{\sigma'}(v)$$

Then, for all values not simultaneously alive according to  $\sigma$ , there is no schedule  $\sigma'$  of  $\overline{G}$  that makes them simultaneously alive. Formally, :

$$\neg \Big(\exists u, v \in V_R, \ LT_{\sigma}(u) \prec LT_{\sigma}(v), \ \exists \sigma' \in \Sigma(\overline{G}) | \ LT_{\sigma'}(u) \cap LT_{\sigma'}(v) \neq \phi\Big)$$

In other words, we ensure that any schedule of  $\overline{G}$  will guarantee the precedence relations between the lifetime intervals of G according  $\sigma$ . Consequently, any schedule  $\sigma'$  of  $\overline{G}$  cannot require more than the register need of  $\sigma$  and

$$RS(\overline{G}) = RN^{\sigma}(G) \le \mathcal{R}$$

A solution for the SRC problem may create a cycle in the solution of ReduceRS. We are sure that if any cycle is introduced in  $\overline{G}$ , then it must be non-positive because there exists at least the valid schedule  $\sigma \in \Sigma(\overline{G})$ . Consequently, a solution of the ReduceRS problem may produce a cyclic DDG. We will see later how to eliminate these solutions.

With regard to the critical path of  $\overline{G}$ , the introduced serial edges ensure that at least  $\sigma \in \Sigma(\overline{G})$ . Since there exists such a schedule with a total time  $\leq \mathcal{P}$ , the critical path of  $\overline{G}$  cannot be longer than  $\mathcal{P}$ .

┙

The next section provides an algorithmic heuristics that tries to reduce RS below a limit. This section follows the ideas and notations used in Section 4.

## 7 An Algorithmic Heuristics for Reducing the Register Saturation

For clarity and without loss of generality, let us focus on only one register type  $^2$ . Then, our notations become  $V_R$  for the set of values of the implicit type we consider,  $E_R$  for the set of flow edges through a register of that type,  $\delta_r$  and  $\delta_w$  for reading/writing delays, and  $RN^{\sigma}(G)$  for the register need of the type we consider. Also, we use the notation u for both the operation u and the value of the considered type it produces.

In this section we build an extended DAG  $\overline{G} = G \setminus^{\overline{E}}$  such that the RS is limited by a strictly positive integer (number of available registers) with the respect of the critical path. Let  $\mathcal{R}$  be this limit. Then:

$$\forall \sigma \in \Sigma(\overline{G}): RN^{\sigma}(\overline{G}) \leq RS(\overline{G}) \leq \mathcal{R}$$

<sup>&</sup>lt;sup>2</sup>If more than one register type exists, we apply our algorithm on each type.

Figure 9. Value Serialization

This section presents a heuristics that adds serial edges to prevent some saturating values in  $AM_k$  (according to a saturating killing function k) from being simultaneously alive for any schedule. Also, we take care not to increase the critical path, if possible.

Serializing two values  $u, v \in V_R$  means that the killing of u must always be carried out before the definition of v, or *vice-versa*, as illustrated by Figure 9. A value serialization  $u \to v$  for two values  $u, v \in V_R$  is defined by:

- if  $v \in pkill_G(u)$  then add the serial edges  $\{e = (v', v)|v' \in pkill_G(u) \{v\}\}$ . Textually, this means that if v is a potential killer of u, the value serialization  $u \to v$  means to add a serial edge from any potential killer of u (except v) to v itself, see Figure 9.c.

- otherwise add the serial edges  $\{e = (u', v)|u' \in pkill_G(u) \land \neg(v < u')\}$  Textually, this means that if v is not a potential killer of u, the value serialization  $u \to v$  means to add a serial edge from any potential killer of u to v itself, see Figure 9.d.

The latency of these added edges has to be chosen depending on the target codes. We have two cases:

- 1. in the case of superscalar codes, the semantics is sequential. So, the latency of each added edge is set to 1;

- 2. in the case of VLIW or EPIC/IA64, there exist reading and writing offsets<sup>3</sup>. Thus, for each added edge e = (u', v), the latency is set to  $\delta(e) = \delta_r(u') \delta_w(v)$ .

In order to not violate the DAG property (we must not introduce a cycle), some serializations must be filtered out. The condition for applying  $u \to v$  is that  $\forall v' \in pkill_G(u) : \neg(v < v')$ . We chose the best serialization within the set of all the possible serializations by using a cost function  $\omega(u \to v) = (\omega_1, \omega_2)$ , such that:

- $\omega_1 = \mu_1 \mu_2$  tries to predict how much RS would be reduced (in the best case) if we carry out this value serialization, where

- $-\mu_1$  is the number of saturating values serialized after u if we carry out this value serialization  $u \to v$ ;

- $-\mu_2$  is the predicted number of u's descendant values that can become simultaneously alive with u;

- $\omega_2$  is the predicted increase in the critical path.

Our heuristics is described in Algorithm 3. It iterates value serializations within the saturating values until we get the limit  $\mathcal{R}$  or until no more serializations are possible (or none is expected to reduce the RS). One can check that if there is no possible value serialization in the original DAG, our algorithm exits at the first iteration of the outer while-loop. If it succeeds, then any schedule of  $\overline{G}$  needs at most  $\mathcal{R}$  registers. If not, it still decreases the original RS, and thus limits the register need. Introducing and minimizing the spill code is another NP-complete problem studied in [3, 4, 9, 10, 27] and is not addressed in this article.

Now, we explain how to compute the prediction parameters  $\mu_1, \mu_2, \omega_2$ . We note  $\overline{G_i}$  the extended DAG of step  $i, k_i$  its saturating function, and  $AM_{k_i}$  its saturating values and  $\downarrow_{R_i} u$  the descendant values of u in  $\overline{G_i}$ :

<sup>&</sup>lt;sup>3</sup>On EPIC/IA64 architectures, a writer and a reader can be scheduled at the same instruction group, so the writing delay is statically considered as zero.

- 1.  $(u \to v)$  ensures that  $k_{i+1}(u) < v$  in  $\overline{G_{i+1}}$ . According to Lemma 2,  $\mu_1 = |\downarrow_{R_i} v \cap AM_{k_i}|$  is the number of saturating values in  $\overline{G_i}$  which cannot be simultaneously alive with u in  $\overline{G_{i+1}}$ ;

- 2. new saturating values could be introduced into  $\overline{G_{i+1}}$ : if  $v \in pkill_{\overline{G_i}}(u)$ , we force  $k_{i+1}(u) = v$ . According to Lemma 2,

$$\mu_2 = \left| \left( \bigcup_{v' \in pkill_{\overline{G_i}}(u)} \downarrow_{R_i} v' \right) - \downarrow_{R_i} v \right|$$

is the number of values which could be simultaneously alive with u in  $\overline{G_{i+1}}$ .  $\mu_2 = 0$  otherwise;

3. if we carry out  $(u \to v)$  in  $\overline{G_i}$ , the introduced serial edges could enlarge the critical path. Let  $lp_i(v', v)$  be the longest path going from v' to v in  $\overline{G_i}$ . The new longest path in  $\overline{G_{i+1}}$  going through the serialized nodes is:

$$\max_{\substack{\text{introduced } e = (v', v) \\ \delta(e) > lp_i(v', v)}} lp_i(\top, v') + lp_i(v, \bot) + \delta(e)$$

If this path is greater than the critical path in  $\overline{G_i}$ , then  $\omega_2$  is the difference between them, 0 otherwise.

## **Algorithm 3** Value Serialization Heuristics

```

Require: a DAG G=(V,E,\delta) and a strictly positive integer \mathcal{R} \overline{G}:=G compute AM_k, saturating values of \overline{G}; while |AM_k| > \mathcal{R} do construct the set U_k of all admissible serializations between saturating values in AM_k with their costs (\omega_1,\omega_2); if \nexists(u \to v) \in U | \omega_1(u \to v) > 0 then \{\text{no more possible RS reduction}\} exit; end if X := \{(u \to v) \in U | \omega_2(u \to v) = 0\} \{\text{the set of value serializations that do not increase the critical path}\} if X \neq \phi then choose a value serialization (u \to v) in X with the minimum cost \mathcal{R} - \omega_1; else choose a value serialization (u \to v) in X with the minimum cost \omega_2; end if carry out the serialization (u \to v) in \overline{G}; compute the new saturating values AM_k of \overline{G}; end while ensure potential killing operations property \{\text{check longest paths between pkill operations}\}

```

At the end of the algorithm, we apply a general check step to ensure the potential killing property proved in Lemma 1 (page 6) for the original DAG. Lemma 1 proves that the operations which do not belong to  $pkill_G(u)$  cannot kill the value u. After adding the serial edges that build  $\overline{G}$ , we may violate this assertion because we introduce some edges with negative latencies. If this assertion is not verified, the computed RS may be incorrect. To overcome this problem, we must guarantee the following assertion:  $\forall u \in V_R, \ \forall v' \in Cons(u) - pkill_{\overline{G}}(u)$ :

$$\exists v \in pkill_{\overline{G}}(u)|v' < v \text{ in } \overline{G} \Longrightarrow lp_{\overline{G}}(v',v) > \delta_r(v') - \delta_r(v)$$

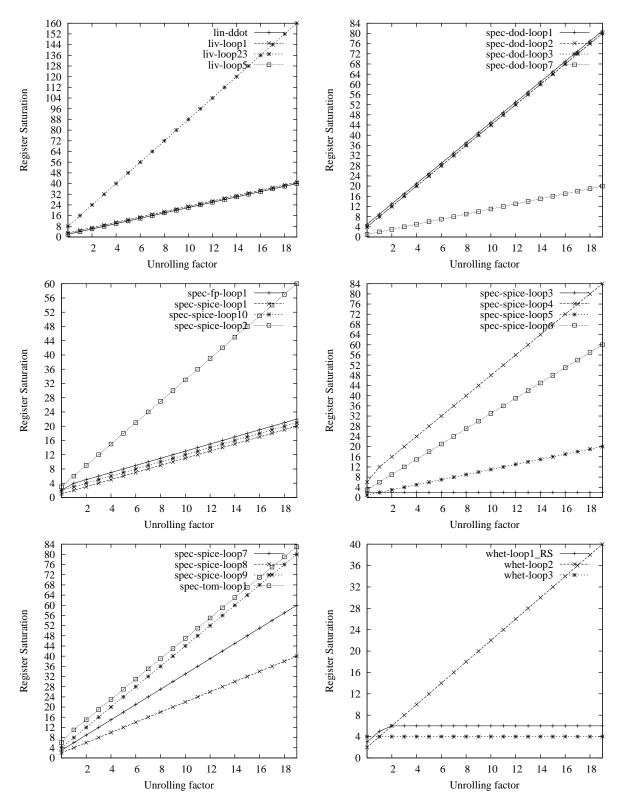

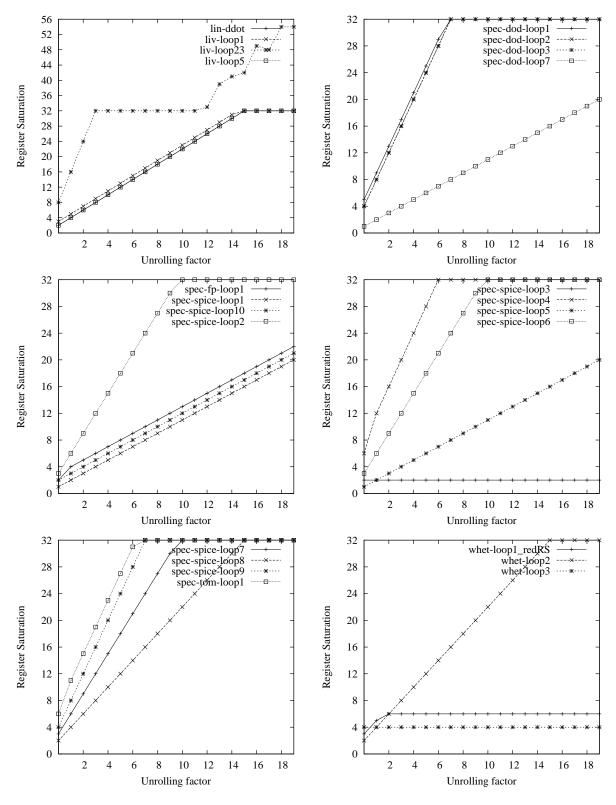

$$\tag{9}$$