Abstract

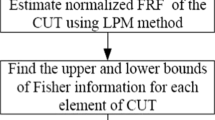

A methodology for diagnosing and characterizing multiple faults in analog circuits, and results from applying this methodology to a real circuit is presented. Our method is a novel combination of a Simulation Before Test (SBT) and Interpolation After Test (IAT) methodology. Our method uses the classical SBT concept of a fault dictionary database constructed before test. It also uses a method of IAT that consists in using the measurements to guide an interpolation algorithm to effectively increase the local resolution of the fault dictionary database and thereby yield the most likely test parameter value. Our method’s underlying principle is to characterize the fault-free and faulty circuit cases by their impulse responses obtained by simulation and subsequently stored in a fault dictionary database. The method uses the technique of Lagrange interpolation to resolve the faults between the fault dictionary database entries and the actual measurements. Our experimental results reveal that the method is effective for characterizing faults when the simulations match the measurements sufficiently. Consequently, the method’s effectiveness depends highly on the quality of the models used to build the dictionary as well as on the accuracy of the measurements.

Similar content being viewed by others

References

J.W. Bandler and A.E. Salama, “Fault Diagnosis of Analog Circuits,” Proc. IEEE, vol. 73, no. 8, pp. 1279–1286, 1985.

S. Cherubal and A. Chatterjee, “Parametric Fault Diagnosis for Analog Systems Using Functional Mapping,” Proc. Design and Test in Europe (Date99), March 1999, pp. 195–200.

H.K. Gummel and H.C. Poon, “An Integral Charge Control Model of Bipolar Transistors,” Bell Syst. Tech., vol. 49, pp. 827–852, May 1970.

HP EEsof Design Solutions, IC-CAP 5.0, Statistical Analysis, Hewlett Packard, June, 1997.

S. Lesage, “Test Electrique et Caracterisation de Fautes Parametriques Dans un Circuit Analogique,” These de Doctorat de l’Universite Bordeaux1, 13 Janvier 1998.

Y. Maidon, B.W. Jervis, N. Dutton, and S. Lesage, “Diagnosis of Multifaults in Analog Circuit Using Multilayer Perceptrons,” IEE Proc. Circuits, Devices and Systems, vol. 144, no. 3, pp. 149–154, 1997.

Y. Maidon, S. Lesage, B.W. Jervis, S. Ogg, and J.P. Dom, “Comparison between Neural Network and Arithmetic Lagrange Interpolation Methods of Analog Circuits Testing,” in IMSTW’96 IEEE Proceedings, Quebec, Canada, May 15–18, 1996.

D.W. Marquardt, “An Algorithm for Least Squares Estimation of Non-Linear Parameters,” Journal SIAM, vol. 11, pp. 431–441, 1963.

R. Menozzi and A. Piazzi, “On the Use of Genetic Algorithm for Millimeter-Wave FET Modelling,” in Proceedings of ESDERC’96, Bologna, Italy, Sept. 1996, pp. 663–666.

S. Somayajulam, E. Sanchez-Sinencio, and J.P. de Gyvez, “Power Supply Ramping and Current Measurement Based Technique for Analog Fault Diagnosis,” in Proc. IEEE VLSI Test Symposium, 1994, pp. 234–239.

R. Voorakaranam, et al., “Hierarchical Specification-Driven Analog Fault Modelling for Efficient Simulation and Diagnosis,” in Proc. International Test Conference, 1997, pp. 903–912.

Z. You, E. Sanzhez-Sinencio, and J.P. de Gyvez, “Analog System-Level Fault Diagnosis Based on a Symbolic Method in the Frequency Domain,” IEEE Trans. on Instrumentation and Measurement, vol. 44, no. 1, pp. 28–35, 1995.

T. Zimmer, J.B. Duluc, and N. Lewis, “Method for BJT Transit Time Evaluation,” Electronics Letters, vol. 34, no. 20, 1998.

T. Zimmer, S. Limtouch, J.B. Duluc, and all, “Process Reliability Assessment Based on Spice Parameter Analysis,” in ESREF’95, Arcachon, France, 1995, pp. 73–75.

Author information

Authors and Affiliations

Corresponding author

Additional information

Yvan Maidon was born in Bordeaux, France. He received the M.Sc degree in (electronics) applied physics from the University of Bordeaux, in 1980. He is currently Head of the Department for Applied Sciences in Electrical and Electronic Engineering at the University of Bordeaux 1. His special research interests include failure analysis and relaibility of analog circuits. He has also developed original BICS for mixed circuits and SoC testing.

Thomas Zimmer is currently Professor at the University of Bordeaux 1. He received the M.Sc. degree in physics from the University of Würzburg, Germany, in 1989 and the Ph.D. degree in electronics from the University of Bordeaux 1, France, in 1992. His research interests include characterization and modeling of high frequency bipolar devices. He has authored and co-authored about 70 scientific and technical publications including several book chapters. He is also co-founder of the start-up company XMOD.

André Ivanov is Professor in the Department of Electrical and Computer Engineering, at the University of British Columbia. Prior to joining UBC in 1989, he received his B.Eng. (Hon.), M. Eng., and Ph.D. degrees in Electrical Engineering from McGill University. In 1995–96, he spent a sabbatical leave at PMC-Sierra, Vancouver, BC. He has held invited Professor positions at the University of Montpellier II, the University of Bordeaux I, and Edith Cowan University, in Perth, Australia. His primary research interests lie in the area of integrated circuit testing, design for testability and built-in self-test, for digital, analog and mixed-signal circuits, and systems on a chip (SoCs). He has published widely in these areas and holds several patents in IC design and test. Besides testing, Ivanov has interests in the design and design methodologies of large and complex integrated circuits and SoCs. Ivanov has served and continues to serve on numerous national and international steering, program, and/or organization committees in various capacities. Recently, he was the Program Chair of the 2002 VLSI Test Symposium (VTS 02) and the General Chair for VTS 03 and VTS 04. In 2001, Ivanov co-founded Vector 12, a semiconductor IP company. He has published over 100 papers in conference and journals and holds 4 US patents. Ivanov serves on the Editorial Board of the IEEE Design and Test Magazine, and Kluwer’s Journal of Electronic Testing: Theory and Applications. Ivanov is currently the Chair of the IEEE Computer Society’s Test Technology Technical Council (TTTC). He is a Golden Core Member of the IEEE Computer Society, a Senior Member of the IEEE, a Fellow of the British Columbia Advanced Systems Institute and a Professional Engineer of British Columbia.

Rights and permissions

About this article

Cite this article

Maidon, Y., Zimmer, T. & Ivanov, A. An Analog Circuit Fault Characterization Methodology. J Electron Test 21, 127–134 (2005). https://doi.org/10.1007/s10836-005-6142-5

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/s10836-005-6142-5