Abstract

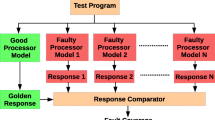

This paper describes a self test program design technique for embedded DSP cores. The method requires minimal knowledge of the core’s internals and minimal insertion of external LFSR hardware, without scan insertions. The test program consists of a small set of instructions which operate iteratively on pseudorandom data generated by the LFSRs to fully test the DSP core components. The method uses instruction-based test metrics and a program template as a blueprint to generate the test program. The self test scheme has been successfully applied on an industrial-strength DSP core and the results compare favorably to other methods using ATPG and pseudorandom BIST.

Similar content being viewed by others

References

M. Abramovici, M. A. Breuer, A. D. Friedman., Digital Systems Testing and Testable Design, New York, Computer Science Press, 1990.

K. Batcher and C. Papachristou, “Instruction Randomization Self Test for Processor Cores,” IEEE VLSI Test Symposium, pp. 34–40,1999.

C. Papachristou and J. Carletta, “Test Synthesis in the Behavioral Domain,” Internat. Test Conf. (ITC-95), 1995.

S. Chiusano, F. Corno, and P. Prinetto, “RT-Level TPG Exploiting High-Level Synthesis Information,” IEEE VLSI Test Symposium, pp. 341–346, 1999.

L. Chen and S. Dey, “DEFUSE: a Deterministic Functional Self-Test Methodology for Processors,” IEEE VLSI Test Symposium, pp. 255–262, 2000.

F. Corno, P. Prinetto, R. Sonza, and Matteo, “Testability Analysis and ATPG on Behavioral RT-Level VHDL,” International Test Conference (ITC-97), pp. 753–759, 1997.

T. M. Cover, and J. A. Thomas, Elements of Information Theory, New York, Wiley-Interscience, 1991.

J. P. Hayes, and E. J. McCluskey, “Testability Considerations in Microprocessor-Based Design,” IEEE Computer, pp. 17–24, 1980.

T.M. Kemp, R.M. Monotoye, J.D. Harper, J.D. Palmer, and D.J. Auerbach, “A Decompression Core for PowerPC,” IBM Journal of Research and Development, Vol. 42, No. 5/6, 1998.

N. Kranitis, D. Gizopoulos, A. Paschalis, and Y. Zorian, “Instruction-Based Self-Testing of Processor Cores,” VLSI Test Symposium (VTS-2002), 2002.

N. Kranitis, G. Xenoulis, D. Gizopoulos, A. Paschalis and Y. Zorian, “Low-Cost Software-Based Self Testing of RISC Processor Cores,” Design Automation and Test in Europe (DATE-03),2003.

W.-C. Lai and K.-T. Cheng, “Instruction-Level DFT for Testing Processor and IP Cores in System-on-a-Chip,” Design Automation Conference (DAC-2001), pp. 59–64, 2001.

W.-C. Lai, A. Krstic, and K.-T. Cheng “Test Program Synthesis for Path Delay Faults in Microprocessor Cores,” International Test Conference (ITC-2000), pp. 1080–1089, 2000.

R. F. Martin, Private Communication.

K. Ockunzzi and C. Papachristou, “Test Strategies for BIST at the Algorithmic and Register-Transfer Levels,” Design Automation Conf. (DAC-2001), 2001.

D. Patterson and J. Hennessy, Computer Architecture: A Quantitative Approach, Morgan-Kaufmann Publishers, San Francisco,2003.

P. Parvathala, K. Maneparambil, and W. Lindsay, “FRITS—A Microprocessor Functional BIST Method,” International Test Conference (ITC-2002), pp. 590–598, 2002.

C.P. Ravikumar, G.S.Saund, and N.Agrawal, “A STAFAN-Like Functional Testability Measure for Register-Level Circuits,” IEEE Fourth Asian Test Symposium, pp. 192–198, 1995.

J. Shen and J. Abraham, “Native Mode Functional Test Generation for Processors with Applications to Self Test and Design Validation,” Intern. Test Conf. (ITC-1998), 1998.

W. Zao and C. Papachristou, “Testing DSP Cores Based on Self-Test Programs,” Design Automation and Test in Europe (DATE-1998), pp. 166–172, 1998.

Author information

Authors and Affiliations

Corresponding author

Additional information

Editor: C.E. Stroud

Hani Rizk received his B.S./M.S. in Computer Engineering at Case Western Reserve University in 2002. He currently works at Intel Corporation in Oregon.

Chris Papachristou has a Ph.D. from Johns Hopkins University. He is currently a Professor of Computer Engineering at Case Western Reserve University. His research interests are in Embedded Systems, CAD, Adaptive Hardware, Testing and Fault Tolerance.

Francis G. Wolff has a Ph.D. from Case Western Reserve University in Computer Engineering and is also a researcher in the area of computer engineering.

Rights and permissions

About this article

Cite this article

Rizk, H., Papachristou, C. & Wolff, F. A Self Test Program Design Technique for Embedded DSP Cores. J Electron Test 22, 71–87 (2006). https://doi.org/10.1007/s10836-006-5549-y

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/s10836-006-5549-y