Abstract

The push to embed reliable and low-power memories architectures into modern systems-on-chip is driving the EDA community to develop new design techniques and circuit solutions that can concurrently optimize aging effects due to Negative Bias Temperature Instability (NBTI), and static power consumption due to leakage mechanisms. While recent works have shown how conventional leakage optimization techniques can help mitigate NBTI-induced aging effects on cache memories, in this paper we focus specifically on scratchpad memory (SPM) and present novel software approaches as a means of alleviating the NBTI-induced aging effects. In particular, we demonstrate how intelligent software directed data allocation strategies can extend the lifetime of partitioned SPMs by means of distributing the idleness across the memory sub-banks.

Similar content being viewed by others

Notes

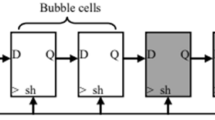

The granularity of the power-managed units can range from one cell to one word, or groups of adjacent words.

This term is null for both the vanilla and the power-aware SPM architectures.

References

Alam M (2008) Reliability- and process-variation aware design of integrated circuits. Microelectronics Reliability 48(8):1114–1122

Alam M, Kufluoglu H, Varghese D, Mahapatra S (2007) A comprehensive model for pmos nbti degradation: recent progress. Microelectronics Reliability 47(6):853–862

ARM (2011) Cortex-A9 MPCore technical reference manual. http://infocenter.arm.com/. Accessed Mar 2012

Boning D, Nassif S (1999) Design of high performance microprocessor circuits, In: Models of process variations in device and interconnect, chap 6. IEEE Press

Borkar S (2005) Designing reliable systems from unreliable components: the challenges of transistor variability and degradation. IEEE Micro 25(6):10–16

Calimera A, Loghi M, Macii E, Poncino M (2010a) Aging effects of leakage optimizations for caches. In: Proceedings of the Great Lakes symposium on VLSI, pp 95–98

Calimera A, Loghi M, Macii E, Poncino M (2010b) Dynamic indexing: concurrent leakage and aging optimization for caches. In: Proceedings of the ACM/IEEE international symposium on low power electronics and design, pp 343–348

Calimera A, Macii E, Poncino M (2010c) Analysis of nbti-induced snm degradation in power-gated sram cells. In: Proceedings of the IEEE international symposium on circuits and systems, pp 785–788

Calimera A, Loghi M, Macii E, Poncino M (2011) Partitioned cache architectures for reduced nbti-induced aging. In: Proceedings of the conference on design, automation and test in Europe, pp 1 –6

Chen G, Li M, Ang C, Zheng J, Kwong D (2002) Dynamic nbti of p-mos transistors and its impact on mosfet scaling. IEEE Electron Device Lett 23(12):734–736

Freescale (2011) Freescale low-power QE family processor. http://www.freescale.com/lowpower. Accessed Mar 2012

Huard V, Parthasarathy C, Guerin C, Valentin T, Pion E, Planes MMN, Camus L (2008) Nbti degradation: from transistor to SRAM arrays. In: Proceedings of the IEEE annual international reliability physics symposium, pp 289–300

Kandemir M, Irwin M, Chen G, Kolcu I (2004) Banked scratch-pad memory management for reducing leakage energy consumption. In: Proceedings of the ACM/IEEE international conference on computer-aided design, pp 120–124

Kang K, Alam M, Roy K (2007a) Characterization of NBTI induced temporal performance degradation in nano-scale SRAM array using IDDQ. In: Proceedings of the IEEE international test conference, pp 1–10

Kang K, Kufluoglu H, Roy K, Alam MA (2007b) Impact of negative-bias temperature instability in nanoscale sram array: modeling and analysis. IEEE Trans Comput-Aided Des Integr Circuits Syst 26(10):1770–1781

Kaxiras S, Hu Z, Martonosi M (2001) Cache decay: exploiting generational behavior to reduce cache leakage power. In: Proceedings of the annual international symposium on computer architecture, pp 240–251

Kim N, Flautner K, Blaauw D, Mudge T (2004) Circuit and microarchitectural techniques for reducing cache leakage power. IEEE Trans Very Large Scale Integr (VLSI) Syst 12(2):167–184

Kumar S, Kim K, Sapatnekar S (2006) Impact of NBTI on SRAM read stability and design for reliability. In: Proceedings of the IEEE international symposium on quality electronic design, pp 213–218

Loghi M, Golubeva O, Macii E, Poncino M (2010) Architectural leakage power minimization of scratchpad memories by application-driven subbanking. IEEE Trans Comput 59(7):891–904

Nii K, Makino H, Tujihashi Y, Morishima C, Hayakawa Y, Nunogami H, Arakawa T, Hamano H (1998) A low power sram using auto-backgate-controlled mt-cmos. In: Proceedings of the international symposium on low power electronics and design, pp 293–298

Powell M, Yang SH, Falsafi B, Roy K, Vijaykumar T (2000) Gated-Vdd: a circuit technique to reduce leakage in deep-submicron cache memories. In: Proceedings of the 2000 international symposium on low power electronics and design, pp 90–95

Ricketts A, Singh J, Ramakrishnan K, Vijaykrishnan N, Pradhan DK (2010) Investigating the impact of NBTI on different power saving cache strategies. In: Proceedings of the conference on design, automation and test in Europe, pp 592–597

Seevinck E, List F, Lohstroh J (1987) Static-noise margin analysis of mos sram cells. IEEE J Solid-State Circuits 22(5):748–754

STMicroelectronics (2011) Stmicroelectronics cortex-m3 cpu. http://www.st.com/mcu/inchtml-pages-stm32.html. Accessed Mar 2012

Su C, Despain A (1995) Cache designs for energy efficiency. In: Proceedings of the Hawaii international conference on system sciences, pp 306–315

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: F. L. Vargas

Rights and permissions

About this article

Cite this article

Ferri, C., Papagiannopoulou, D., Bahar, R.I. et al. NBTI-Aware Data Allocation Strategies for Scratchpad Based Embedded Systems. J Electron Test 28, 349–363 (2012). https://doi.org/10.1007/s10836-012-5295-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-012-5295-2