Abstract

This paper describes the architecture and principles of operation of sigma-delta ( ΣΔ) time-to-digital converters (TDC) for high-speed I/O interface circuit test applications. In particular, we describe multi-bit ΣΔ TDC architectures; they offer good accuracy with short testing time. However, mismatches among delay cells in delay lines degrade their linearity. Here we propose two methods to improve the overall TDC linearity: a data-weighted-average (DWA) algorithm, and a self-calibration method that measures delay values using a ring oscillator circuit. Our Matlab simulation results demonstrate the effectiveness of these approaches.

Similar content being viewed by others

References

Bushnell ML, Agrawal VD (2000) Essentials of electronic testing for digital, memory & mixed-signal VLSI circuits. Springer, New York

Cao Y, Leroux P, Cock WD, Steyaert M (2011) A 1.7mW 11b 1-1-1 MASH ΔΣ time-to-digital converter. In: IEEE international solid-state circuits conference, San Francisco

Geerts Y, Steyaert M, Sansen W (2002) Design of multi-bit deltasigma A/D converters. Springer, New York

Hirabayashi D, Arakawa Y, Kawauchi S, Ishii M, Uemori S, Sato K, Kobayashi H, Niitsu K, Takai N (2012) Built-out self-test circuit for digital signal timing. In: IEEJ technical meeting of electric circuits, ECT-12-069, Kumamoto

Hirabayashi D, Osawa Y, Harigai N, Kobayashi H, Kobayashi O, Niitsu K, Yamaguchi TJ, Takai N (2013) Phase noise measurement with sigma-delta TDC. In: IEEE international test conference, poster session, Anaheim

Ito S, Nishimura S, Kobayashi H, Uemori S, Tan Y, Takai N, Yamaguchi TJ, Niitsu K (2010) Stochastic TDC architecture with self-calibration. In: IEEE asia pacific conference on circuits and systems, Kuala Lumpur

Jee D-W, Seo Y-H, Park H-J, Sim J-Y (2011) A 2 GHz fractional-N digital PLL with 1b noise shaping ΔΣ TDC. In: IEEE VLSI circuit symposium, Kyoto

Kauffman JG, Witte P, Becker J, Ortmanns M (2011) An 8mW 50MS/s CT ΔΣ modulator with 81dB SFDR and digital background DAC linearization. In: IEEE international solid-state circuits conference, San Francisco

Kobayashi H, Yamaguchi TJ (2010) Digitally-assisted analog test technology - analog circuit test technology in nano-CMOS era. In: Technical report of IEICE. Integrated circuits and devices, Osaka

Moreira J, Werkmann H (2010) An Engineer’s guide to automated testing of high-speed interfaces. Artech House, Norwood

San H, Kobayashi H, Kawakami S, Kuroiwa N (2004) A noise-shaping algorithm of multi-bit DAC nonlinearities in complex bandpass ΔΣ AD modulators. IEICE Trans. Fundam E87-A(4):792–800

Silva J, Wang X, Kiss P, Moon U, Temes GC (2002) Digital techniques for improved ΔΣ data conversion. In: IEEE custom integrated circuits conference, San Jose

Schreier R, Temes G (2005) Understanding delta-sigma data converters. In: IEEE Press

Schreier R, Steensgaard J, Temes G (2002) Speed vs. dynamic range trade-off in oversampling data converters. In: Toumazou Ch, Moschytz G, Gilbert B (eds) Trade-offs in analog circuit design, chapt 22. Springer, New York

Yamauchi S, Watanabe T, Otsuka Y Japanese Patent, no. Toku-Kai-Hei 6-216721

Yin W, Inti R, Hanumolu PK (2010) A 1.6mW 1.6ps-rms-Jitter 2.5GHz digital PLL with 0.7-to-3.5GHz frequency range in 90nm CMOS. In: IEEE custom integrated circuits conference, San Jose

Young B, Sunwoo K, Elshazly A, Hanumolu PK (2010) A 2.4ps resolution 2.1mW second-order noise-shaped time-to-digital converter with 3.2ns range in 1MHz bandwidth. In: IEEE custom integrated circuits, San Jose

Acknowledgment

We acknowledge comments from K. Sato, S. Kawauchi, F. Abe, K. Sakuma and K. Wilkinson.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: M. Margala

Appendix: Improved Delay Measurement Circuit

Appendix: Improved Delay Measurement Circuit

This appendix shows an improved delay-value self-measurement circuit in Fig. 18, and we can use it when the rise delay time τ r and the fall delay time τ f of the delay cell are quite different.

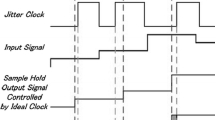

The oscillation frequency f o s c of the basic ring-oscillator configuration in Fig. 10 is a function of the buffer delay τ. Note that τ is the average of τ r and τ f (i.e., τ = (τ r + τ f ) / 2), where τ r is the delay when the buffer output rises from low to high level, and τ f is the one when it falls from high to low level. However, we need the value of τ r and we cannot measure it accurately with the ring oscillator in Fig. 10 when τ r and τ f are not equal.

The oscillation frequency of the improved circuit in Fig. 18a is only a function of τ r but is not a function of τ f . Figure 18b shows the timing chart of its signals for τ r < τ f . We have checked its operation with Spectre simulation.

By replacing one of the five buffers from node “a” to node “b” in Fig. 18a with the buffer in Fig. 5 whose rise delay τ r(m e a s u r e) should be measured, we can obtain the accurate value of τ r(m e a s u r e) by measuring the oscillation frequency.

Remark 3

Rights and permissions

About this article

Cite this article

Uemori, S., Ishii, M., Kobayashi, H. et al. Multi-bit Sigma-Delta TDC Architecture with Improved Linearity. J Electron Test 29, 879–892 (2013). https://doi.org/10.1007/s10836-013-5408-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-013-5408-6