Abstract

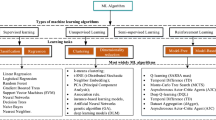

In order to learn the interconnect reliability of the complicated integrated circuit, a power amplifier 3D model is constructed and analyzed. The modeling and computation are completely automatic using the APDL. In order to predict the interconnect reliability of the power amplifier for the given design index effectively, the artificial neural networks model is used, then the prediction can be done fast. Training the simulation data from ANSYS, the neural network is used to model the relationship between the input and output. Then, a reliability database can be obtained which can help the designer to get the reliability performance of any design solution and the tradeoff decisions on the transistor’s size and the operation condition.

Similar content being viewed by others

References

Dalleau D, and Weide-Zaage K (2001) Three-dimensional voids simulation in chip metallization structures: a contribution to reliability evaluation. Microelectron Reliab 41 (9):1625–1630

Feng F, Chao C, Reddy G, Zhang QJ, Ma JG (2014) Parallel Space-Mapping Approach to EM Optimization. IEEE Trans Microwave Theory Tech 62(5):1135–1148

Fiks VB (1959) On the mechanism of the mobility of ions in metals. Soviet Physics-Solid State 1:14–28

Frost DF, Poole KF (1989) Reliant: a reliability analysis tool for VLSI interconnects. IEEE J Solid State Circuits 24(2):458–462

Guan Zhong, et al (2014) Atomic flux divergence based current conversion scheme for signal line electromigration reliability assessment, in Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC):2045–2056.

He FF (2012) 3D electro-migration modeling at circuit layout level, Ph.D dissertation, Nanyang Technol. Univ., Singapore

Hu CM (1992) BERT: an IC reliability simulator. Microelectron J 23(2):97–102

Kwong LE, Aun W (2005) A study in establishing flip-chip ball grid array (FCBGA) second level interconnect (SLI) reliability requirement by CFD simulation, in Proc Int Symp, EMAP:292–295.

Lee SY, Cetiner BA, Torpi H, Li J, Alt K, Wen CP (2001) An X-band gan hemt power amplifier design using an artificial neural network modeling technique. IEEE Trans Electron Devices 48(3):495–501

Lee M, Pramanik D, Yong-Seog O, and Qin ZD (2013) Determination of cu-line EM lifetime criteria using physically based TCAD simulations, in Proc. Reliability Physics Symposium, EM.4.1-EM.4.7

Li W, Tan CM, Raghavan N (2009) Dynamic simulation of void nucleation during electromigration in narrow integrated circuit interconnects. J Appl Phys 105(1): 014305-1–014305-7

Rajabalinejad M (2009) Reliability methods for finite element models. IOS Press, Amsterdam

Rayas-Sanchez JE (2004) EM-based optimization of microwave circuits using artificial neural networks: the state-of-the-art. IEEE Trans Microwave Theory Tech 52(1):42–435

Roy A, Tan CM (2006) Experimental investigation on the impact of stress free temperature on the electromigration performance of copper dual damascene submicron interconnect. Microelectron Reliab 46(9): 1652–1656

Rzepka S et al (1999) 3-D finite element simulator for migration effects due to various driving forces in interconnect lines, in Proc. fifth international workshop on stress induced phenomena in metallization: 877–890

Silvestre MR, Lee LL (2006) Statistical evaluation of pruning methods applied in hidden neurons of the mlp neural network. Lat Am Trans 4(4):249–256

Tan CM, Roy A (2006) Investigation of the effect of temperature and stress gradients on accelerated EM test for Cu narrow interconnects. Thin Solid Films 504(1):288–293

Tan CM, Roy A (2007) Electromigration in ULSI interconnects. Mater Sci Eng R Rep 58(1):1–75

Tan CM, Zhang G, Gan Z (2004) Dynamic study of the physical processes in the intrinsic line electromigration of deep-submicron copper and aluminum interconnects. IEEE Trans Device Mater Rel 4(3):450–456

Tan CM, Roy A, Vairagar AV, Krishnamoothy A, Mhaisalkar SG (2005) Current crowding effect on copper dual damascene via bottom failure for ULSI applications. IEEE Trans. Device Mater Rel 5(2):198–205

Tan CM, Hou YJ, Li W (2007) Revisit to the finite element modeling of electromigration for narrow interconnects. Appl Phys 102(3):033705–033707

Tian YZ, He FF, Zhang QJ, Tan CM, Ma JG (2014) Rapid ULSI interconnect reliability analysis using neural networks. IEEE Trans Device Mater Rel 14(1):400–407

Zhang QJ, Gupta KC (2000) Neural Networks for RF and Microwave Design. Artech House, Boston

Zhang QJ, Gupta KC, Devabhaktuni VK (2003) Artificial neural networks for RF and microwave design-from theory to practice. IEEE Trans Microwave Theory Tech 51(4):1339–1350

Zhong G, Marek-Sadowska M, Nassif S, Li BZ (2014) Atomic flux divergence based current conversion scheme for signal line electromigration in reliability assessment. Proc IITC/AMC: 245–248

Acknowledgments

This work was supported in part by the 863 Program of China (Contract No. 2015AA01A703), the Tianjin University-Qinghai University for Nationalities independent innovation fund cooperation project (2015), the international science and technology cooperation projects of Qinghai under Grant No. 2014-HZ-821 and the Chun Hui Project of Education Ministry( Z2015033).

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: Y. Makris

Rights and permissions

About this article

Cite this article

Lin, Q., Fu, H., He, F. et al. Interconnect Reliability Analysis for Power Amplifier Based on Artificial Neural Networks. J Electron Test 32, 481–489 (2016). https://doi.org/10.1007/s10836-016-5606-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-016-5606-0