Abstract

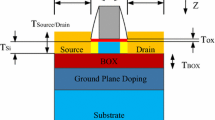

In this paper, a 65 nm MOSFET 3D structure is built based on Technology Computer Aided Design (TCAD) 3D device simulation software, and the single-event transient (SET) effect in 65 nm CMOS inverter is analyzed using TCAD-HSPICE mixed-mode simulation based on heavy ion model. The formation and function of the PN junction diffusion capacitance in the Metal-Oxide-Semiconductor (MOS) device are discussed by analyzing the drain and substrate voltage characteristics of the device under the SET effect. Then the sub-circuit structure of this device for SET is established, and the mechanism of the diffusion capacitance of PN junction during the heavy ion action process is verified comparing with the results of sub-circuit HSPICE simulation results and the TCAD-HSPICE simulation results. Finally, A sub-circuit model is provided, to support circuit-level simulation of single-event effects.

Similar content being viewed by others

References

Artola L, Gaillardin M, Hubert G, Raine M, Paillet P (2015) Modeling Single Event Transients in Advanced Devices and ICs. IEEE Trans Nucl Sci 62(4):1528–1539

Black DA, Robinson WH, Wilcox IZ, Limbrick DB, Black JD (2015) Modeling of Single Event Transients With Dual Double-Exponential Current Sources: Implications for Logic Cell Characterization. IEEE Trans Nucl Sci 62(4):1540–1549

Ferlet-Cavrois V, Massengill LW, Gouker P (2013) Single Event Transients in Digital CMOS—A Review. IEEE Trans Nucl Sci 60(3):1797–1790

GSEAT 1.9.0: User’s Guide (2017) Cogenda Pte Ltd. Su Zhou, China

He YB, Chen SM (2012) Impact of Circuit Placement on Single Event Transients in 65 nm Bulk CMOS Technology. IEEE Trans Nucl Sci 59(6):2772–2777

HSPICE Reference Manual: Elements and Device Models (2013) Synopsys. California, USA

HSPICE User Guide: Basic Simulation and Analysis (2013) Synopsys. California, USA

Kauppila JS, Massengill LW, Ball DR, Alles ML, Schrimpf RD, Loveless TD, Maharrey JA, Quinn RC, Rowe JD (2015) Geometry-Aware Single-Event Enabled Compact Models for Sub-50 nm Partially Depleted Silicon-on-Insulator Technologies. IEEE Trans Nucl Sci 62(4):1589–1598

Kerns SE, Massengill LW, Kerns DV, Alles ML, Houston TW, Lu H, Hite LR (1989) Model for CMOS/SOI Single-Event Vulnerability. IEEE Trans Nucl Sci 36(6):2305–2310

Laux SE, Hess K (1999) Revisiting the Analytic Theory of p-n Junction Impedance: Improvements Guided by Computer Simulation Leading to a New Equivalent Circuit. IEEE Trans Electron Devices 46(2):396–412

Liu Z, Chen SM, Liang B, Liu BW, Zhao ZY (2009) Research on bipolar effect in single-event transient. Acta Phys Sin 59(1):649–654

MacSweeney D, McCarthy KG, Mathewson A, Mason B (1998) A SPICE Compatible Subcircuit Model for Lateral Bipolar Transistors in a CMOS Process. IEEE Trans Electron Devices 45(9):1978–1984

VisualTCAD 1.7.2: VisualTCAD User’s Guide (2017) Cogenda Pte Ltd. Su Zhou, China

Wang H-B, Mahatme N, Chen L, Newton M, Li Y-Q, Liu R, Chen M, Bhuva BL, Lilja K, Wen S-J, Wong R, Fung R, Baeg S (2016) Single-Event Transient Sensitivity Evaluation of Clock Networks at 28-nm CMOS Technology. IEEE Trans Nucl Sci 63(1):385–391

Ziren L, Minxuan Z (2013) Research on SET and Charge Collection in Nano Integrate Circuits. Changsha China. Graduate School of National University of Defense Technology

Acknowledgment

This research was partially supported by Equipment Pre-research Project of China.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: V. D. Agrawal

Rights and permissions

About this article

Cite this article

Yi, T., Liu, Y. & Yang, Y. A Study of PN Junction Diffusion Capacitance of MOSFET in Presence of Single Event Transient. J Electron Test 33, 769–773 (2017). https://doi.org/10.1007/s10836-017-5694-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-017-5694-5