Abstract

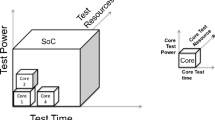

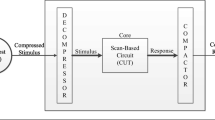

With increasing power density in modern integrated circuits, thermal issues are becoming a critical problem in System-on-a-Chip (SoC) testing. In this paper, we develop the thermal-aware test scheduling methods using Voltage/Frequency Scaling (VFS) and Test Partition (TP) to reduce the expensive Test Application Time (TAT). First, we develop a quick temperature estimation method in test scheduling to ensure the test temperature within the given range. Second, we propose a thermal-aware test scheduling method based on the mixed-integer linear programming model (MILP) (called STP-M) that applies VFS and TP to search the optimum scheduling and further reduce the TAT. Third, we develop a heuristic method based on Rectangular Strip Packing (called H-RSP) to quickly access the quasi-optimal scheduling. The experimental results on ITC’02 benchmarks showed that the STP-M obtains the most optimized result for every benchmark and saved 15.5% and 8.0% TAT on average compared with the existing works, while H-RSP takes less than 10 seconds to access the quasi-optimal scheduling that is close to that of STP-M.

Similar content being viewed by others

References

Aghaee N, Peng Z, Eles P (2013) Process-variation and temperature aware SoC test scheduling technique. J Electron Test 29(4):499–520

Aghaee N, Peng Z, Eles P (2015) A test-ordering based temperature-cycling acceleration technique for 3D stacked ICs. J Electron Test 31(5-6):503–523

Bild DR, Misra S, Chantemy T, Kumar P, Dick RP, Huy XS, Shangz L, Choudhary A (2008) Temperature-aware test scheduling for multiprocessor systems-on-chip. In: Proceedings of the 2008 IEEE/ACM International Conference on Computer-Aided Design, San Jose, USA, pp 59–66

Chakrabarty K (2000) Test scheduling for core-based systems using mixed-integer linear programming. IEEE Trans Comput-Aid Des Integr Circuit Syst 19(10):1163–1174

Chakrabarty K (2005) Low-cost modular testing and test resource partitioning for SOCs. In: Proceedings of IEEE Computers and Digital Techniques, vol 152, pp 427–441

Chou RM, Saluja KK, Agrawal VD (1997) Scheduling tests for VLSI systems under power constraints. IEEE Trans Very Large Scale Integr Syst 2:5

Gurobi Optimization Inc. (2013) Gurobi optimizer erence manual. http://www.gurobi.com, Accessed 15 Apr 2014

He Z, Peng Z, Eles P, Rosinger P, Al-Hashimi BM (2008) Thermal-aware SoC test scheduling with test set partitioning and interleaving. J Electron Test 24(1-3):247–257

Hu Y, Han Y, Li X, Li H, Wen X (2006) Compression/scan Co-design for reducing test data volume, scan-in power dissipation, and test application time. IEICE Trans 89-D(10):2616–2625

Iyengar V, Chakrabarty K, Marinissen EJ (2003) Test access mechanism optimization, test scheduling, and test data volume reduction for System-on-Chip. IEEE Trans Comput 12:52

Jiang L, Xu Q, Chakrabarty K (2012) Integrated test-architecture optimization and thermal-aware test scheduling for 3-D SoCs under pre-bond test-pin-count constraint. IEEE Trans Very Large Scale Integr Syst 20 (9):1621–1633

Khan O, Kundu S (2011) Microvisor: a runtime architecture for thermal management in chip multiprocessors. Trans High-Performance Embedded Architectures Compilers 4:84–110

Ling L, Jiang J (2014) Exploit Dynamic Voltage and Frequency Scaling for SoC Test Scheduling under Thermal Constraints. In: Proceedings of the 23rd IEEE Asian Test Symposium, Hangzhou, China, pp 180–185

Liu C, Veeraraghavan K, Iyengar V (2005) Thermal-aware test scheduling and hot spot temperature minimization for core-based system. In: Proceedings of IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, Monterey, USA, pp 552–560

Lofberg J (2004) YALMIP: a toolbox for modeling and optimization in MATLAB. In: Proceedings of CACSD Conference, Taipei, Taiwan. http://users.isy.liu.se/johanl/yalmip, Accessed 5 Apr 2014

Marinissen EJ, Iyengar V, Chakrabarty K (2002) A set of benchmarks for modular testing of SOCs. In: Proceedings of the 2002 IEEE International Test Conference Baltimore, USA, pp 519–528

Millican SK, Saluja KK (2012) Linear Programming Formulations for Thermal-Aware Test Scheduling of 3D-Stacked Integrated Circuits. In: Proceedings of IEEE Asian Test Symposium, Niigata, Japan, pp 37–42

Millican SK, Saluja KK (2013) 3D-IC Benchmarks. http://3dsocbench.ece.wisc.edu/, Accessed 20 Mar 2014

Millican SK, Saluja KK (2013) Formulating optimal test scheduling problem with dynamic voltage and frequency scaling. In: Proceedings of the 22nd Asian Test Symposium, Yilan County, Taiwan, pp 165–170

Millican SK, Saluja KK (2014) Optimal test scheduling formulation under power constraints with dynamic voltage and frequency scaling. J Electr Test Theory Appl 30(5):569–580

Millican SK, Saluja KK (2014) A test partitioning technique for scheduling tests for thermally constrained 3D integrated circuits. In: Proceedings of the 13th International Conference on VLSI Design and 27th International Conference on Embedded Systems, pp 20–25, Mumbai, India

Ravi S (2007) Power-aware test: challenges and solutions. In: Proceedings of 2007 IEEE International Test Conference, Santa Clara, USA, pp 1–10

Sheshadri V, Agrawal VD, Agrawal P (2013) Power-aware SoC test optimization through dynamic voltage and frequency scaling. In: Proceedings of 21st IFIP/IEEE International Conference on VLSI and SoC, Istanbul, Turkey, pp 102–107

Sheshadri V, Agrawal VD, Agrawal P (2017) Power-aware optimization of SoC test schedules using voltage and frequency scaling. J Electron Test Theory Appl 33(2):171–187

Shih CJ, Hsu CY, Kuo CY, Li J, Rau JC, Chakrabarty K (2012) Thermal-Aware Test Schedule and TAM Co-Optimization for ThreeDimensional IC. In: Proceedings of Active and Passive Electronic Components, pp 1–10

Skadron K, Stan MR, Huang W, Velusamy S, Sankaranarayanan K, Tarjan D (2003) Temperature-aware microarchitecture. ACM SIGARCH Comput Architecture News 31(2):2–13

Srinivasan S, Ganeshpure KP, Kundu SK (2012) A Wavelet-Based Spatio-Temporal Heat Dissipation Model for Reordering of Program Phases to Produce Temperature Extremes in a Chip. IEEE Trans Comput-Aid Des Integr Circuit Syst 31:12

Vartziotis F, Kavousianos X, Chakrabarty K, Jain A, Parekhji R (2015) Time-division multiplexing for testing DVFS-based SoCs. IEEE Trans Comput-Aid Des Integr Circuit Syst 4:34

Wen X, Yamashita Y, Kajihara S, Wang L, Saluja KK, Kinoshita K (2006) A new method for low-capture-power test generation for scan testing. IEICE Trans 89-D(5):1679–1686

Xia Y, Chrzanowska-Jeske M, Wang B, Jeske M (2003) Using a distributed rectangle bin-packing approach for core-based SoC test scheduling with power constraints. In: Proceedings of 2003 IEEE/ACM International Conference on Computer-Aided Design, San Jose, USA, p 100

Yao C, Saluja KK, Ramanathan P (2011) Power and thermal constrained test scheduling under deep submicron technologies. IEEE Trans Comput-Aid Des Integr Circuit Syst 30(2):317–322

Zhang Y, Peng Z, Jiang J, Li H, Fujita M (2015) Temperature-aware software-based self-testing for delay faults. In: Proceedings of Design Automation and Test Conference in Europe, Grenoble, France, pp 423–428

Acknowledgments

This paper is supported in part by National Natural Science Foundation of China (NSFC) under grant No. (61432017, 61502422, 61404092), in part by the Fundamental Research Funds for the Central Universities, and in part by Zhejiang Provincial Natural Science Foundation under grant No. (LY18F020028).

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: K. K. Saluja

Rights and permissions

About this article

Cite this article

Zhang, Y., Ling, L., Jiang, J. et al. Thermal-aware SoC Test Scheduling with Voltage/Frequency Scaling and Test Partition. J Electron Test 34, 447–460 (2018). https://doi.org/10.1007/s10836-018-5733-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-018-5733-x