Abstract

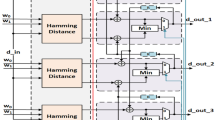

The Viterbi Algorithm is a recursive optimal solution for estimating the most likely state sequence of discrete-time finite-state Markov process and Hidden Markov Models (HMM) observed in memoryless noise. The Viterbi algorithm is extensively used for decoding convolutional codes, in the constraint length k that encompasses its use in digital communications specifically in satellite and cellular communications. Storage devices to speed up access, speech synthesis and recognition technologies use the Viterbi algorithm or its variants. In this paper low-power, high-speed and reduced transistor count Viterbi decoding circuits with enhanced error detection capabilities are designed and implemented with signature-based error detection schemes in three design logic styles primarily Conventional CMOS, Hybrid logic and GDI. The significance of the work is the upshot of realizing low latency and low power dissipation with high reliability in the iterative process of finding the least path metric by superseding the subtractor in CSA & PCSA circuits with an optimized comparator. When evaluated against the Traditional/Benchmark CSA & PCSA circuits, the Conventional CMOS design approach attains low power consumption and high accuracy with a reduction in average power dissipation by 4.69% and 3.83% and an improvement in delay performance by 7.89% and 3.79% respectively, with a tradeoff for high area utilization. Whereas, the GDI design approach results in an extreme reduction of transistor count by 71.52% and 74.94% with a weaker logic swing for CSA & PCSA units respectively, complimented by an increase in power dissipation (approximately multiplied by a factor of 5) and deterioration in delay performance by one order of magnitude. The Hybrid logic stages CSA & PCSA units that are 32.52% and 9.27% faster and achieve optimization in area utilization by 48.68% and 51.09% respectively, at the expense of elevated power dissipation by one order of magnitude. All the circuits were designed and simulated using GPDK 90 nm technology libraries on Cadence Design Suite 6.1.6 platform at 27 °C temperature on 1.2 V supply-rail and SPICE codes were generated as well.

Similar content being viewed by others

References

“Viterbi Algorithm for Decoding of Convolutional Codes.” Internet: https://web.archive.org/web/20130807043539/http:/www.1-core.com/library/comm/viterbi, 2009 [May. 8, 2019]

Viterbi AJ (2006) A personal history of the Viterbi algorithm. IEEE Signal Process Mag 23(4):120–142

Yueksel H et al. (2018) Design techniques for high-speed multi-level Viterbi detectors and trellis-coded-modulation decoders, in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, no. 10, pp. 3529–3542

Suganya GS, Kavya G (2013) RTL design and VLSI implementation of an efficient convolutional encoder and adaptive Viterbi decoder, in Proc. International Conference on Communication and Signal Processing, Melmaruvathur, pp. 494–498

Mozaffari Kermani M, Singh V, Azarderakhsh R (2017) Reliable low-latency Viterbi algorithm architectures benchmarked on ASIC and FPGA, IEEE Transactions on Circuits and Systems I: Regular Papers 64(1):208–216

Lember J, Gasbarra D, Koloydenko A, Kuljus K (2019) Estimation of Viterbi path in Bayesian hidden Markov models. Metron: rivista internazionale di statistica 77(2):137–169

MIT Lecture notes. “Viterbi Decoding of Convolutional codes, Lecture 9.” Internet: http://web.mit.edu/6.02/www/f2010/handouts/lectures/L9.pdf, 2010, accessed June 11, 2019

Boo M, Arguello F, Bruguera JD, Doallo R, Zapata EL (1997) High-performance VLSI architecture for the viterbi algorithm. IEEE Trans Commun 45(2):168–176

Ramadass U, Dhavachelvan P (2012) Modified Gate Diffusion Input Technique: A New Technique for Enhancing Performance in Full Adder Circuits. Procedia Technology 6:74–81

Kamuf M, Owall V, Anderson JB (2007) Survivor path processing in Viterbi decoders using register exchange and Traceforward, IEEE Transactions on Circuits and Systems II: Express Briefs 54(6):537–541

Dawid H, Fettweis G, Meyr H (1996) A CMOS IC for Gb/s Viterbi decoding: system design and VLSI implementation, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 4(1):17–31

Habib I, Paker Ö, Sawitzki S (2010) Design space exploration of hard-decision Viterbi decoding: algorithm and VLSI implementation, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 18(5):794–807

Kubota S, Kato S, Ishitani T (1993) Novel Viterbi decoder VLSI implementation and its performance, IEEE Transactions on Communications, 41(8):1170–1178

He J, Liu H, Wang Z, Huang X, Zhang K (2012) High-speed low-power Viterbi decoder design for TCM decoders, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 20(4):755–759

Putra RVW, Adiono T (2014) A configurable and low complexity hard-decision viterbi decoder in VLSI architecture, in Proc.2nd International Conference on Information and Communication Technology, ICoICT, pp. 182–186

Morgenshtein A, Fish A, Wagner IA (2002) Gate-diffusion input (GDI): a power-efficient method for digital combinatorial circuits, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 10(5):566–581

Tirumalasetty VR, Machupalli MR (2019) Design and analysis of low power high-speed 1-bit full adder cells for VLSI applications. Int J Electron 106(4):521–536

Rabaey JM. Digital Integrated Circuits: A Design Perspective, Chapter 6, Designing Combinational Logic gates in CMOS. [On-line]. Available: http://bwrcs.eecs.berkeley.edu/Classes/icdesign/ee141_f01/Notes/chapter6.pdf, accessed January 26, 2020

Smitha GS, Ravish Aradhya HV (2019) mGDI based parallel adder for low power applications. Microsyst Technol 25(5):1653–1658

Morgenshtein A, Fish A, Wagner IA (2002) Gate-diffusion input (GDI) - a technique for low power design of digital circuits: analysis and characterization, in Proc.IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA

“Three transistors (3T) based logic gates.” Chapter 5. https://shodhganga.inflibnet.ac.in/bitstream/10603/39870/10/10_chapter5.pdf. Accessed 30 Jan 2020

Bhowal S. (2013) Transformation of ACS module to CSA module of low-power Viterbi decoder for digital wireless communication applications, in Proc.International Conference on Advances in Computing, Communications and Informatics (ICACCI), Mysore, pp. 266–270

“Power estimation and Analysis,” UNIT - 3. http://gvpcew.ac.in/LN-CSE-IT-22-32/ECE/4-Year/Low-power-VLSI-unit-3.pdf. Accessed 29 Jan 2020

Kumar V, Singh A, Upadhyay S, Kumar B (2019) Power-delay-error-efficient approximate adder for error-resilient applications. Journal of Circuits, Systems and Computers 28(10):1–14

Shieh S-H, and Lee MI (2010) Totally Self-Checking Carry-Select Adder Design Based on Two-Rail Code. https://www.semanticscholar.org/. Accessed 10 Apr 2019

Muthulaxmi S (2015) Detection of fault in self-checking carry select adder. International Journal of Electronics and Communication Engineering 8(2):99–106

Das SR et al. (2003) Parity bit signature in response data compaction and built-in self-testing of VLSI circuits with nonexhaustive test sets, IEEE Transactions on Instrumentation and Measurement 52(5):1363–1380

Sentiyes O “Design of VLSI Integrated Circuits, A (very) deep dive into processors.” http://people.rennes.inria.fr/Olivier.Sentieys/presentations/ARCHI17_VLSI_Sentieys.pdf. Accessed 31 Jan 2020

Belgacem H, Chiraz K, Rached O (2011) Pass Transistor Based Self-Checking Full Adder, International Journal of Computer Theory and Engineering 3(5):608–616

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of Interest

The authors declare that they have no conflict of interest.

Additional information

Responsible Editor: B. Ghavami

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Varada, S., Katpally, S. & Thiruveedhi, S.S.L. Comprehensive Analysis and Optimization of Reliable Viterbi Decoder Circuits Implemented in Modular VLSI Design Logic Styles. J Electron Test 36, 343–363 (2020). https://doi.org/10.1007/s10836-020-05882-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-020-05882-5