Abstract

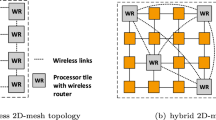

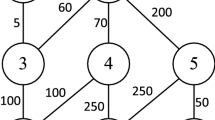

Based on the recent research, the communication cost has been the most important open issue in network on chip (NoC). In other words, the lower the communication cost, the better the performance of the NoC and the lower the energy consumption. In this regard, although different mapping algorithms are proposed, they could not efficiently address some important challenges such as high complexity, early convergence at the local optimum, and performing well for all task graphs. The proposed method named IAM (IWO algorithm mapping) is an enhanced 2D-mesh-based-NoC mapping method which adapts the invasive weed optimization (IWO) algorithm, in order to efficiently map the IP cores to routers. The obtained results indicate that the communication cost improved 13, 9, 8, 4, and 4 percent in comparison with the LMAP, the CASTNET, the CLUSTER, the NMAP, and the PSO algorithm, respectively. Regarding energy consumption, IAM outperforms the NMAP, the CASTNET, and the CMAP and the Onyx algorithms by providing 15, 10, 7, and 7 percent improvement in energy consumption, respectively. Max delay was reduced by 11, 4, 5, and 5 percent compared to NMAP, CASTNET, CMAP, and Onyx algorithms, respectively. Throughput was improved by 9, 9, 4, and 10 percent compared to NMAP, CASTNET, CMAP, and Onyx algorithms, respectively.

Similar content being viewed by others

References

Frankel, D.S.: Model Driven Architecture: Applying MDA to Enterprise Computing. Wiley, Hoboken (2003)

Bennini, L., DeMicheli, G.: Networks on chip: a new paradigm for system on chip design. Des. Autom. Test Europe 35, 70–78 (2002)

Jamali, M., Khademzadeh, A.: MinRoot and CMesh: interconnection architectures for network-on-chip systems. World Acad. Sci. Eng. Technol. 54, 349–354 (2009)

Kumar, S., Jantsch, A., Sonioen, J.P., Forsell, M., Millberg, M., Oeberg, J., Tiensirja, K., Hemani, A.: A network on chip architecture and design methodology. In: IEEE Computer Society Annual Symposium on VLSI, pp. 105–114 (2002)

Tosun, S., Ozturk, O., Ozen, M.: An ILP formulation for application mapping onto network-on-chips. In: 3rd International Conference on Application of Information and Communication Technologies, AICT2009, Baku (2009)

Liu, J., Zheng, W., Li, W., Wang, X., Xie, Y., Wen, X.: Distributed uplink power control for two-tier femtocell networks via convex pricing. In: IEEE Wireless Communication Network Conference (WCNC), Shanghai, China, pp. 458–463 (2013)

Tsiropoulou, E.E., Vamvakas, P., Papavassiliou, S.: Joint customized price & power for energy efficient multi-service wireless networks via S-modular theory. IEEE Trans. Green Commun. Netw. 1(1), 17–28 (2017)

Murali, S., Micheli, G.De.: Bandwidth constrained mapping of cores onto NoC architectures. Proc. Des. Autom. Test Europe Conf. Exhib. 2(3), 896–901 (2004)

Shen, T., Chao, C.H., Lien, Y.K., Wu, A.Y.: A new binomial mapping and optimization algorithm for reduced-complexity mesh-based on-chip network. In: International Symposium on Networks-on-Chip, IEEE (NOCS’07), pp. 317–322 (2007)

Mehran, A., Saeidi, S., Khademzadeh, A., Afzali-Kusha, A.: Spiral: a heuristic mapping algorithm for network on chip. Electron. Express 4(15), 478–484 (2007)

Janidarmian, M., Khademzadeh, A., Tavanpour, M.: Onyx: a heuristic bandwidth-constrained mapping of cores onto tile-based network on chip. Electron. Express 6(1), 1–7 (2009)

Saeidi, S., Khademzadeh, A., Vardi, F.: Crinkle: a heuristic mapping algorithm for network on chip. Electron. Express 6(24), 1737–1744 (2009)

Chan, Y., Xie, L., Li, J.: An energy-aware heuristic constructive mapping algorithm for network on chip. In: International Conference on ASIC (ASICON), pp. 101–104 (2009)

Moein-Darbati, F., Khademzadeh, A., Gharooni-Fard, G.: CGMAP: a new approach to network-on-chip mapping problem. Electron. Express 6(1), 27–34 (2009)

Tavanpour, M., Khademzadeh, A., Pourkiani, S., Yaghobi, M.: GBMAP: an evolutionary approach to mapping cores onto a mesh-based NoC architecture. J. Commun. Comput. 7(3), 1–7 (2010)

Kumar, P.: A survey on application mapping strategies for Network on chip design. J. Syst. Archit. 54, 60–76 (2013)

Rashedi, M., Khademzadeh, A., Reza, A.: Elixir: a new bandwidth-constrained mapping for networks-on-chip. Electron. Express 7(2), 73–79 (2010)

Sahu, P.K., Venkatesh, P., Gollapalli, S., Chattopadhyay, S.: Application mapping onto mesh structured network-on-chip using particle swarm optimization. In: IEEE International Symposium on VLSI (ISVLSI), pp. 335–336 (2011)

Tosun, S.: New heuristic algorithms for energy aware application mapping and routing on mesh-based NoCs. J. Syst. Archit. 57(2), 69–78 (2011)

Tosun, S.: Cluster-based application mapping method for network-on-chip. Adv. Eng. Softw. 42(5), 868–875 (2011)

Maqsood, T.: Dynamic task mapping for network on chip based systems. J. Syst. Archit. 61(7), 293–306 (2015)

Alagarsamy, A., Gopalakrishnan, L.: SAT: a new application mapping method for power optimization in 2-D NoC. In: 2016 20th International Symposium on VLSI Design and Test (VDAT), pp. 1-6. IEEE (2016)

Xie, Y., Liu, Y.: A research on NoC mapping with quantum ant colony algorithm. In: 2017 International Conference on Wireless Communication, Signal Processing and Networking (WISPNET), pp. 874–877. IEEE (2017)

Huang, L., Chen, S., Wu, Q., Ebrahimi, M., Wang, J., Jiang, S., Li, Q.: A lifetime-aware mapping algorithm to extend MTTF of networks-on-chip. In: Proceedings of the 23rd Asia and South Pacific Design Automation Conference, pp. 147–152. IEEE Press (2018)

Sonavane, R., Kashyap, S.G., Chattopadhyay, S.: Thermal aware application mapping and frequency scaling for mesh-based network on chip design. In: IEEE International Symposium on Smart Electronic System (iSES) (2018)

Fang, J., Zong, H., Zhao, H.: DI_GA: a heuristic mapping algorithm for heterogeneous network on chip. In: Proceedings of the IOP Conference: Materials Science and Engineering, Hubei, China, 19–20 April 2019, vol. 490 (2019)

Wang, J., Li, Y., Chai, S., Peng, Q.: Band width-aware application mapping for NOC-based MPSoCs. J. Comput. Inf. Syst. 7, 152–159 (2011)

Mehrabian, A.R., Lucas, C.: A novel numerical optimization algorithm inspired from weed colonization. Ecol. Inform. 1(4), 355–366 (2006)

Srinivasan, K., Chatha, K.S., Konjevod, G.: Linear-programming-based techniques for synthesis of network-on-chip architectures. IEEE Trans. Very Large Scale Integr. Syst. 14(4), 407–420 (2006)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Mazaheri Kalahroudi, P., Yaghoubi, E. & Barekatain, B. IAM: an improved mapping on a 2-D network on chip to reduce communication cost and energy consumption. Photon Netw Commun 41, 78–92 (2021). https://doi.org/10.1007/s11107-020-00911-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11107-020-00911-x