Abstract

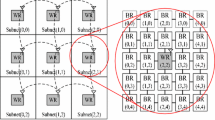

In this paper, we have developed analytical stochastic communication technique for inter and intra-Networks-on-Chip (NoC) communication. It not only separates the computation and communication in Networks-in-Package (NiP) but also predicts the communication performance. Moreover, it will help in tracking of the lost data packets and their exact location during the communication. Further, the proposed technique helps in building the Closed Donor Controlled Based Compartmental Model, which helps in building Stochastic Model of NoC and NiP. This model helps in computing the transition probabilities, latency, and data flow from one IP to other IP in a NoC and among NoCs in NiP. From the simulation results, it is observed that the transient and steady state response of transition probabilities give state of data flow latencies among the different IPs in NoC and among the compartments of NoCs in NiP. Furthermore, the proposed technique produces low latency as compared to the latencies being produced by the existing topologies.

Similar content being viewed by others

References

Kangmin L, Se-Joong L, Donghyun K, Kwanho K, Gawon K, Joungho K, Hoi-Jun Y (2005) Networks-on-chip and networks-in-package for high-performance SoC platforms. In: Proceedings of international conference on Asian solid-state circuits, pp 485–488

Kangmin L, Se-Joong L, Hoi-Jun Y (2006) Low-power network-on-chip for high-performance SoC design. IEEE Trans Very Large Scale Integr Syst 14(2):148–160

Dumitras TA (2003) On-chip stochastic communication. Masters Thesis, Department of Electrical and Computer Engineering Carnegie Mellon University, Pittsburgh, Pennsylvania, 2003

Nitin, Sehgal VK, (2007) Stochastic communication on application specific networks on chip. Springer, Berlin, pp 11–16, ISBN 978-1-4020-6265-0

Nitin, Chauhan DS, Sehgal VK (2008) Two O(n 2) time fault-tolerant parallel algorithm for inter NoC communication in NiP. Springer, Berlin, pp 267–282, ISBN 978-3-540-79186-7, Invited

Nitin, Sehgal VK, Chauhan DS (2008) A new approach for inter networks-on-chip communication in networks-in-package. In: Proceedings of the 6th international conference on embedded systems and applications, pp 16–23

Nitin, Sharma R, Sehgal VK, Mehta R, Sethi P., Gupta E. (2009) Asymptotic analysis of dynamic algorithms designed to provide parallel communication among NoC in NiP using MIN. In: Proc 11th international conference on computer modeling and simulation, pp 443–448

Kim K, Lee S-J, Lee K, Yoo H-J ? An arbitration look-ahead scheme for reducing end-to-end latency in networks on chip. In: Proc IEEE international symposium on circuits and systems, 2005, pp 2357–2360

Murali S, Micheli G (2004) SUNMAP: a tool for automatic topology selection and generation for NoCs. In: Proceedings of design automation conference, pp 914–919

Bjerregaard T, Mahadevan S (2006) A survey of research and practices of network-on-chip. ACM Comput Surv 38(1):1–51

Madl G, Pasricha S, Dutt ND, Abdelwahed S (2009) Cross-abstraction functional verification and performance analysis of chip multiprocessor designs. IEEE Trans Indust Inform 5(3):241–256

Gajski D, Dutt ND, Wu A, Lin S (1992) High level synthesis: introduction to chip and system design. Kluwer Academic, Norwell, ISBN: 978-0-7923-9194-4

Pasricha S, Dutt ND (2008) On-chip communication architectures. Kauffman, Los Altos, ISBN: 978-0-12-373892-9

Bogdan P, Marculescu R (2006) A theoretical framework for on-chip stochastic communication analysis. In: Proceedings of 1st international conference on nano-networks, pp 1–5

Bogdan P, Dumitras TA, Marculescu R (2007) Stochastic communication: a new paradigm for fault-tolerant networks-on-chip, VLSI Des, pp 1–17. doi:10.1155/2007/95348

Sgroi M, Sheets M, Mihal A, Keutzer K, Malik S, Rabaey J, Vincentelli AS (2001) Addressing the system-on-a-chip interconnect woes through communication-based design. In: Proceedings of the 38th annual ACM IEEE conference on design automation conference, pp 667–672

Benini L, De Micheli G (2002) Networks-on-chips: a new SoC paradigm. IEEE Comput 35(1):70–78

Benini L, De Micheli G (2006) Networks-on-chips: technology and tools. Kaufmann, San Francisco, ISBN: 978-0-12-370521-1

Jayasimha DN, Zafar B, Hoskote Y (2006) On-chip interconnection networks: why they are different and how to compare them, Intel Corporation, pp 1–11

Inwood B (1986) Goal and target in stoicism. J Philos 83(10):547–556

Asmussen S, Glynn PW (2007) Stochastic simulation: algorithms and analysis. Springer, Berlin, ISBN: 978-0-387-30679-7

Duato J, Yalamanchili S, Ni LM (2003) Interconnection networks: an engineering approach. Kaufmann, San Francisco, ISBN: 1-55860-852-4

Dally WJ, Towles B (2004) Principles and practices of interconnection networks. Kaufmann, San Francisco, ISBN: 978-0-12-200751-4

Nitin, Subramanian A (2008) Efficient algorithms to solve dynamic MINs stability problems using stable matching with complete ties. J Discrete Algorithms 6(3):353–380

Nitin, Sehgal VK, Sharma N, Krishna K, Bhatia A (2007) Path-length and routing-tag algorithm for hybrid irregular multi-stage interconnection networks. In: Proceedings of the 8th ACIS international conference on software engineering, artificial intelligence, networking, and parallel/distributed computing, pp 652–657

Nitin, Sehgal VK, Bansal PK (2007) On MTTF analysis of a fault-tolerant hybrid MINs. WSEAS Trans Comput Res 2(2):130–138 ISSN: 1991-8755

Nitin (2006) Component level reliability analysis of fault-tolerant hybrid MINs. WSEAS Trans Comput 5(9):1851–1859 ISSN: 1109-2750

Nitin (2006) Reliability analysis of multi-path multi-stage interconnection network. In: Proceedings of the 10th WSEAS international conference on circuits, systems, communication and computers, pp 1018–1023

Nitin (2006) On analytic bounds of regular and irregular fault-tolerant multi-stage interconnection networks. In: Proceedings of the international conference on parallel and distributed processing techniques and applications, pp 221–226

Nitin, Subramanian A (2006) On reliability analysis of cost-effective hybrid zeta network: a fault-tolerant multi-stage interconnection network. In: Proceedings of the international conference on parallel and distributed processing techniques and applications, pp 260–265

Subramanian A, Nitin (2004) On a performance of multistage interconnection network. In: Proceedings of the 12th international conference on advanced computing and communication, pp 73–79

Nitin, Garhwal S, Srivastava N (2009) Designing a fault-tolerant fully-chained combining switches multi-stage interconnection network with disjoint paths, J. Supercomput, doi:10.1007/s11227-009-0336-z, pp 1–32

Nitin, Chauhan DS (2010) Comparative analysis of traffic patterns on k-ary n-tree using adaptive algorithms based on burton normal form, J Supercomput, doi:10.1007/s11227-010-0454-7, pp 1–20

Walter GG, Contreras M (1999) Compartmental modeling with networks. Birkhauser, Boston, ISBN: 0-8176-4019-3

Ladde GS (1976) Cellular systems-II. stability of compartmental systems. Math Biosci 30:1–21

Jacquez JA, Simon CP (2002) Qualitative theory of compartmental systems with lags. Math Biosci 180:329–362

Sandberg IW (1978) On the mathematical foundations of compartmental analysis in biology, medicine, and ecology. IEEE Trans Circuits Syst 25(5):273–279

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Nitin, Chauhan, D.S. Stochastic communication for application-specific Networks-on-Chip. J Supercomput 59, 779–810 (2012). https://doi.org/10.1007/s11227-010-0472-5

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-010-0472-5