Abstract

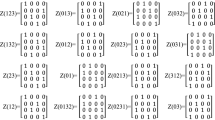

Quaternary encoded binary circuits are more compact than their binary counterpart. Although quaternary reversible circuits are realizable, design of such circuits is still in its infancy. This work proposes a new, enhanced method of quaternary Galois field sum of products (QGFSOP) synthesis for quaternary quantum circuits. To reduce QGFSOP product terms, the algorithm makes use of 11 newly defined quaternary Galois field (QGF) expansions (for a total of 21 QGF expansions). This algorithm achieves QGFSOP minimization with the assistance of a pseudo-Kronecker Galois field decision diagram (QGFDD). This is a novel approach for QGFSOP synthesis. Finally, QGFSOP expressions are translated into quantum cost optimized quaternary quantum circuits using: (1) newly developed quaternary quantum gate realizations of controlled Feynman and Toffoli gate that are optimized in terms of quantum cost, (2) use of composite literals consisting of 1 digit and M–S gates. Performance evaluation against existing works in the literature determined that our proposed method achieves an average QGFSOP expression product term savings of 32.66 %. Also, the synthesized QGFSOP circuits were evaluated in terms of quantum cost.

Similar content being viewed by others

References

Frost-Murphy SE ,Ottavi M, Frank MP, DeBenedictis EP (2006) On the design of reversible qdca systems. Technical report, Sandia National Laboratories

Ren J, Semenov VK (2011) Progress with physically and logically reversible superconducting digital circuits. IEEE Trans Appl Supercond 21(3):780–786

Vos AD, Rentergem YV (2005) Power consumption in reversible logic addressed by a ramp voltage. In: Proc. 15th Intl. Workshop on Power and Timing Modeling, Optimization and Simulation, Lecture Notes in Computer Science, vol 3728, pp 207–216

Nielsen M, Chuang I (2000) Quantum computation and quantum information. Cambridge University Press, Cambridge

Wille R, Drechsler R (2009) BDD-based synthesis of reversible logic for large functions. In: Proc. 46th ACM/IEEE Design Automation Conf. (DAC ’09), pp 270–275

Mochizuki A, Shirahama H, Hanyu T (2014) Design of a quaternary single-ended current-mode circuit for an energy-efficient inter-chip asynchronous communication link. In: Proc. 44th IEEE International Symposium on Multiple-Valued Logic (ISMVL), pp 67–72

Onizawa N, Hanyu T, Gaudet VC (2009) High-throughput bit-serial LDPC decoder LSI based on multiple-valued asynchronous interleaving. IEICE Trans Electron E92–C(6):867–874

Patel KSV, Gurumurthy KS (2010) Arithmetic operations in multi-valued logic. arXiv:1003.5442

Sasao T, Nakahara H, Matsuura M, Kawamura Y, Butler JT (2009) A quaternary decision diagram machine and the optimization of its code. In: 39th International Symposium on Multiple-Valued Logic (ISMVL 2009), pp 362–369

Okamoto K, Homma N, Aoki T (2014) Formal design of arithmetic circuits over galois fields based on normal basis representations. IEICE Trans 97–D(9):2270–2277

Homma N, Saito K, Aoki T (2012) Formal design of multiple-valued arithmetic algorithms over Galois fields and its application to cryptographic processor. ISMVL, Victoria, pp 110–115

Feinstein DY, Thornton MA (2015) Quantum multiple-valued decision diagrams containing skipped variables. J Multi Valued Logic Soft Comput 24(1–4):93–108

Liang J, Chen L, Han J, Lombardi F (2014) Design and evaluation of multiple valued logic gates using pseudo N-type carbon nanotube FETs. IEEE Trans Nanotechnol 13(4):695–708

Muthukrishnan A, Stroud CR Jr (2000) Multivalued logic gates for quantum computation. Phys Rev A 62(5):052309/1-8

Meena JK, Lal C, Gupta H, Jain SC (2015) Low cost realization of square and square multiplication operations using toffoli gates. Green Computing and Internet of Things (ICGCIoT), International Conference on, Noida, pp 1304–1308

Khan MHA, Siddika NK, Perkowski MA (2008) Minimization of quaternary Galois field sum of products expression for multi-output quaternary logic function using quaternary Galois field decision diagram. In: Proc. Intl. Symp. Multiple-Valued Logic, pp 125–130

Mandal SB, Chakrabarti A, Sur-Kolay S (2012) A synthesis method for quaternary quantum logic circuits, in Progress in VLSI Design and Test. LNCS 7373:270–280

Khan MMM, Biswas AK, Chowdhury S, Tanzid M, Mohsin KM, Hasan M, Kahn AI (2008) Quantum realization of some quaternary circuits. In: Proc. 2008 IEEE Region 10 Conference, pp 1–5

Khan MHA (2007) Reversible realization of quaternary decoder, multiplexer, and demultiplexer circuits. Eng Lett 15(2):203–207

Yang S (2014) Logic synthesis and optimization benchmarks users guide version 3.0. http://citeseerx.ist.psu.edu/viewdoc/download;jsessionid=7D8CF3ACF680A3BD7D10E6CCA602CABA?doi=10.1.1.49.591&rep=rep1&type=pdf. Accessed on 06 August 2014

Deb A, Das DK, Sur-Kolay S (2013) Modular design for symmetric functions using quantum quaternary logic. In: Proc. 5th Intl. Symp. Electronic System Design (ISED)

Meena JK, Jain SC, Gupta H, Gupta S (2015) Synthesis of balanced quaternary reversible logic circuit. In: Circuit, Power and Computing Technologies (ICCPCT), International Conference on, Nagercoil, pp 1–6

Khan MHA, Perkowski MA (2007) GF(4) based synthesis of quaternary reversible/quantum logic circuits. J Multiple Valued Logic Soft Comput 13:583–603

Sarabi A, Ho PF, Iravani K, Daasch WR, Perkowski MA (1993) Minimal multi-level realization of switching functions based on Kronecker functional decision diagrams. In: Proc. IEEE Intl. Workshop Logic Synthesis, pp P3a-1-6

Khan MHA, Perkowski MA, Khan MR (2005) Ternary GFSOP minimization using Kronecker decision diagrams and their synthesis with quantum cascades. J Multi Valued Logic Soft Comput 11:567–602

Jayashree H, Thapliyal H, Arabnia HR, Agrawal V (2016) Ancilla-input and garbage-output optimized design of a reversible quantum integer multiplier. J Supercomput 72(4):1477–1493

Thapliyal H, Jayashree HV, Nagamani AN, Arabnia HR (2013) Progress in reversible processor design: a novel methodology for reversible carry look-ahead adder. Springer Trans Comput Sci 7420:73–97

Thapliyal H, Arabnia HR, Srinivas MB (2009) Efficient reversible logic design of BCD subtractors. In: Springer Transactions on Computational Sciences Journal, LNCS 5300, vol 3, pp 99–121

Bocharov A, Roetteler M, Svore KM (2016) Factoring with Qutrits: Shor’s Algorithm on Ternary and Metaplectic Quantum Architectures. arXiv:1605.02756

Sharifi F, Moaiyeri MH, Navi K, Bagherzadeh N (2016) Ultra-low-power carbon nanotube FET-based quaternary logic gates, Taylor and Francis. Int J Electron 103(9):1524–1537

Sharifi F, Moaiyeri MH, Navi K, Bagherzadeh N (2015) Quaternary full adder cells based on carbon nanotube FETs. J Comput Electron 14(3):762–772

Moaiyeri MH, Navi K, Hashemipour O (2012) Design and evaluation of CNFET-based quaternary circuits. Springer Circuits Syst Signal Process 31(5):1631–1652

Kotiyal S, Thapliyal H, Ranganathan N (2010) Design of a ternary barrel shifter using multiple-valued reversible logic. In: Proceedings of the 10th IEEE International Conference on Nanotechnology (IEEE NANO). Seoul, Korea, pp 1104–1108

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Khan, M.H.A., Thapliyal, H. & Munoz-Coreas, E. Automatic synthesis of quaternary quantum circuits. J Supercomput 73, 1733–1759 (2017). https://doi.org/10.1007/s11227-016-1878-5

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-016-1878-5