Abstract

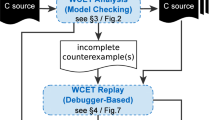

Real-time critical systems can be considered as correct if they compute both right and fast enough. Functionality aspects (computing right) can be addressed using high level design methods, such as the synchronous approach that provides languages, compilers and verification tools. Real-time aspects (computing fast enough) can be addressed with static timing analysis, that aims at discovering safe bounds on the worst-case execution time (WCET) of the binary code. In this paper, we aim at improving the estimated WCET in the case where the binary code comes from a high-level synchronous design. The key idea is that some high-level functional properties may imply that some execution paths of the binary code are actually infeasible, and thus, can be removed from the worst-case candidates. In order to automatize the method, we show (1) how to trace semantic information between the high-level design and the executable code, (2) how to use a model-checker to prove infeasibility of some execution paths, and (3) how to integrate such infeasibility information into an existing timing analysis framework. Based on a realistic example, we show that there is a large possible improvement for a reasonable computation time overhead.

Similar content being viewed by others

Notes

In the binary code, 27 “if then else” patterns appearing in sequence are controlled by only 6 high-level conditions ; the impact in the number of paths is \(2^6\) when taking into account the trivial exclusions, while it was \(2^{27}\) without this information: the gain is a factor of \(2^{21} = 2.097.152\).

References

Andalam S, Roop P, Girault A (2011) Pruning Infeasible Paths for Tight WCRT Analysis of Synchronous Programs. In: International Conference on Design, Automation and Test in Europe (DATE 2011)

Asavoae M, Maiza C, Raymond P (2013) Program Semantics in Model-Based WCET Analysis: A State of the Art Perspective. In: 13th International Workshop on Worst-Case Execution Time Analysis (WCET 2013), pp 31–40

Béchennec JL, Cassez F (2011) Computation of WCET using Program Slicing and Real-Time Model-Checking. The Computing Research Repository (CoRR) abs/1105.1633

Berry G, Gonthier G (1992) The Esterel synchronous programming language: design, semantics, implementation. Sci Comput Program (SCP) 19(2):87–152

Blazy S, Maroneze A, Pichardie D (2013) Formal Verification of Loop Bound Estimation for WCET Analysis. VSTTE - Verified Software: Theories, Tools and Experiments, Springer 8164:281–303

Boldt M, Traulsen C, von Hanxleden R (2008) Worst case reaction time analysis of concurrent reactive programs. Electron Notes Theor Comput Sci (ENTCS) 203(4):65–79

Caspi P, Raymond P, Tripakis S (2007) Synchronous programming. In: Lee I, Leung JYT, Son SH (eds) Handbook of real-time amd embedded systems, Chapman and Hall/CRC, Chap 14

Dalsgaard A, Olesen M, Toft M, Hansen R, Larsen K (2010) METAMOC: Modular Execution Time Analysis using Model Checking. In: 10th International Workshop on Worst-Case Execution Time Analysis (WCET 2010), pp 113–123

Engblom J, Ermedahl A, Altenbernd P (1998) Facilitating worst-case execution time analysis for optimized code. In: Euromicro Conference on Real-Time Systems (ECRTS)

Falk H, Lokuciejewski P, Theiling H (2006) Design of a WCET-Aware C Compiler. In: 6th International Workshop on Worst-Case Execution Time Analysis (WCET 2006)

Ferdinand C, Heckmann R, Sergent TL, Lopes D, Martin B, Fornari X, Martin F (2008) Combining a high-level design tool for safety-critical systems with a tool for WCET analysis on executables. In: International Conference on Embedded Real-Time Software and Systems (ERTS2)

Gauthier T, Guernic PL, Besnard L (1987) Signal, a declarative language for synchronous programming of real-time systems. In: Proc. 3rd. Conference on Functional Programming Languages and Computer Architecture, LNCS 274, Springer

Gustafsson J, Ermedahl A, Sandberg C, Lisper B (2006) Automatic Derivation of Loop Bounds and Infeasible Paths for WCET Analysis Using Abstract Execution. In: IEEE Real-Time Systems Symposium (RTSS)

Halbwachs N (1993) Synchronous programming of reactive systems. Kluwer Academic Publishers, Dordrecht

Halbwachs N, Raymond P, Ratel C (1991) Generating Efficient Code From Data-Flow Programs. In: 3rd International Symposium on Programming Language Implementation and Logic Programming (PLILP), pp 207–218

Ju L, Huynh BK, Roychoudhury A, Chakraborty S (2008) Performance debugging of Esterel specifications. In: International Conference on Hardware Software Codesign and System Synthesis (CODES-ISSS)

Ju L, Huynh BK, Chakraborty S, Roychoudhury A (2009) Context-sensitive timing analysis of Esterel programs. In: Proceedings of the 46th Annual Design Automation Conference (DAC 09), pp 870–873

Kirner R, Lang R, Freiberger G, Puschner P (2002) Fully Automatic Worst-Case Execution Time Analysis for Matlab/Simulink Models. In: Euromicro Conference on Real-Time Systems (ECRTS)

Kirner R, Puschner P, Prantl A (2010) Transforming flow information during code optimization for timing analysis. J Real-Time Syst 45(1—-2):72–105

Knoop J, Kovács L, Zwirchmayr J (2013) WCET squeezing: on-demand feasibility refinement for proven precise WCET-bounds. In: 21st International Conference on Real-Time Networks and Systems (RTNS 2013), pp 161–170

Metzner A (2004) Why Model Checking Can Improve WCET Analysis. In: 16th International Conference on Computer Aided Verification (CAV 2004), pp 334–347

Raymond P (2008) Synchronous Program Verification with Lustre/Lesar. In: Mertz S, Navet N (eds) Modeling and Verification of Real-Time Systems, ISTE/Wiley, Chap. 6

Raymond P (2014) A General Approach for Expressing Infeasibility in Implicit Path Enumeration Technique. In: International Conference on Embedded Software (EMSOFT)

Ringler T (2000) Static Worst-Case Execution Time Analysis of Synchronous Programs. In: Proceedings of the 5th Ada-Europe International Conference on Reliable Software Technologies, pp 56–68

Tan L, Wachter B, Lucas P, Wilhelm R (2009) Improving Timing Analysis for Matlab Simulink/Stateflow. In: 2nd International Workshop on Model Based Architecting and Construction of Embedded Systems (ACES-MB)

Wang JJ, Roop PS, Andalam S (2013) ILPc: A novel approach for scalable timing analysis of synchronous programs. In: International Conference on Compilers, Architectures, and Synthesis for Embedded Systems (CASES 2013), pp 1–10

Wilhelm R, Engblom J, Ermedahl A, Holsti N, Thesing S, Whalley D, Bernat G, Ferdinand C, Heckmann R, Mitra T, Mueller F, Puaut I, Puschner P, Staschulat J, Stenström P (2008) The worst-case execution-time problem-overview of methods and survey of tools. ACM Trans Embed Comput Syst (TECS) 7(3):1–53

Acknowledgments

This work is supported by the french research fundation (ANR) as part of the W-SEPT Project (ANR-12-INSE-0001).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Raymond, P., Maiza, C., Parent-Vigouroux, C. et al. Timing analysis enhancement for synchronous program. Real-Time Syst 51, 192–220 (2015). https://doi.org/10.1007/s11241-015-9219-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11241-015-9219-y