Abstract

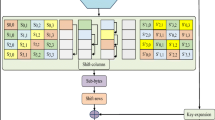

In this paper we propose novel high-speed and low-power architecture for the context formation sub-block in tier-1 block of JPEG2000 system. The proposed architecture is inspired from the statistical analysis results on 20 test images, each one 512*512 pixels, gray scale with 8 bit pixels. The proposed architecture incorporates a check unit to detect unnecessary operations in both pass1 and pass2 of the EBCOT block. For code block size of 64*64 bits, the timing and power consumption analysis show that the proposed architecture reduces the power consumption about 20.64% and increases the processing speed to about 33.67% with respect to the speedy reference architecture. The proposed architecture has a processing speed close to the parallel mode architectures with almost the same area for serial mode architectures and more power saving. The proposed architecture gathers the basic advantages of the serial and parallel mode implementations in addition to lower power consumption.

Similar content being viewed by others

References

K.-F. Chen, C.-Jr Lian, and H.-H. Chen, and L.-G. Chen, “Analysis and Architecture Design of EBCOT for JPEG-2000,” In Proceedings of the 9th International Symposium on Integrated Circuits, Devices and Systems (ISIC-2001), Singapore, 2001, pp. 497–500.

Y. Li, R.E. Aly, B. Wilson, and M.A. Bayoumi, “Analysis and Enhancement for EBCOT in High speed JPEG2000 Architectures,” MWSCAS 2002, Ok, July-2002.

C. Christopoulos, et. al., “JPEG-2000 Verification Model 7.0 (Technical Description),” ISO/IEC JTC 1/SC 29/WG 1 N 1684, Apr 2000.

J. Chiang, Y. Lin, and C. Hsieh, “Efficient Pass-Parallel Architecture for EBOCT in JPEG2000,” IEEE ISCAS-2002.

D. Chai and A. Bouzerdoum, “JPEG2000 image compression: an overview,” Seventh Australian Intelligent Information Systems Conference, 2001, pp. 237–241.

A. Shams, T. Darwish and M.A. Bayoumi, “Performance Analysis of 1 bit Cmos Full Adder Cell,” IEEE Trans. on VLSI, Feb. 2002.

David Taubman, “High Performance Scalable Image Compression with EBCOT,” Proc. of IEEE International Conference on Image Processing, Kobe, Japan, 1999, vol.3. pp. 344–348

D. Taubman, “EBCOT: Embedded Block Coding with Optimized Truncation,” ISO/IEC JTC1/SC29/WG1 N1020R.

JPEG2000 Final Committee Draft (FCD) (http://www.jpeg.org/JPEG2000.htm).

M. Rabbani and R. Joshi, “An Overview of the JPEG 2000 still image compressing standard,” Signal Processing: Image Communication 17, 2002, pp. 3–48.

J. Rabaey et al., “Digital Integrated Circuits: A Design Perspective,” 2nd edition, Prentice-Hall 2002.

Y. Li, R.E. Aly, M.A. Bayoumi, and S. Mashali, “Parallel High-Speed Architecture for EBCOT in JPEG2000,” IEEE International Conference on Acoustics, Speech, and Signal Processing, vol. 2, 2003, pp. 481–484.

Author information

Authors and Affiliations

Corresponding author

Additional information

Ramy E. Aly received the B.S. degree in electrical engineering from University of Alexandria, Egypt, in 1994, and the M.S. degree in electrical engineering from Old Dominion University, VA, in 2001 and M.S. in computer engineering from University of Louisiana at Lafayette, in 2002. He is currently working toward his Ph.D. degree at the Center for Advanced Computer Studies (CACS), University of Louisiana, Lafayette. Since 2001, he has been a Research Assistant with the CACS, in the VLSI Research group of M. A. Bayoumi, University of Louisiana. His research interests include low-power VLSI circuit design, low-power SRAM design, JPEG2000 Architecture and CAD-tools.

Magdy A. Bayoumi(S'80-M'84-SM'87-F'99) received the B.Sc. and M.Sc. degrees in electrical engineering from Cairo University, Cairo, Egypt, in 1973 and 1977, the M.Sc. degree in computer engineering from Washington University in St. Louis, MO, in 1981, and the Ph.D. degree in electrical engineering from the University of Windsor, Windsor, ON, Canada, in 1984. Currently, he is the Director of the Center for Advanced Computer Studies (CACS), Department Head of the Computer Science Department, the Edmiston Professor of Computer Engineering, and the Lamson Professor of Computer Science at The Center for Advanced Computer Studies, University of Louisiana at Lafayette, where he has been a Faculty Member since 1985. He has edited and coedited three books in the area of VLSI Signal Processing. He has one patent pending. His research interests include VLSI design methods and architectures, low-power circuits and systems, digital signal processing architectures, parallel algorithm design, computer arithmetic, image and video signal processing, neural networks, and wide-band network architectures. Dr. Bayoumi received the University of Louisiana at Lafayette 1988 Researcher of the Year Award and the 1993 Distinguished Professor Award. He was an Associate Editor of the IEEE CIRCUITS AND DEVICES MAGAZINE, the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, the IEEE TRANSACTIONS ON NEURAL NETWORKS, and the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: ANALOG AND DIGITAL SIGNAL PROCESSING. He was an Associate Editor of the Circuits and Devices Magazine and is currently an Associate Editor of Integration, the VLSI Journal, and the Journal of VLSI Signal Processing Systems. He is a Regional Editor for the VLSI Design Journal and on the Advisory Board of the Journal on Microelectronics Systems Integration. From 1991 to 1994, he served on the Distinguished Visitors Program for the IEEE Computer Society, and he is on the Distinguished Lecture Program of the Circuits and Systems Society. He was the Vice President for technical activities of the IEEE Circuits and Systems Society. He was the Cochairman of the Workshop on Computer Architecture for Machine Perception in 1993, and is a Member of the Steering Committee of this workshop. He was the General Chairman of the 1994 MWSCAS and is a Member of the Steering Committee of this symposium. He was the General Chairman for the 8th Great Lake Symposium on VLSI in 1998. He has been on the Technical Program Committee for ISCAS for several years and he was the Publication Chair for ISCAS'99. He was also the General Chairman of the 2000 Workshop on Signal Processing Design and Implementation. He was a founding member of the VLSI Systems and Applications Technical Committee and was its Chairman. He is currently the Chairman of the Technical Committee on Circuits and Systems for Communication and the Technical Committee on Signal Processing Design and Implementation. He is a Member of the Neural Network and the Multimedia Technology Technical Committees. Currently, he is the faculty advisor for the IEEE Computer Student Chapter at the University of Louisiana at Lafayette.

Rights and permissions

About this article

Cite this article

Aly, R.E., Bayoumi, M. High-Speed and Low-Power IP for Embedded Block Coding with Optimized Truncation (EBCOT) Sub-Block in JPEG2000 System Implementation. J VLSI Sign Process Syst Sign Image Video Technol 42, 139–148 (2006). https://doi.org/10.1007/s11265-005-4179-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-005-4179-4